Умножитель частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике, радиотехнике и вычислительной технике. Целью изобретения является уменьшение затрат оборудования. Это достигается введением источника 4 напряжения, делителя 9 напряжения, резистора 12 и второго триггера 1 в устройство, содержащее элемент И 5, первый триггер 6, два ключа 3 и 7, интегратор 8, управляемый генератор 13 и делитель 14 частоты. 2 ил. FBbiyi (Л со 00 ел со (Г) 1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ1335997

А1 (5ц 4 G 06 F 7/68

AL д ) п1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

Floe

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4054147/24-24 (22) 14.04.86 (46) 07.09.87. Бюл. № 33 (71) Ивановский энергетический институт им. В. И. Ленина (72) М. В. Фалеев, P. М. Трахтенберг, А. Н. Ширяев и В. П. Аполенский (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 744569, кл. Н 03 В 19/00, G 06 F 7/68, 1977.

Авторское свидетельство СССР № 420082, кл. Н 03 В 19/00, G 06 G 7/16, 1971. (54) УМНОЖИТЕЛЬ ЧАСТОТЫ (57) Изобретение относится к автоматике, радиотехнике и вычислительной технике.

Целью изобретения является уменьшение затрат оборудования. Это достигается введением источника 4 напряжения, делителя 9 напряжения, резистора 12 и второго триггера

1 в устройство, содержащее элемент И 5, первый триггер 6, два ключа 3 и 7, интегратор 8, управляемый генератор !3 и делитель 14 частоты. 2 ил.

1335997

Изобретение относится к автоматике, радиотехнике и вычислительной технике и может быть использовано в устройствах, требующих повышения частоты электрических сигналов.

Цель изобретения — уменьшение затрат оборудования.

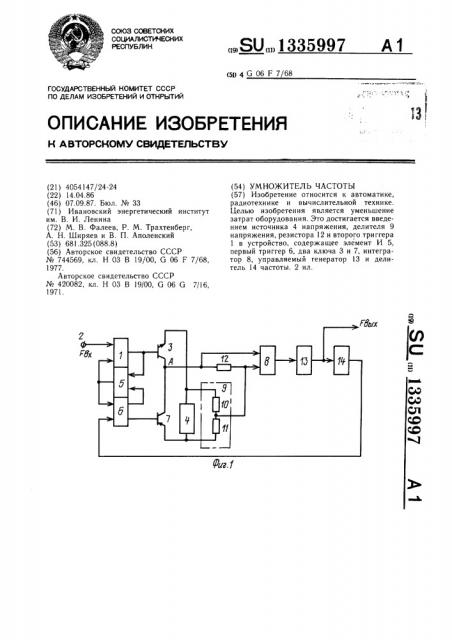

На фиг. 1 представлена функциональная схема умножителя частоты; на фиг. 2 — временные диаграммы работы элементов умножителя.

Умножитель частоты содержит второй триггер 1, вход 2 умножителя, и-р-и транзистор 3, источник 4 питания, элемент И 5, первый триггер 6, р-п-р транзистор 7, интегратор 8, делитель 9, напряжения, состоящий из резисторов 10 и 11, резистор

12, управляемый генератор 13 и делитель

14 частоты.

Умножитель частоты работает следующим образом.

В исходном состоянии на выходе триггера 1 и прямом выходе триггера 6 присутствуют нулевые потенциалы. После прихода импульса частоты Fax с выхода 2 на выходе триггера 1 устанавливается положительный потенциал, который открывает транзистор 3. При этом инвертирующий вход интегратора 8 через открытый транзистор 3 подключается к первому выходу источника

4 питания. Напряжение на неинвертирующем входе интегратора 8 в этом случае определяется следующим образом

Us= U4 Rio/(Rio+ Rii), (1) где Us — напряжение на неинвертирующем входе интегратора 8;

U4 — напряжение на выходе источника 4 питания;

Rio, R

Так как напряжение на инвертирующем

Н входе интегратора 8 Us близко к нулю, поскольку открыт транзистор 3, 1- 8 ) 1- 8 (2) откуда следует, что производная выходного напряжения интегратора 8 положительна.

Следовательно, напряжение на выходе интегратора 8 начинает возрастать, что приводит к увеличению частоты на выходе управляемого генератора 13 и появлению импульса обратной связи fia на выходе делителя

14 частоты.

Импульс обратной связи устанавливает на прямом выходе триггера 6 положительный потенциал. При этом на выходе элемента также появляется положительный потенциал, который, поступая на входы сброса триггеров 1 и 6, приводит к появлению на их прямых выходах нулевого потенциала и закрыванию транзистора 3. Транзистор 7 остается также закрытым, так как на инверсном выходе триггера 6 присутствует положительный потенциал. Напряжение на инвертирующем входе интегратора 8 в этом случае определяется по формуле

1-18= 1-18 1У R12 (3) где I — ток утечки интегратора 8;

R I — величина сопротивления резистора 12.

Поскольку величина I, для интеграторов, построенных на базе операционных усилителей, мала и составляет 10 и 10 мкА, можно считать, что 1 Ri2 ((Us, а следовательно, 1- 8 = Us (4) т.е. напряжения на входах интегратора

8 равны и его выходной сигнал остается постоянным.

После прихода следующего импульса частоты Fax имеют место аналогичные процессы. Очевидно, что в квазиустановившемся режиме работы напряжение на выходе интегратора 8 должно оставаться постоянным, что возможно только в том случае, когда импульсы частот Р" и fi4 приходят одновременно, т.е. эти частоты равны между собой, а фазовый сдвиг последовательностей импульсов и выходных импульсов делителя

14 равен нулю. Поскольку делитель 14 частоты не вносит погрешности в положение выходных импульсов относительно входных, можно считать, что импульсы входной частоты Fax и управляемого генератора 13 синфазны.

Неидеальность характеристик используемых элементов, например дрейф интегратора и конечные величины токов утечки по его входам, приводит к тому, что в течение периода частоты F- напряжение на выходе интегратора изменяется, например уменьшается. При этом уменьшается частота импульсов управляемого генератора 13 и импульс с выхода делителя 14 задерживается относительно импульса частоты F--. Появление импульса частоты Fax, как показано выше, приводит к увеличению напряжения на выходе интегратора 8. Этот процесс продолжается до момента прихода импульса частоты

fi4. Величина фазового сдвига импульсов частот Fax и fi4 автоматически устанавливается такой, чтобы скомпенсировать изменение напряжения на выходе интегратора 8 в течение периода частоты F x. Временные диаграммы, соответствующие этому режиму работы устройства, представлены на фиг. 2 (участок 1).

При увеличении напряжения на выходе интегратора 8 в течение периода частоты

Fsx (фиг. 2, участок II) частота сигнала управляемого генератора 13 также увеличивается и импульс обратной связи с выхода делителя 14 приходит раньше импульса частоты I=. При этом на инверсном выходе триггера 6 устанавливается нулевой потенциал и транзистор 7 открывается. На инвертирующем входе интегратора 8 устанавливается напряжение, близкое по величине к напряжению источника 4 питания. Так как в этом случае Us (Us, напряжение на выходе интегратора 8 начинает уменьшаться.

1335997 0иг. 2

Составитель Н. Маркелова

Редактор П. Гереши Техред И. Верес Корректор М. Демчик

Заказ 3803/44 Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий ! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Этот процесс происходит до появления импульса частоты Р-, которыЙ устанавливает на инверсном выходе триггера 6 положительный потенциал, закрывающий транзистор 7. Таким образом, и в этом случае частоты сигналов управляемого генератора

13 и делителя частоты 14 изменяются в необходимую сторону до тех пор, пока величина фазового рассогласования импульсов частот Р- и fi4 не станет равной нулю.

При резком изменении, например увеличении, частоты Г- на инверсный вход интегратора 8 поступает широтно-импульсный сигнал с выхода триггера 1 через транзистор 3, увеличивая напряжение на выходе интегратора 8 и частоту сигнала управляемого генератора 13.

Формула изобретения

Умножитель частоты, содержащий делитель частоты, интегратор, управляемый генератор, первый триггер, элемент И и два ключа, причем выход интегратора соединен с входом управляемого генератора, выход которого является выходом умножителя, выход делителя частоты соединен с синхровходом первого триггера, прямой выход которого соединен с первым входом элемента И, отличающийся тем, что, с целью уменьшения затрат оборудования, в умножитель введены второй триггер, источник напряже5 ния, делитель напряжения и резистор, первый и второй ключи выполнены в виде п-р-и и р — n — р-транзисторов соответственно, при этом вход умножителя соединен с синхровходом второго триггера, вход сброса которого соединен с входом сброса первого триггера и с выходом элемента И, второй вход которого соединен с выходом второго триггера и базой п — р — n-транзистора, эмиттер которого соединен с выходом нулевого потенциала источника напряжения и с первым

15 входом делителя напряжения, второй вход которого соединен с выходом положительного потенциала источника напряжения и эмиттером р — n — p-транзистора, база которого соединена с инверсным выходом пер20 вого триггера, коллекторы и — р — и- и р — n — р-транзисторов соединены с инверсным входом интегратора и через резисторы— с прямым входом интегратора и выходом делителя напряжения, выход управляемого генератора соединен с входом делителя частоты.