Многовходовый сигнатурный анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и наладки систем передачи и обработки информации. Целью изобретения является расширение функциональных возможностей анализатора за счет обеспечения возможности анализа логических состояний в системах с повторной передачей сбойных ситуаций. Анализатор содержит первую группу из п триггеров 1-1,... 1-п, первый сумматор 2 по модулю два, группу из (п-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3-1,...,3-(п-1), блок 4 индикации , группу информационных входов 5-1,..., 5-п синхровход 6, вторую группу из п триггеров 7-1,...,7-п, второй сумматор 8 по модулю два, элемент И 9, элемент 10 задержки, вход 11 сброса. Анализатор обеспечивает свертку входной информации с одновременной ее проверкой на нечетность. В случае четности входной информации (при сбойной ситуации) свертка приостанавливается до получения от системы повторной правильной информации. 1 ил. S (Л 5-1 ) со со Oi

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (594 G06F 11 16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АBTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4053868/24-24 (22) 09.04.86 (46) 07.09.87. Бюл. № 33 (72) А. Н. Тарасенко, Г. М. Львов, О. Н. Дяченко, А. И. Уткин, А. А. Коновалов и Н. Л. Антипова (53) 681.3 (088.8) (56) Авторское свидетельство СССР № 1048475, кл. G 06 F 11/00, 1982.

Авторское свидетельство СССР № 858210, кл. Н 03 К 21/34, 1979. (54) МНОГОВХОДОВЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР (57) Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и наладки систем передачи и обработки информации. Целью изобретения является расширение функцио„„Su„„ ЗЗВО О А1 нальных возможностей анализатора за счет обеспечения возможности анализа логических состояний в системах с повторной передачей сбойных ситуаций. Анализатор содержит первую группу из п триггеров 1-1,...

1-п, первый сумматор 2 по модулю два, группу из (и — 1) элементов ИСКЛЮЧАЮШЕЕ ИЛИ 3 — 1,...,3-(п — 1), блок 4 индикации, группу информационных входов 5-1,..., 5-п синхровход 6, вторую группу из и триггеров 7-1,...,7-п, второй сумматор 8 по модулю два, элемент И 9, элемент 10 задержки, вход 11 сброса. Анализатор обеспечивает свертку входной информации с одновременной ее проверкой на нечетность. В случае четности входной информации (при сбойной ситуации) свертка приостанавливается до Я получения от системы повторной правильной информации. 1 ил.

1336010

Формула изобретения

Многовходовый сигнатурный анализатор, содержащий первую группу из л триггеров, где и — число информационных входов анализатора, первый сумматор по модулю два, группу из и — I элементов ИСКЛЮЧАЮЩЕЕ

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и наладки систем передачи и обработки информации.

Цель изобретения — расширение функциональных возможностей анализатора за счет обеспечения возможности анализа логических состояний в системах с повторной передачей сбойных ситуаций.

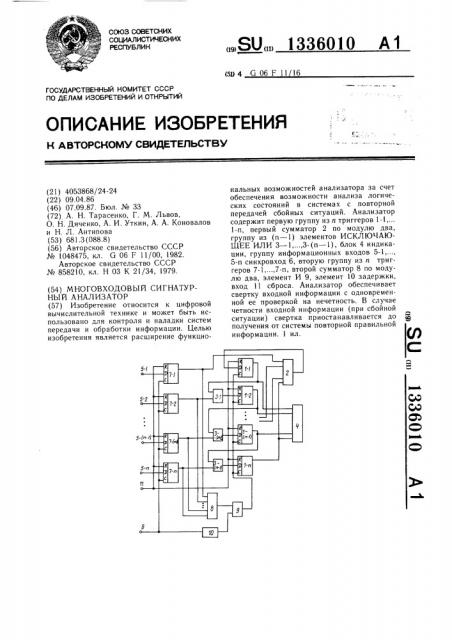

На чертеже представлена функциональная схема анализатора.

Анализатор содержит первую группу из п триггеров 1-1,...,1-п, первый сумматор 2 по модулю два, группу из (п-1) элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ 3-1,,3- (n — 1), блок 4 индикации, группу информационных входов 5-1,...,5-п, синхровход 6, вторую группу из п триггеров 7-1,...,7-п, второй сумматор 8 по модулю два, элемент И 9, элемент 10 задержки, вход 11 сброса.

Анализатор работает следующим образом.

Перед началом работы его входы 5-1,..., 5-п подключаются к выходным шинам контролируемой цифровой системы. Обычно количество входов анализатора. п соответствует количеству выходных шин контролируемой системы. Если появляются неиспользуемые входы анализатора, они подключаются к шине логического «О». Синхровход 6 подключается к выходу источника тактовых импульсов проверяемой системы. Многовходовый параллельный сигнатурный регистр представляет собой регистр сдвига с линейной обратной связью через первый сумматор 2 по модулю два, на входы которого (кроме первого входа) поступают выходы триггеров, определяемые порождающим полиномом обратных связей.

Информация, поступающая на вход каждого триггера первой группы, является результатом суммирования по модулю два логических состояний, поступающих с выходов триггеров 7-1,...,7-п второй группы, и логического состояния предыдущего триггера первой группы. Таким образом, при поступлении синхроимпульсов на синхровходы триггеров первой группы обеспечивается сворачивание в сигнатуру логических состояний, поступающих с выходов триггеров второй группы.

При поступлении сигнала на вход 11 сброса анализатора устанавливаются в нулевое состояние триггеры 1-1,...,1-п первой группы и триггеры 7-1,...,7-п второй группы.

Запуск анализатора осуществляется началом подачи синхроимпульсов на вход 6 анализатора. Они поступают с входа 6 на синхровходы триггеров 7-1,...,7-п второй группы и через элемент 10 задержки на второй вход элемента И 9. При поступлении синхроимпульса на триггерах 7-1,...,7-п второй группы фиксируются логические сигналы с входов 5-1,,5-п. Принятый код исследуемой последовательности с выходов триггеров 7-1, 5

50...,7-и второй группы анализируется на нечетность с помощью второго сумматора 8 по модулю два.

Если входной код оказывается четным, что при контроле на нечетность соответствует одиночной случайной ошибке (сбой) в исследуемой последовательности, проверяемая цифровая система передачи и обработки информации фиксирует сбойную ситуацию и обеспечивает повторную передачу соответ ствующего кода. В этом случае через элемент И 9 запрещается прохождение задержанного синхроимпульса на синхровходы триггеров 1-1,...,1-п первой группы. Таким образом, сбойная информация с выходов триггеров 7-1,...,7-н группы не сворачивается в сигнатуру на многовходовом сигнатурном регистре.

Если принятый на триггеры 7-1,...,7-п второй группы код оказывается нечетным, единичный логический сигнал с выхода второго сумматора 8 по модулю два разрешает прохождение через элемент И 9 синхроимпульса, задержанного элементом 10 задержки на время записи информации в триггеры

7-1,...7п второй группы и срабатывания второго сумматора 8 по модулю два.

По задержанному синхроимпульсу инфор мация с выходов триггеров 7-1,...,7-п второй группы сворачивается в сигнатуру на многовходовом сигнатурном регистре путем сложения по модулю два на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 3-1,...,3- (и — 1) и первом сумматоре 2 по модулю два с логическим состоянием предыдущих разрядов триггеров первой группы. Сворачивание последовательности исследуемых входных наборов логических состояний в сигнатуру на многовходовом сигнатурном регистре будет происходить до тех пор, пока на входе

6 присутствует последовательность синхроимпульсов, после окончания которой завершается исследование входной последовательности логических состояний.

По окончании цикла проверки на триггерах первой группы содержит некоторое число (сигнатура), отражающее в сжатой форме содержание выходной информации проверяемой системы. Суждение о правильности работы проверяемой системы передачи и обработки информации может быть вынесено оператором путем сравнения высвеченного на блоке 4 индикации числа с контрольным числом, записанным в технической документации на проверяемое изделие и полученным ранее, например, при проверке заведомо исправного такого же устройства.

1336010

Составитель С. Старчихин

Редактор П. Гереши Техред И. Верес Корректор С. Черни

Заказ 3803/44 Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 7К вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 з

ИЛИ и блок индикации, причем входы первого сумматора по модулю два с второго по (и — 1)-й подключены к единичным выходам соответствующих триггеров первой группы, в том числе и последнего триггера первой группы, в соответствии с видом образующего полинома, выход первого сумматора по модулю два соединен с информационным входом первого триггера первой группы, единичный выход каждого предыдущего триггера первой группы подключен к первому входу соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход каждого из которых соединен с информационным входом последующего триггера первой группы, входы блока индикации соединены с выходами триггеров первой группы, входы сброса которых объединены и подключены к входу сброса анализатора, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения возможности анализа логических состояний в системах с повторной передачей сбойных ситуаций, он содержит дополнительно вторую группу из и триггеров, второй сумматор по модулю два, элемент

И и элемент задержки, причем единичный выход первого триггера второй группы подключен к первым входам первого и второго сумматоров по модулю два, единичные выходы остальных триггеров второй группы подключены к вторым входам соответствующих элементов ИСКЛЮЧАЮШЕЕ ИЛИ и к соответствующим входам второго сумматора по модулю два, выход которого соединен с первым входом элемента И, второй вход которого подключен к выходу элемента задержки, выход элемента И подключен к синхровходам триггеров первой группы, информационные входы триггеров второй группы образуют группу информационных входов анализатора, входы сброса триггеров второй группы объединены и подключены к входу сброса анализатора, синхровходы триггеров второй группы соединены с входом элемен20 та задержки и подключены к синхровходу анализатора.