Микропроцессор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к микропроцессорным системам с микропрограммным управлением , п может быть использовано в устройствах обработки телевизионного изображения . Целью изобретения является повы- 1пение производительности микропроцессора. С этой целью в микропроцессор, содержащий первый блок 3 памяти, регистр 1 микрокоманд и операционный блок 5, введены второй блок 4 памяти и блок 2 син.хронизации и формирования признаков, условий, содержащий регистр условий, мультиплексор условий, включающий дешифратор, группу элементов И п элемент ПЛИ, элементы И и элементы НЕ.7 ил. бнеш (Л СО оо 05 о ГчЭ ОО

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„1ЗЗ602З (51) 4 G 06 F 15 00

t

) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

Я

Н. УС дн

Р г 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3882079/24-24 (22) 08.04.85 (46) 07.09.87. Бюл. ¹ 33 (72) Г. В. Галкин, Л. Д. Минутин и О. О. Попов (53) 681.325 (088.8) (56) Березенко А. И., Корягин Л. Н., Назарьян А. Р. Микропроцессорные комплекты повышенного быстродействия. Мл Радио и связь, 1981, с. 84 — 88, рис. 49 б.

Там же, с. 84 — 86, рис. 49 а. (54) МИКРОПРОЦECCOP (57) Изобретение относится к вычислительной технике, в частности к микропроцессорным системам с микропрограммным управлением, и может быть использовано в устройствах обработки телевизионного изображения. Целью изобретения является повышение производительности микропроцессора.

С этой целью в микропроцессор, содержащий первый î1ок 3 памяти, регистр 1 микрокоманд и операционный блок 5, введены второй блок 4 памяти и блок 2 синхронизации и формирования признаков, условий, содержащий регистр условий. мультиплексор условий, включающий дешифратор, группу элементов И и элем I T ИЛИ, элементы И и элементы HF.7 ил.

1336023

Изобретение относится к вычислительной технике, а в частности к микропроцессорным системам с микропрограммным управлением, и может быть использовано в устройствах обработки телевизионного изображения.

Целью изобретения является повышение производительности микропроцессора.

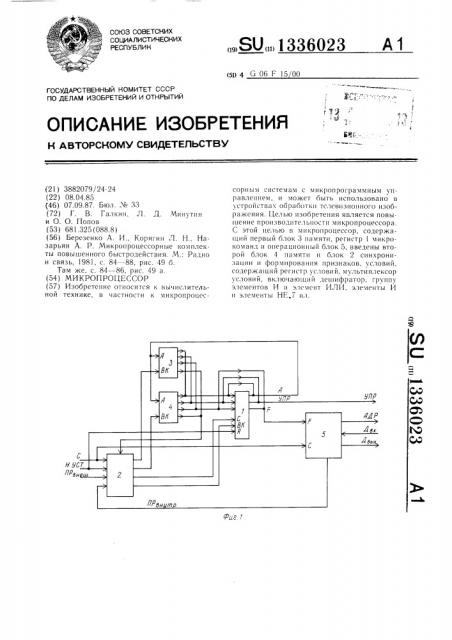

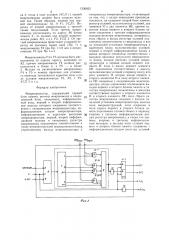

На фиг. 1 представлена функциональная схема микропроцессора; на фиг. 2 схема блока синхронизаци и обработки признаков; на фиг. 3 — алгоритмы функционирования микропроцессора; на фиг. 4 алгоритм взаимодействия блоков памяти и микрокоманд регистра; на фиг. 5 и 6 блок-схемы программы и распределения микрокоманд в блоках памяти соответственно; на фиг. 7 — операционный блок.

Микропроцессор содержит (фиг. 1) регистр 1 микрокоманд, блок 2 синхронизации и формирвания признаков условий, блоки 3 и 4 памяти и операционный блок 5.

Блок 2 содержит (фиг. 2) регистр 6 условий, мультиплексор условий, включающий дешифратор 7, группу элементов И 8.1,..., 8.п и элемент ИЛИ 9, а также первый элемент HE 10, элементы И 11.1 и 11.2 и второй элемент HE 12.

Операционный блок 5 содержит (фиг. 7) восемь операционных элементов 13.1, ..., 13.8, схему 14 ускоренного переноса и дешифратор 15. Элементы 13 могут быть выполнены в виде микросхем К 589ИК02, а схема 14— в виде микросхемы К 589ИКОЗ.

Микропроцессор работает следующим образом.

Для выборки первой микрокоманды программы на вход начальной установки микропроцессора подается импульс, который обнуляет регистр 1, а также устанавливает в начальное состояние блок 2. В результате на адресные входы первого и второго блоков памяти (блоки 3 и 4 соответственно) поступает нулевой код с регистра 1, а на управляющие входы блоков 3 и 4 поступают соответственно логические «О» и «1» с первого и второго выходов блока 2, т.е. разрешающий сигнал поступает на блок 4.

Таким образом, первая микрокоманда программы должна размещаться по нулевому адресу блока 4. Ограничений на адреса остальных микрокоманд нет, за исключением требования размещать две микрокоманды, следующие за условным переходом, по одному и тому же адресу в блоках

3 и 4. После появления первой микрокоманды параллельно начинаются три процесса: выборка следующей микрокоманды по адресу, определяемому кодом адресного поля первой микрокоманды (этому полю соответствуют первые выходы блоков 3 и 4), дешифрация вида перехода (номера признака при условном переходе и номера блока памяти при безусловном переходе) блоком 2 по сигналу управления из поля условия микрокоманды (поле микрокоманды, соответст2 вующее четвертым выходам блоков 3 и 4) выполнение микроинструкций (F) и выработка признаков ПР. yTp.) блоком 5 (например, в качестве признаков ПР. >.Р могут использоваться сигналы предварительных переносов, вырабатываемые в блока 5). К моменту окончания выборки следующей микрокоманды блок 2 вырабатывает разрешающий сигнал на управляющий вход одного из блоков

3 или 4, разрешая выдачу второй микрокоманды. С ее появлением начинается вто5 t0 рой такт работы микропроцессора. В микропроцессоре происходят полное наложение процедур выборки микрокоманды из памяти (из блока 3 или 4) и выполнение микроинструкции (F) в блоке 5 (в известном уст15 ройстве несмотря на конвейерную организацию взаимодействия микропрограммного устройства управления и центрального процессора полного наложения этих процедур не происходит) . Это уменьшает длительность такта микропроцессора. Кроме того, условный переход осуществляется за один такт.

Так как адрес обеих микрокоманд, следующих за условным переходом, одинаков, то он выдается в микрокоманде с условным переходом, не дожидаясь достоверности сиг25 нала признака (по состоянию которого произойдет ветвление); происходит выборка обеих микрокоманд параллельно с выполнением микрокоманды, по результату которой произойдет условный переход. К концу такта выборка обеих микрокоманд завершится, вы30 полняется текущая микрокоманда и формируется сигнал признака: взависимости от состояния признака в следующем такте выдается одна из выбранных микрокоманд.

Таким образом, отсутствует необходимость в выполнении дополнительного «пустого» так35 та, присущего известному микропроцессору.

Блоки 2 и 5 микропроцессора, а также внешние устройства управляются сигналами соответствующих полей микрокоманды. Для нормальной работы этих блоков необходимо.

40 чтобы в течение такта в микрокоманде отсутствовали случайные состояния, какие-либо переключения, т.е. достоверная микрокоманда.выдается от начала такта до самого его конца. Для обеспечения этого требования используется регистр 1 (фиг. 4). При

45 выдаче микрокоманды одним из блоков 3 или 4 эта микрокоманда записывается в регистр 1, в этот момент буфер регистра 1 отключен. Одновременно с этим начинается выборка информации из блоков 3 и 4 по сле дующему адресу микрокоманды, т.е. актив50 ный блок памяти (тот, который выдает текущую микрокоманду) через некоторое время начнет переключать свои состояния на выходах. Чтобы не допустить попаданий этих переключений на шину микрокоманды (т.е. выдачи недостоверных состояний в микроко55 маиде в середине такта), буфер активного блока памяти отключается. Синхронно включается буфер регистра 1, который становится источником микрокоманды до конца

1336023

3 такта. Так как в регистр 1 занесена текущая микрокоманда, то на шине микрокоманды переключений не происходит. К концу такта внутри блоков 3 и 4 завершится выборка информации и на буфер одного из этих блоков поступает разрешающий сигнал.

Синхронно на буфер регистра 1 поступает запрещающий сигнал. В результате на шине микрокоманд появляется очередная микрокоманда. Синхронизация всех этих переключений осуществляется сигналами с выходов блока 2.

Регистр 1 необходим также для остановки циклов выборки микрокоманд из блоков

3 и 4 в режиме остановки всего микропроцессора. Дело в том, что первые выходы блоков 3 и 4 непосредственно соединены с их адресными входами. Такое соединение само по себе привело бы к автогенерации.

Однако, если, имея регистр 1 во второй половине такта, когда микрокоманда записана в регистр 1 и выдается им на шину микрокоманд «заморозить» это состояние, т.е. не подавать разрещающего сигнала на один из блоков 3 или 4 и не снимать разрешающий сигнал с регистра 1, то происходит остановка в процедуре выдачи микрокоманд. Для остановки всего микропро цессора необходимо также прекратить подачу синхроимпульсов на блок 5. Все это (т.е. полная остановка микропроцессора) достига ется прекращением подачи синхроимпульсов на соответствующий вход микропроцессора.

Частный случай остановки — такт с «растянутой» длительностью (при работе с медленно действующими внешними устройствами); для реализации которого достаточно задержать поступления очередного синхроимпульса на микропроцессор.

При условном переходе из поля условия микрокоманды в регистр 6 (фиг. 2) поступает номер i признака (i=1,....,n), по состоянию которого происходит условный переход. Код этого поля записывается в регистр

6, дешифрируется узлом 7 и состояние

i-ro признака через i-й элемент И 8 — 1 поступает на элемент ИЛИ 9. Если i-й признак равен логическому «О», то на выходе элемента 9 будет логический «О», а на выходе элемента HE 10 — логическая «1». В этом случае открыт для прохождения сигнала элемент И 11 — 2, выход которого управляет буфером блока 4, т.е. условный переход по

i-му признаку, равному логическому «О», произойдет в блок 4. Если i-й признак равен логической «1», то в результате будет открыт для прохождения сигнала элемент И

11 — 1, т.е. условный переход произойдет в блок 3. При безусловном переходе в блок 3 в поле условия микрокоманды записывается состяние =п+ I. При дешифрации этого состояния логическая «1» появляется на соответствующем выходе дешифратора 7 и поступает на (п+1) -й вход элемента ИЛИ 9.

В результате разрешающий сигнал поступает на элемент И 11 — 1, т е. микроко1О !

4 манда выдается блоком 3. При безусловном переходе в блок 4 в поле условия микрокоманды записывается состояние i=0. Нулевой выход дешифратора не используется, т.е. на всех его выходах с 1-го по (и+1)-й будет логический «О», в результате очередная микрокоманда выбирается из блока 4. Разрешающим сигналом для блоков 3 и 4 служит синхросигнал, проходящий через элемент И

11 — 1 или элемент И 11 — 2 на управляющий вход блока 3 или 4. Кроме того по синхросигналу происходит запись микрокоманды в регистр 1. Синхросигнал, проходя через элемент НЕ 12, управляет буфером регистра 1: в момент высокого уровня синхросигнала логическая «1» поступает на первый или второй выход блока 2 (открывается буфер одного из блоков 3 или 4), а на буфер регистра 1 поступает запрещающий сигнал, в момент нулевого уровня синхросигнала на управляющие входы блоков 3 и 4 поступает логический «О» (т.е. буферы блоков 3 и 4 закрыты), а на управляющий вход регистра 1 — логическая

«1», открывающая его буферы. В этот момент возможна остановка микропроцессора (при «замораживании» нулевого уровня синхроси гнала) .

При реализации блока 2 возможны варианты, обусловленные конкретными временными соотношениями функционирования блоков и элементов микропроцессора. Например, для увеличения быстродействия блока 2 (в тех случаях, когда остальные блоки работают более быстро) можно отказаться от дешифратора 7, записывая в регистр 6 однопозиционный (унитарный) код.

Это целесообразно при небольшом количестве признаков. так как унитарное кодирование увеличивает разрядность микрокоманды. Возможен вариант блока 2, в котором отсутствует регистр 6, в том случае, когда дешифратор 7 имеет большую задержку (например, при большом количестве признаков); которая заменяет конвейерную задержку регистра 6, т.е. дешифратор кроме функции дешифрации выполняет функцию динамического элемента памяти. В этом случае поле микрокоманды должно быть соединено с регистром 1 аналогично всем остальным полям, так как необходимо сохранить состояние поля условия до конца такта. Дешифратор 7 представляет для дешифра ции время, почти равное длительности такта (т.е. дешифратор 7 может быть. многоразрядным).

При распределении микрокоманд в памяти (фиг. 5 и 6) первая микрокоманда F располагается по нулевому адресу блока 4. В адресное поле первой микрокоманды записывается адрес второй микрокоманды (например, А1), в поле условия — номер блока памяти при безусловном переходе (О илг п+1) или номер признака (i=1,...,п) при условном переходе. Пусть переход по второй микрокоманде F2 происходит в ячейку А! бло1336023

Формула изобретения ifeeuz ПРЬ„, УПРбСО

Рг

5 ка 4, тогда в поле условия (УСЛ 1) первой микрокоманды должен быть записан нулевой код. Таким образом, полный код первой микрокоманды: А1, О Fl, УСЛ1. Переход от второй микрокоманды к третьей также безусловный. Если третью микрокоманду расположить по адресу АО блока памяти 3., то полный код второй микрокоманды равен АО, и+1, F2, УСЛ 2. От третьей микрокоманды происходит условный переход по признаку номер один (Пр. 1) к микрокоманде F4 при Пр. 1=0 или к микрокоманде F5 при Пр 1=1.

Микрокоманды F4 и F5 должны быть расположены по одному адресу, например по

А2, причем микрокоманда F4 должна располагаться в блоке 4, а F5 — в блоке

3. Исходя из расположения микрокоманд

F4 и F5 и номера признака для условного перехода заполняются адресное поле и поле условия микрокоманды F3, А2, 1 F3, УСЛ 3 и тд.

Микропроцессор, содержащий первый блок памяти, регистр микрокоманд и операционный блок, синхровход, информационный вход, первый и второй информационные выходы которого соединены соответственно с синхровходом микропроцессора, информационным входом микропроцессора, информационным и адресным выходами микропроцессора, первый, второй информационные выходы и синхровход регистра микрокоманд подключены соответственно к входу микроинструкций операционного блока, уп равл яющему выходу м и кроп роцессора и ь синхровходу микропроцессора, отличающийся тем, что, с целью повышения производительности, он содержит второй блок памяти, регистр условий, мультиплексор условий, два элемента И и два элемента НЕ, причем ад5 ресные входы первого и второго блоков памяти соединены с третьим информационным выходом регистра микрокоманд, синхровход, вход сброса и выход регистра условий подключены соответственно к синхровходу и вхо ду начальной установки микропроцессора и адресному входу мультиплексора условий, первый и второй информационные входы и выход которого соединены соответственно с выходом признака результата операционного блока, входом внешних условий микропроцессора и первым входом первого элемента И, вход и выход первого элемента

НЕ подключены соответственно к выходу мультиплексора условий и первому входу второго элемента И, вторые входы первого и второго элементов И и вход второго элемента HE соединены с синхровходом микропроцессора, входы управления отключением выходов первого и второго блоков памяти и регистра микрокоманд подключены к выходам соответственно первого и второго элементов

И и второго элемента НЕ, вход сброса регистра микрокоманд соединен с входом начальной установки микропроцессора, выходы поля микроинструкций, поля операции и поля адреса первого и второго блоков памяти подключены соответсгвенно к первому. второму и третьему информационным входам регистра микрокоманд, а также его первому, второму и третьему информационным выходам, а выходы поля условия первого и второго блоков памяти соединены с информационным входом регистра условий.

1336023 инрономаноа до ежился аия пью моменсп . озиолч кои п анобки

Ьыброна нобоя микрокоманда

ПмК

Ьыбрана сле3уюцая микрононанда

/ avano быдоркй следующей микр команды

Окончание быборк микрокоманды, быбоча микро— команды по сигналу с bC0n

Дешисрроция биоа перекода, Юькдача упробляющего сигнала но один из блок памяспи по сиен лу признака или бРзуслобна икрокоманбыбаекп оддерлчибося) буфери регистром начало быполнени микроинсппрукции г быробогпка Agn енник признакоб бля бей

0нончание быполнения тнроинсспрукции, запись информации б

Ж;гооные регистры (00p даннык), быооча инсрормации на быкоаные шины

1336023 иг.

А2

АЗ фигд х-безразличное согтояние

А0

А4

А5

Ядресноя УПР ЬСОП чоспв ин.по УПР6нешн. инструниия

1336023

Составитель Г. Виталиев

Редактор Л. Гратилло Техред И. Верес Корректор Г. Решстник

Заказ 3804/45 Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Г1роизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4