Устройство для обучения операторов

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в тренажерах операторов АСУ. Цель изобретения - расширение дидактических возможностей устройства. Устройство содержит регистр 1 адреса, блок 2 памяти, регистр 3 микрокоманды, блок 4 индикации, блок 5 ввода ответов, блоки 6, 7 сравнения, элементы И 8, блок 9 памяти, триггер 10, элемент ИЛИ 11, элемент задержки 12, элементы И 13, триггеры 14, элемент ИЛИ 15, элементы И 16, элемент ИЛИ 17. Сущность изобретения заключается в обучении оператора поэтапному самоконтролю выполняемых действий, а также способности обнаруживать и исправлять ошибки, допуш.епные при управлении отдельными объектами в общем алгоритме управления. 1 ил. S (Л со со 05 О 00 4

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1336084

А1 (5D 4 б 09 В 9 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21 ) 4046385/24-24 (22) 01.04.86 (46) 07.09.87. Бюл. № ЗЗ (72) В. И. Балабай, В. А. Бирюков, С. И. Севастьянов, И. Ю. Кивирский и О. А. Соловьев (53) 681.3.071 (088.8) (56) Авторское свидетельство СССР № 918962, кл. G 009 9 В 99//0000, 1980. (54) УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ (57) Изобретение относится к области автоматики и вычислительной техники и может быть использовано в тренажерах операторов АСУ. Цель изобретения — расширение дидактических возможностей устройства.

Устройство содержит регистр 1 адреса, блок

2 памяти, регистр 3 микрокоманды, блок 4 индикации, блок 5 ввода ответов, блоки 6, 7 сравнения, элементы И 8, блок 9 памяти, триггер 10, элемент ИЛИ 11, элемент задержки 12, элементы И 13, триггеры 14, элемент

ИЛИ 15, элементы И 16, элемент ИЛИ 17.

Сущность изобретения заключается в обучении оператора поэтапному самоконтролю выполняемых действий, а также способности обнаруживать и исправлять ошибки, допущенные при управлении отдельными объектами в общем алгоритме управления. 1 ил.

1336084

40

Изобретение относится к тренажерам о»ераторов систем управления и может быть использовано для обучения операторов систем управления.

Цель изобретения — расширение дидактических возможностей устройства.

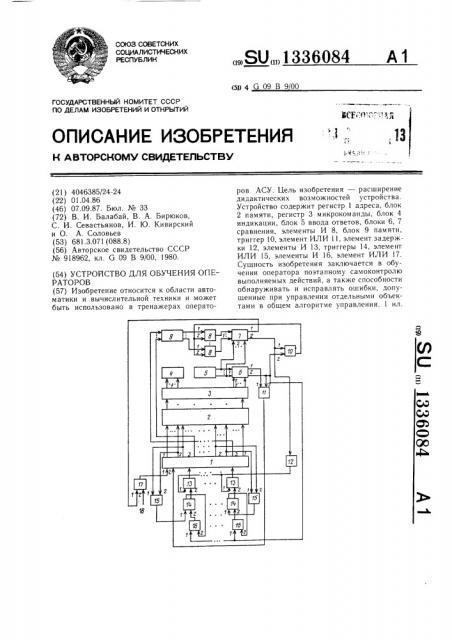

На чертеже представлена структурная схема устройства для обучения операторов.

Устройство содержит регистр 1 адреса (микрокоманды), блок 2 памяти (микропрограммы), регистр 3 микрокоманды, блок 4 индикации, блок 5 ввода ответов, блоки 6 и 7 сравнения, группу элементов И 8, блок 9 памяти, триггер 10, элемент ИЛИ 11, элемент 12 задержки, группу элементов И 13, группу триггеров 14, группу элементов ИЛИ

15, группу элементов И 16, элемент ИЛИ 17 и вход 18 запуска устройства.

Регистр 1 предназначен для задания управляющей составляющей алгоритма деятельности оператора. Блок 2 предназначен для хранения в виде микрокоманд данных о каждой операции алгоритма управления.

При появлении сигналов на входах блока 2 происходит считывание микрокоманды текущей операции алгоритма в регистр 3, который предназначен для хранения данных текущей, обрабатываемой, операции алгоритма. Данный регистр состоит из двух микроопераций: в первой хранится код органа индикации-блока 4, который изменяет свое состояние в данной операции алгоритма, а во второй микрооперации — код органа блок 5, на который оператор должен воздействовать в той же операции алгоритма деятельности.

Блоки 4 и 5 являются физической моделью пульта оператора реальной ЛСУ.

Блок 6 предназначен для оценки безошибочности выполненного оператором воздействия на орган блока 5 — требуемому органу. В случае совпадения поступающих кодов, т. е. безошибочности выполненного воздействия оператора, сигнал появляется на первом выходе блока 6. Если оператор задействовал не тот орган блока 5, то совпадения кодов не происходит и сигнал появляется на втором выходе блока 6.

Блок 7 служит для проверки факта обнаружения оператором в управлении одним объектом перед его переходом к управлению очередным объектом. Если оператор обнаружил допущенную ранее ошибку и возобновил управление этим же объектом, то в блоке 7 происходит сравнение кодов, поступающих с выходов блока 5 и блока 9, при этом сигнал появляется на втором выходе блока 7. Сигнал»а первом его выходе появляется в случае, если оператор приступил к управлению следующим объектом, не обнаружив, или не устранив ошибку в управлении предыдущим объектом.

Блок 9 хранит коды органов управления, с которых начинается управление каждым новым объектом, к этим же органам управления оператор должен возвратиться, если цель управления данным объектом не достигнута из-за допущенных им ошибок.

Триггер 10 хранит факт совершения оператором ошибки в процессе управления объектом.

Группа триггеров 14 содержит их столько, сколько объектов управления включено в общий алгоритм. Они позволяют оператору после обнаружения ошибки в управлении объектом вернуться к первой операции этой части алгоритма и устранить допущенную ошибку.

Устройство функционирует следующим образом.

Перед включением его триггер 10 находится в нулевом состоянии, триггеры 14— в единичных состояниях.

С включением устройства, за счет появления сигнала на входе 18, через элемент 17 этот сигнал поступает на вход регистра 1.

По этому сигналу из первой ячейки регистра 1 выбран код первой микрокоманды в блоке 2. Данная микрокоманда переписывается в регистр 3, из которого содержимое первой микрооперации поступает на панель блока 4, где соответствующий орган изменяет свое состояние. Оператор, восприняв информацию, осуществляет соответствующее воздействие с помощью органа блока 5. Код задействованного органа управления поступает на одни входы блока 6, на другие входы которого поступает из второй микрооперации микрокоманды код требуемого органа управления. При совпадении поступивших кодов сигнал появляется на первом выходе блока 6 и поступает на вход регистра 1. При поступлении сигнала на данный вход регистра 1 происходит сдвиг вправо и считывание кода очередной микрокоманды из ячеек регистра 1. Весь описанный цикл функционирования повторяется, но уже для второй операции алгоритма и т. д. При этом методика предусматривает возможность перехода оператора к очередной операции, в пределах управления одним объектом, даже при совершении им ошибки на текущей операции. Поэтому в случае ошибочных действий и несовпадении кодов в блоке 6 сигнал появляется на другом его выходе и через вход элемента ll поступает на вход регистра 1.

Выходы регистра 1 обьединены в группы по числу объектов управления, при этом выходы каждой группы через элементы 15 подключены к единичным входам триггеров 14. При управлении отдельным объектом безошибочность действий оператора контролируется нулевым состоянием триггеров 14. При совершении оператором ошибки сигнал появляется на втором выходе блока 6, данный сигнал переводит триггер 10 в единичное состояние и через элемент 16

1336084

Составитель Л. Карлов

Редактор Н. Бобкова Техред И. Верес Корректор 51. Бескид

Заказ 3807/48 Тираж 433 Подписное

ВНИИПИ Государственного комитета СССР по делаги изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4 5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 переключает триггер 14 в единичное состояние. После завершения оператором управления данным объектом сигнал с выхода регистра 1 поступает на соответствующий вход блока 9, с выхода которого через открытые 5 элементы 8 код органа управления первой операции управления данным объектом поступает на вход блока 7. В случае, если оператор не обнаружил допущенной им ошибки, при управлении данным объектом и попытается перейти к управлению очередным объектом, код задействованного органа блока 5 поступает на вход блока 7 и сравнения не происходит. Сигнал с выхода блока 7 через элемент 17 поступает на вход регистра 1 и приводит устройство в состояние, соответствующее началу алгоритма, т. е. новой тренировки. В том случае, если оператор обнаружил допущенную ошибку, он выбирает орган управления, соответствующий повторному выполнению той части алгоритма, которая относится к данному объекту управления. При этом в результате сравнения сигнал теперь появляется на втором выходе блока 7. Этот сигнал переводит триггер 10 в нулевое состояние и через элемент 12 и подготовленный элемент 13 поступает на вход регистра 1 и выбирает его ячейку с адресом микрокоманды, хранящей параметры первой операции части алгоритма управления данным объектам управления.

Изобретение расширяет дидактические возможности устройства за счет того, что оператор обучается поэтапному самоконтролю выполняемых действий, что повышает качество его деятельности за счет его способности обнаруживать и устранять ошибки, допущенные при управлении отдельными объектами в общем алгоритме управления.

Формула изобретения

Устройство для обучения операторов, содержащее регистр адреса, выходы первой, второй и третьей групп которого соединены 4О с соответствующими входами первого блока памяти, выходы которого подключены к соответствующим входам регистра м икрокоманды, выходы первой группы которого соединены с соответствующими входами блока индикации, а выходы второй группы — с соответствующими входами первой группы первого блока сравнения, входы второй группы которого подключены к соответствующим выходам блока ввода ответов, и первый элемент ИЛИ, отличающееся тем, что, с целью расширения дидактических возможностей устройства, в него введены второй блок памяти, второй блок сравнения, второй элемент ИЛИ, триггер, элемент задержки, три группы элементов И, группа триггеров и группа элементов ИЛИ, входы которых соединены с соответствующими выходами второй группы регистра адреса, а выходы с R-входами соответствующих триггеров группы, S-входы которых подключены к выходам соответствующих элементов И первой группы, инверсные выходы, — к первым входам соответствующих элементов И первой группы, а прямые выходы — к первым входам соответствующих элементов И второй группы, вторые входы которых соединены с выходом элемента задержки, а выходы — с соответствующими информационными входами регистра адреса, синхронизирующий и установочный входы которого подключены соответственно к выходам первого и второго элементов ИЛИ, вторые входы элементов И первой группы соединены с одним выходом первого блока сравнения, подключенным к S-входу триггера и одному входу первого элемента ИЛИ, другой вход которого соединен с другим выходом первого блока сравнения, вход элемента задержки и R-вход триггера подключены к одному выходу второго блока сравнения, другой выход которого соединен с первым входом второго элемента ИЛИ, первый вход которого является входом устройства, входы второго блока памяти подключены к соответствующим выходам третьей группы регистра адреса, а выходы — к первым входам соответствующих элементов И третьей группы, вторые входы которых соединены с прямым выходом триггера, а выходы — с соответствующими входами первой группы второго блока сравнения, входы второй группы которого подключены к соответствующим выходам блока ввода ответов.