Доменное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении запоминаюш.их устройств на цилиндрических магнитных доменах. Целью изобретения является расширение области применения устройства. Устройство содержит контроллер 1, накопитель 2, блок 18 модификации адреса программ и блок 19 идентификации типа модуля накопителя. Изобретение обеспечивает воз.можность использования в накопителе различных типов доменных интегральных микросборок. 2 з. п. ф-лы, 4 ил. (Л СО СО 05 О ел /Риг. 1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (594 G 11 С ll 14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4062653/24-24 (22) 25.04.86 (46) 07.09.87. Бюл. № 33 (71) Институт электронных управляющих машин (72) Н. Л. Прохоров, В. К. Раев, Д. И. Леонтьев, А. Е. Шотов, С. О. Кузнецов, В. Е. Красовский, О. В. Матвеев и С. М. Захарян (53) 681.327.66 (088.8) (56) Устройство внешней памяти на гибких магнитных дисках СМ 1800.5602,3.060.022.

Техническое описание.

Мэвити У. К. Применение ЦМД ЗУ в массовой памяти. — Электроника, № 7, 1979.

„„SU„„1336105 А 1 (54) ДОМЕННОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на цилиндрических магнитных доменах.

Целью изобретения является расширение области применения устройства. Устройство содержит контроллер 1, накопитель 2, блок 18 модификации адреса программ и блок 19 идентификации типа модуля накопителя.

Изобретение обеспечивает возможность использования в накопителе различных типов доменных интегральных микросборок. 2 з. п. ф-лы, 4 ил.

1336105

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройство (ЗУ) на цилиндрических магнитных доменах.

Цель изобретения — расширение области применения устройства за счет возможности использования в нем различных типов доменных интегральных микросборок (ДИМ) .

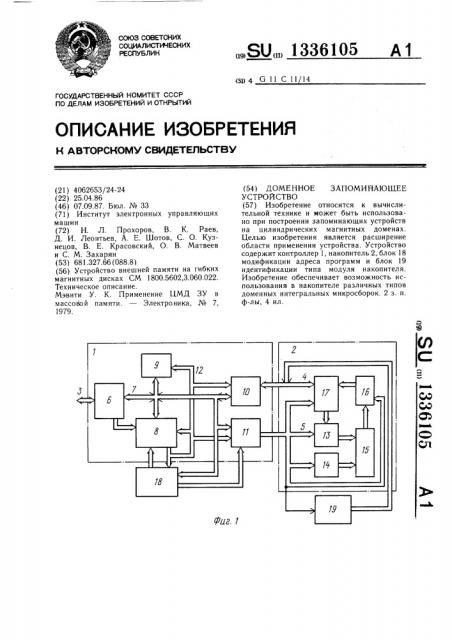

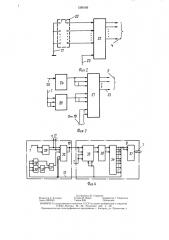

На фиг. 1 представлена структурная схема доменного запоминающего устройства; на фиг. 2 — функциональная схема блока идентификации типа модуля накопителя; на фиг. 3 — функциональная схема блока синхронизации накопителя; на фиг. 4 функциональные схемы блока модификации адреса подпрограмм и блока вычислений и управления.

Доменное запоминающее устройство (фиг. 1) содержит контроллер 1, накопитель 2. На фиг. 1 показаны группа входов-выходов 3 устройства, подключаемая к счетному интерфейсу, группа входоввыходов 4 данных накопителя, входы 5 синхронизации накопителя.

Контроллер содержит блок 6 связи с интерфейсом, подключенный к группе входоввыходов 7 данных контроллера и блок 8 вычислений и управления, буферное ЗУ 9 данных, блок 10 буферных регистров, блок 11 синхронизации накопителя, подключенный к группе входов-выходов 12 управления контроллера.

Накопитель содержит блок 13 усилителей функциональных импульсов, блок 14 усилителей поля, блок 15 ДИМ, блок 16 усилителей считывания, блок 17 преобразования формата данных. На фиг. 1 показаны введенные блок 18 модификации адреса подпрограмм и блок 19 идентификации типа модуля накопителя.

Блок идентификации типа модуля накопителя (фиг. 2) содержит наборное поле 20, в котором один контакт каждой пары подключен к шине 2! питания, а второй — - к первым входам шинного формирователя 22, второй вход которого соединен с линиеи 23 входов синхронизации накопителя.

Блок синхронизации накопителя (фиг. 3) содержит счетчик 24, вход которого соединен с линией 25 синхрочастоты группы входоввыходов управления контроллера, регистр 26 фазы, программируемую логическую матрицу 27.

Блок модификации адреса подпрограмм (фиг. 4) содержит регистр 28 режима, первый логический элемент И 29, второй логический элемент И 30, третий логический элемент И 31, логический элемент НЕ 32 и мультиплексор 33.

Блок вычислений и управления (фиг. 4) содержит регистр 34 микрокоманд, схему 35 формирования адреса микрокоманд, блок 36 памяти микрокоманд и блок 37 микропроцессорных секций.

Доменное запоминающее устройство работает следующим образом.

При записи логические схемы блока 6 связи с интерфейсом дешифруют команду

5 системного интерфейса 3 и передают на схему 35 формирования адреса микрокоманды (выполненную, например, на микросхемах КР 1804 ВУ2, КР1804ВУЗ) запрос на микропрерывание, по которому формируется первый адрес микропрограммы заполнения буферного ЗУ 9 данных, хранимой в блоке 36 памяти микрокоманд. Блок 37 микропроцессорных секций (например, секций К 1804ВС1) под управлением этой микропрограммы, поступающей из блока 36 памяти микрокоманд на регистр 34 микрокоманд, выполняет передачу блока данных по системному интерфейсу 3 из памяти

ЭВМ в буферное ЗУ 9 данных.

После загрузки буферного ЗУ 9 данных происходит запись блока данных в накопи20 тель 2. Предварительно осуществляется чтение кода идентификатора типа модуля накопителя. Микропрограмма формирует на выходе блока 11 синхронизации накопителя сигнал «Чтение идентификатора», передаваемый», передаваемый по линии 23 на шинный формирователь 22 блока 19 идентификации типа модуля накопителя. Этот сигнал пере водит шинный форм иро ватель

22 в активный режим и код идентификатора типа модуля накопителя, заданный наборным полем 20 и огределяющий тип

ДИМ, используемых в накопителе, передается по группе входов-выходов 4 накопителя через блок 10 буферных регистров в блок 18 модификации адреса подпрограмм, где заносится в регистр 28 режима.

Алгоритм модификации адреса подпрограммы применительно к микропроцессорному комплекту К1804 следующий. Если код микроинструкции равен 0101, два старших бита адреса подпрограммы поступают на схему 35 формирования адреса микрокоманды

40 из регистра 28 режима, в противном случае — из регистра 24 микрокоманд.

Содержимое регистра 28 режима передается через мультиплексор 33 по сигналу, формируемому с выхода логических схем

И 29, 30, 31 и HE 32. Схема 35 формирования адреса микрокоманды формирует адрес подпрограммы обслуживания того типа ДИМ, который используется в накопителе. Выполняется чтение текущего адреса в блоке 15 ДИМ. Управляющая информа50 ция, задающая временную диаграмму работы конкретного типа ДИМ, поступает от блока 37 микропроцессорных секций по группе входов-выходов 7 данных контроллера на регистр 26 фазы блока 1 синхронизации накопителя. В зависимости от сос55 тояния счетчика 24, содержимого регистра 26 фазы и регистра 28 режима с выхода программируемой логической матрицы 27, содержащей фазовую диаграмму работы тех

1336105

Формула изобретения типов ДИМ, которые могут быть использованы в накопителе, поступают те или иные функциональные сигналы, передаваемые в накопитель. На время чтения одного блока данных включается блок 14 усилителей поля, который, создает вращающееся магнитное поле в ДИМ. Блок данных считывается по текущему адресу и через блок 16 усилителей считывания поступает в блок 17 преобразования формата данных, который запрещает дальнейшую передачу информации из дефектных регистров блока 15 ДИМ.

Блок данных через блок 10 буферных регистров поступает в блок 37 микропроцессорных секций, где происходит сравнение текущего и заданного адресов бЛока данных. Если они не равны, то происходит поиск заданного адреса. Вычисляется требуемое для этого числа циклов управляющего поля и выполняется перемещение информации в блоке 15 ДИМ на заданное число позиций. Если текущий и заданный адреса оказываются равными, происходит запись блока данных. Блок данных поступает из буферного ЗУ 9 данных через блок 10 буферных регистров в блок 17 преобразования формата данных, который запрещает запись информации в дефектные регистры блока 15 ДИМ. Затем блок данных передается в блок 13 усилителей функциональных импульсов, формирующий эти импульсы в соответствии с временной диаграммой работы ДИМ, и записывается в блок 15 ДИМ.

При выполнении операции чтения блока данных аналогичным образом происходят чтение идентификатора модуля накопителя и поиск адреса блока данных, к которому производится обращение.

Затем выполняется чтение блока данных, который через блок 10 буферных регистров загружается в буфер 9 данных. Далее выполняется разгрузка буферного ЗУ 9 данных и передача блока данных через блок 6 связи с интерфейсом по системному интерфейсу 3. На этом работа устройства заканчивается.

1. Доменное запоминающее устройство, содержащее контроллер и накопитель, причем первая группа входов-выходов контроллера является группой входов-выходов уст5

45 ройства, вторая группа входов-выходов контроллера подключена к группе входоввыходов данных накопителя, группа выходов контроллера соединена с входами синхронизации накопителя, отличающееся тем, что, с целью расширения области применения устройства за счет возможности использования в нем различных типов доменных интегральных микросборок, в него введены блок идентификации типа модуля накопителя, вход которого подключен к одному из входов синхронизации накопителя, а выходы — к группе входов-выходов данных накопителя, и блок модификации адреса подпрограмм, первая группа входов которого подключена к группе входов-выходов данных контроллера, вторая группа входов — к группе входов-выходов управления контроллера, первая группа выходов блока модификации адреса подпрограмм соединена с входами модификации адреса контроллера, а вторая группа выходов — с входами режима контроллера.

2. Устройство по п. 1, отличающееся тем, что блок идентификации типа модуля накопителя содержит наборное поле и шинный формирователь, причем первая группа контактов наборного поля подключена к шине питания, а вторая — к первой группе входов шинного формирователя, второй вход которого является входом блока идентификации типа модуля накопителя, а выходы шинного формирователя являются выходами блока идентификации типа модуля накопителя.

3. Устройство по п. 1, отличающееся тем, что блок модификации адреса подпрограмм содержит регистр режима, входы которого являются первой группой входов блока, первый и второй элементы И, входы которых подключены к второй группе входов блока, третий элемент И, первый вход которого соединен с выходом первого элемента И, элемент НЕ, вход которого подключен к выходу второго элемента И, выход элемента HE соединен с вторым входом третьего элемента И, мультиплексор, выходы которого являются первой группой выходов блока, первая группа входов мультиплексора подключена к выходам регистра режима и является второй группой выходов блока, выход третьего элемента И соединен с вторым входом мультиплексора, третья группа входов которого подключена к второй группе входов блока.

21

Фиг. Z к 1f

Составитель В. Топарков

Редактор А. Козориз Техред И. Верес Корректор Г. Решетник

Заказ 3809/49 Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4