Запоминающее устройство с коррекцией ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при создании запоминающих устройств повышенной надежности на базе кристаллов памяти с многоразрядной организацией. Целью изобретения является упрощение и повышение надежности устройства. Устройство содержит накопитель, коммутатор, шифратор, первый, второй, третий и четвертый блоки сумматоров по модулю два, первый и второй депшфраторы, элемент ИЛИ и элемент И. В устройстве обеспечивается испра.вление всех одиночных и двойныхi расположенных в соседних парных разрядах (1-2, 3-4 и т.д.)., ошибок кодом Хэмминга без введения ,., :. дополнительной информационной и временной избыточности относительно кода Хэмминга, исправляющего одиночные ошибки. 4 ил. i (Л со СО а ю ю

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1336122 А1 цц 4 G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЙ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4053493/24-24 (22) 11,04,86 (46) 07,09.87. Бюл. У 33 (71) Минский радиотехнический институт (72) В,А.Лабунов, П.П,Урбанович, А.M.Суходольский и Н,И.Урбанович (53) 681.327,6 (088.8) (56) Авторское свидетельство СССР

У 927627, кл. G 11 C 29/00, 1982.

Экспресс-информация, Сер. Надежность и контроль качества, 1981, Ф 25, с, 13 17, (54) ЗАПОМИНАЮЩЕЕ УСТРОИСТВО С КОРРЕКЦИЕИ ОШИБОК (57) Изобретение относится к вычислительной технике и может быть использовано при создании запоминающих устройств повышенной надежности на базе кристаллов памяти с многоразрядной органиэацией. Целью изобретения является упрощение и повышение надежности устройства. Устройство содержит накопитель, коммутатор, шифратор, первый, второй, третий и четвертый блоки сумматоров по модулю два, первый и второй дешифраторы, элемент

ИЛИ и элемент И. В устройстве обеспечивается исправление всех одиночных и двойных; расположенных в соседних парных разрядах (1-2, 3-4 и т,д,)., ошибок кодом Хэмминга без введения,; . дополнительной информационнойи временной избыточности относительно кода

Хэмминга, исправляющего одиночные ошибки. 4 ил.

1336122

Изобретение относится к вычислительной технике и может быть использовано при создании запоминающих устройств повышенной надежности на базе кристаллов памяти с многораз-. рядной организацией.

Цель изобретения — упрощение и повышение Надежности устройства.

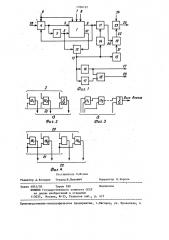

На фиг.lпредставлена структурная схема запоминающегоустройства скоррекцией ошибок;на фиг.2- функциональная схемапервого (второго) блока сумматоров помодулю два;на фиг. 3— функциональная схема третьего блока сумматоров по модулю два; на фиг,4— функциональная схема четвертого блока сумматоров vo модулю два, Запоминающее устройство (фиг.l) содержит накопитель 1 с входами информационных 2 и контрольных 3 разрядов, коммутатор 4, шифратор 5, входы записи считывания 6, выборки 7 и адреса 8, выходы информационных 9 и контрольных 10 разрядов накопителя 25

1, первый блок 11 сумматоров по мо дулю два, второй блок 12 сумматоров по модулю два с выходами 13, первый

14 и второй 15 дешифраторы, элемент

ИЛИ 16, третий блок 17 сумматоров по З0 модулю два, элемент И 18, четвертый блок 19 сумматоров по модулю два, с входами 20 и 21 и выходами 22, Устройство содержит также блок 23 вывода с синхровходом 24 и выходами

25 и информационный вход 26.

Блок 12 (фиг.2) состоит из отдельных сумматоров по модулю два по числу проверочных символов кодового слова, Аналогично строится и блок ll 40 однако число дискретных сумматоров равно количеству информационных символов слова, Блок 17 (фиг.3) состоит из r сумматоров по модулю два (по числу,проверочных символов) . 45

Блок 19 (фиг,4) состоит из сумматоров по модулю два (по числу инфор мационных символов). Накопитель 1 состоит из отдельных кристаллов памяти с многоразрядной организацией об- 50 ращение. Одновременно обращение может производиться к одному либо к нескольким кристаллам (БИС) ° в зависимости от длины слова и разрядности кристалла. 55

По входу 6 устройства поступает сигнал, задающий режим функционирования устройства (запись-считывание), по входу 7 — сигнал выборки кристалла (кристаллов), по входу 24 — сигнал, разрешающий использование информации, считанной иэ накопителя. Все управляющие сигналы связаны с процессором (не показан), На управляющем выходе 27 устройства единичной сигнал появляется при наличии хотя бы одного ошибочного символа в считанном кодовом слове, на выходе 28 — при наличии двойной ошибки, Такие выходы (их состояние) учитываются лишь в режиме считывания через определенный промежуток времени после начала цикла.

Принцип работы устройства, в особенности принцип коррекции ошибок, основан на свойстве кода Хэмминга, состоящего в том, что для исправления всех одиночных.и всех парных двойных ошибок необходимо такое же число проверочных символов, как и для модифицированного кода Хэмминга с кодовым расстоянием, равным "4".

Например, проверочная матрица Н кода при К = 8 имеет вид:

11101001 10000

10011011 01000

Н= 01011100 00100

00110111 00010

11100110 00001

При К = 8 необходимо г+1=5 проверочных символов. При возникновении одной ошибки синдром имеет нечетный вес (число единиц)„ а при возникновении двойной — четный.

Устройство работает следующим образом, Режим работы, На входах 26 — информация, подлежащая записи в накопитель по адресу 8, На основании этого шифратор 5 вырабатывает проверочные символы, Кодовое слово, состоящее из информационных и проверочных битов по входам соответственно

2 и 3 записывается в накопитель 1 °

На этом цикл записи заканчивается.

Режим считывания. На входе 6 устройств — нулевой сигнал. Считываемые из накопителя информационные и проверочные разряды кодового слова поступают соответственно в блок 11 сумматоров,,через коммутатор 4 — шифратор

5 и на вторые входы блока 12 сумматоров, на первые входы которого поступает проверочное число с выходов шифратора 5. Таким образом, на выходах

13 блока 12 формируется синдром, равный нулю лишь при отсутствии ошибок, з 133612

Если возникает одиночная ошибка, то на одном из выходов дешифратора 14 появляется единичный сигнал, который в ссответствующем сумматоре блока 11

5 проинвертирует ошибочный бит информации, В этом случае информационное слово проходит через блок 19 без изменений, При появлении двойной ошибки единичный сигнал будет лишь на одном из входов 21 дешифратора 15, который в двух соответствующих сумматорах блока 19 проинвертирует ошибочные биты.

При поступлении на вход 24 соот1 ветствующего управляющего сигнала считанные из накопителя информационные символы поступают далее по назначению.

Пример. В накопитель записы- 20 вается слово 10110110. В соответст-. вии с этим шифратор 5 вырабатывает проверочные символы (используя матрицу Н) 01000, Кодовое слово

10110110 01000 записывается в накопи- 25 тель. Предложим, что первый и второй символы кодового слова являются ошибочными, т.е. считывают слово

01110110 01000. Блоком 12 формируется синдром 01100, в соответствии с чем на выходе 28 устройства формируется единичный .сигнал. Такой же сигнал будет и на первом выходе дешифратора 15, который в первом и втором сумматорах блока 19 проинвертирует считанные символы кодового слова. На выходах 25 блока 23 по по-. ». ступлении единичного сигнала на вход 24 (при отсутствии ошибок либо при появлении корректируемых

40 ошибок) будет исходная информация без ошибок 10110110.

Формула изобретения

Запоминающее устройство с коррекцией ошибок, содержащее накопитель, адресные входы и вход выборки которого являются одноименными входами устройства, вход записи-считывания накопителя является одноименным входом устроиства и соединен с управляющим входом коммутатора, информационные входы первой группы которого являются информационными входами устройства, информационные входы второй группы коммутатора подключены к входам первой группы первого блока сумматоров по модулю два и к выходам информационных разрядов накопителя, входы инофрмационных разрядов которого соединены с выходами коммутатора.и с входами шифратора, выходы которого подключены к входам контрольных разрядов накопителя и к входам первой группы второго блока сумматоров по модулю два, входы второй группы которого соединены с выходами контрольных разрядов накопителя, а выходы подключены к входам элемента

ИЛИ, третьего блока сумматоров по модулю два и первого дешифратора, выходы которого соединены с входами второй группы первого блока сумматоров по модулю два, выход элемента

ИЛИ является выходом одиночной ошибки устройства и подключен к прямому входу элемента И, инверсный вход которого соединен с выходом третьего блока сумматоров по модулю два, а выход является выходом двойной ошибки устройства, о т л и ч а ю щ е е— с я тем, что, с целью упрощения и повышения надежности, в него введены второй дешифратор и четвертый блок сумматоров по модулю два, причем входы второго дешифратора соеди-, нены с выходами второго блока сумматоров по модулю два, а выходы подключены к входам первой группы четвертого блока сумматоров по модулю два, входы второй группы которого соединены с выходами первого блока сумматоров по модулю два, а выходы являются информационными выходами устройства.

133б122

7 д. длокф

13.

Фиг. 2

13 Ðèã. 5

Фиг. 4

Составитель О. Исаев

Редактор А.Коэориз Техред И.Попович

Корректор Н.Король

Заказ 4051/50 Тираж 589

ВНИИПИ Государственного комитета СССР

IIo делам изобретений и открытий!

13035, Москва, Ж-35, Раушская наб., д. 4/5

°

Подписное

Производственно-полиграФическое предприятие, г,Ужгород, ул, Проектная, 4