Устройство для кодирования цифровой информации циклическими кодами

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и технике связи. Его использование в системах обработки, хранения и передачи информации позволяет повысить 18 быстродействие при кодировании укороченными циклическими кодами, в которых проверочные символы расположены внутри кодового слова. Устройство содержит генератор 1 тактовых импульсов, делитель 2 частоты, триггер 4, формирователь 6 проверочных символов (регистр сдвига с обратными связями ), элемент И 11 и элемент ИЛИ 15. Введение делителя 3 частоты, триггера 5, формирователя 7 проверочных символов (регистр сдвига с инвертированными обратными связями)., сумматора 8, мультиплексора 9, счетчика 10, элементов И 12-14 и элемента ИЛИ 16 обеспечивает кодирование укороченными циклическими кодами с проверочными символами внутри кодового слова без введения дополнительных до полного циклического кода нулей. 2 ил. S о: с ос СО 05 o СП СП

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (50 4 H 03 М 13/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4060111/24-24 (22) 25.04.86 (46) 07.09.87. Бюл. № 33 (72) В. А. Никамин и С. Н. Фролов (53) 621.394.6:681.32 (088.8) (56) Блох Э. Л., Зяблов В. В. Обобщенные каскадные коды. — М.: Связь, 1976, с. 107—

108, рис. 3.39.

Питерсон У., Уэлдон Э. Коды, исправляющие ошибки.— М.: Мир, 1976, с. 254 — 255, рис. 8.2. (54) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ ЦИКЛИЧЕСКИМИ КОДАМИ (57) Изобретение относится к вычислительной технике и технике связи. Его использование в системах обработки, хранения и передачи информации позволяет повысить

„„SU» 1336255 А 1 быстродействие при кодировании укороченными циклическими кодами, в которых проверочные символы расположены внутри кодового слова. Устройство содержит генератор

1 тактовых импульсов, делитель 2 частоты, триггер 4, формирователь 6 проверочных символов (регистр сдвига с обратными связями), элемент И 11 и элемент ИЛИ 15.

Введение делителя 3 частоты, триггера 5, формирователя 7 проверочных символов (регистр сдвига с инвертированными обратными связями), сумматора 8, мультиплексора 9, счетчика 10, элементов И 12 — 14 и элемента ИЛИ 16 обеспечивает кодирование укороченными циклическими кодами с проверочными символами внутри кодового слова без введения дополнительных до полного циклического кода нулей. 2 ил.

1336255

Изобретение относится к вычислительной технике и технике связи и может использоваться в системах обработки, хранения и передачи информации.

Цель изобретения — повышение быстродействия устройства при кодировании укороченными циклическими кодами с проверочнымм и символами внутри кодового слова.

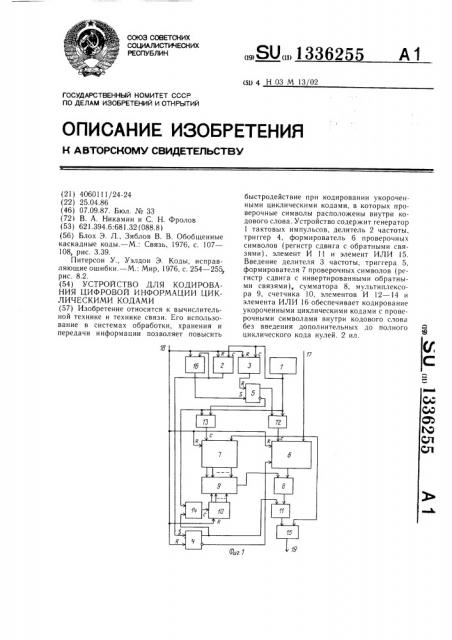

На фиг. 1 дана блок-схема устройства; на фиг. 2 — временные диаграммы его работы.

Устройство для кодирования цифровой информации циклическими кодами содержит генератор 1 тактовых импульсов, первый и второй делители 2 и 3 частоты, первый и второй триггеры 4 и 5, первый и второй формирователи 6 и 7 проверочных символов, сумматор 8, мультиплексор 9, счетчик 10, первый — четвертый элементы И 11 — 14, первый и второй элементы ИЛИ 15 и 16, информационный вход 17, вход 18 синхронизации и выход 19.

Делители 2 и 3 частоты могут быть выполнены на счетчиках с заданным коэффициентом пересчета.

Первый формирователь 6 проверочных символов представляет собой регистр сдвига с обратными связями, выполненными в соответствии с неприводимым полиномом g(x) для первых информационных символов используемого кода. Обратные связи замыкаются ло сигналу на управляющем входе формирователя 6.

Второй формирователь 7 проверочных символов выполнен на регистре сдвига такой же длины, как и в формирователе 6, но обратные связи его выполнены в соответствии с неприводимым лолиномом g(x), где у= х

Например, если обратные связи в регистре формирователя 6 выполнены в соответствии с полиномом g(x)= х + х+ 1, то обратные связи в регистре формирователя 7 должны быть выполнены в соответствии с полиномом g(x) = у" + у + 1.

Предлагаемое устройство предназначено для кодирования цифровой информации укороченными циклическими кодами вида (и, k), в которых общее число n символов меньше числа и в циклических кодах (л,k) а число k информационных символов не меняется. При этом укороченный циклический код задан таким образом, что проверочные символы располагаются в середине кодового слова, т.е.

Vo, Vi,...,V! — i, Qi, Q2,...,Qm, V!, V!+!,... V» — и где V; — информационные символы (i= О, l, 2,...,k — 1); — проверочные символы (J= 1, 2,...,гпЛ ! — число информационных символов, расположенных перед проверочными символами.

В отличие от известного устройства, где кодирование такими кодами осуществляется путем записи перед информационными символами n — и нулей и циклического сдвига всех символов, включая эти нули, до тех пор, пока проверочные символы не переместятся на последние позиции, т.е. приведения кода к виду

5 >> !+1> ° V» — f> g> Q> ">Q> Vo> > 1>» 2 ° ° ° > V! — 1>

g! 92 ° ° ° > Q»>, в предлагаемом устройстве кодирование производится без введения дополнительных нулей.

Устройство для кодирования цифровой

10 информации циклическими кодами работает следующим образом.

В исходном состоянии, которое возникает при появлении сигнала на входе 18 синхронизации (фиг. 2а), делители 2 и 3 частоты, счетчик 10, триггер 4 и формирователи

6 и 7 находятся в обнуленном состоянии, а триггер 5 — в состоянии «I». Элемент

И 12 открыт, а элементы И 11, 13, 14 — закрыты. Обратные связи в формирователе 6 включены сигналом логической «1» с инверсного выхода триггера 4. Обратные связи в формирователе 7 включены в течение всего времени работы устройства.

Информационные символы, поступающие на информационный вход 17 (фиг. 2б) проходят на информационные входы формирователей 6 и 7 и одновременно — через элемент ИЛИ 15 — на выход 19 устройства.

Тактовые импульсы с выхода генератора

1 тактовых импульсов (фиг. 2в) поступают в это время через открытый элемент И 12 на вход синхронизации первого формирователя 6 (фиг. 2г). Поэтому информационные символы Vo, Vi,...,V! продвигаются по ячейкам регистра сдвига в формирователе 6 до тех пор, пока информационный символ

V! не будет записан во входную ячейку памяти этого регистра. Записи информационных символов в формирователь 7 в это время не производится, так как элемент И 13 закрыт и тактовые импульсы на вход синхронизации формирователя 7 не поступают.

40 Делитель 3 частоты (счетчик) при этом подсчитывает тактовые импульсы, вырабатываемые генератором 1. Как"только количество этих импульсов станет равным 1, что соответствует моменту записи символа

V! в регистр формирователя 6, — на вы45 ходе делителя 3 появляется сигнал (фиг. 2д) обнуления триггера 5, который переводится в состояние «О» и сигналом со своего прямого выхода закрыват элемент И 12 (фиг. 2е), а сигналом с инверсного выхода открывает

50 элемент И 13 (фиг. 2ж).

Поскольку на вход синхронизации формирователя 6 тактовые импульсы с выхода генератора 1 не поступают (фиг. 2г), то он переходит в режим хранения результата вычислений, которым являются проверочные символы Q!, Q2,...,Q, вычисленные по первым информационным символам:

Vo> V »...V! — 1> Q! > Q2,-">g»>.

Далее с помощью второго формирователя 7 вычисляются символы V<, Ъ !! ь...,V»

1336255

Таким образом, информационные символы Vp i, Vy g,...,Vip, Vi, поступающие с информационного входа 17 на информационный вход второго формирователя 7, вводятся в ячейки памяти регистра этого формирователя по сигналам генератора 1, поступающим на вход синхронизации формирователя 7 через открытый элемент И 13 (фиг. 2з).

Одновременно информационные символы поступают на выход 19 устройства через элемент ИЛИ 15. Делитель 2 частоты (счетчик) подсчитывает тактовые импульсы с выхода генератора I до тех пор, пока их число не станет равным к, что соответствует моменту записи в формирователь 7 последнего информационного символа V . При этом на его выходе появляется сигнал (фиг. 2и), который переводит триггеры 4 и

5 в состояние «1» (фиг. 2к). Триггер 5 закрывает элемент И 13 и открывает элемент И 12 (фиг. 2е,ж). Формирователь 7 переходит в режим хранения результата вычислений, содержащегося в m его ячейках памяти, так как на его вход синхронизации тактовые импульсы не поступают, а формирователь 6— в режим последовательного сдвига, поскольку тактовые импульсы с выхода генератора 1 через открытый элемент И 12 проходят на его вход синхронизации.

Поскольку триггер 4 теперь находится в состоянии «1», то сигнал логической «1» на его прямом выходе (фиг. 2k) открывает элемент И 14, а сигнал логического «О» на его инверсном выходе (фиг. 2д) отключает цепи обратных связей в регистре формирователя 6. Тактовые импульсы с выхода генератора I поступают на счетный вход счетчика 10 (фиг. 2м), который управляет мультиплексором 9. Информационные входы мультиплексора 9 соединены с параллельными выходами формирователя 7 таким образом, что первый вход мультиплексора 9 соединен с ячейкой формирователя 7, в которой хранится проверочный символ Я„„второй вход — с выходом ячейки, содержащей Я„и так далее — до m-ro входа, который соединен с выходом ячейки, содержащей Qi.

Сигналом с прямого выхода триггера 4 открыт элемент И 11 и за последние n — k=m (или п — k= m — в случае укороченного

1 циклического кода) тактов происходит вывод проверочных сигналов Qi, Qp,...Д,„из устройства на выход 19 путем суммирования в сумматоре 8 проверочных символов

I /

Ql Q2,".,Q содержащихся в ячейках памяти формирователя 6, и проверочных символов Q, Q« i,...Qi, содержащихся в ячейках памяти формирователя 7, следующим образом:

Qi= Qi+ Q-"

Я9 Q2+ Qп — г И

Q=Q. + Qi

Формула изобретения

Устройство для кодирования цифровой информации циклическими кодами, содержащее генератор тактовых импульсов, выход

Для этого регистр в формирователе 6 как упоминалось, переводится в режим последовательного сдвига содержимого ячеек памяти, а ячейки регистра в формирователе 7 опрашиваются в заданном порядке с помощью мультиплексора 9, управляемого счетчиком 10, который подсчитывает тактовые импульсы с выхода генератора 1, поступающие через открытый элемент И 14 на его счетный вход.

При появлении (к+1) -го импульса на выходе генератора на первом входе сумматора 8 появится символ Q с выхода формирователя 6, а на втором — символ Q с выхода мультиплексора 9, который в этот момент подключен к соответствующей ячейке формирователя 7. На выходе сумматора 8— сумма Qi+Q.,= Qi. Символ Q через открытый элемент И 11 и элемент ИЛИ 15 поступает на выход 19 устройства.

При поступлении (k+2) -го тактового импульса с выхода генератора 1 таким же путем происходит формирование второго проверочного символа Qq.

Этот процесс продолжается до тех пор, пока не будут получены и выведены на выход 19 устройства все m проверочных символов Q ь Q, Я„,.

На этом процесс кодирования циклическим кодом считается законченным и следующим импульсом сигнала синхронизации на входе 18 устройство переводится в исходное состояние, необходимое для осуществления последующего цикла работы.

Предлагаемое устройство обеспечивает кодирование цифровой информации как полными, так и укороченными циклическими кодами с поперечными символами, расположенными внутри кодового слова, так как наличие (укороченный код) или отсутствие (полный код) нулей в кодовом слове никак не отражается на процедуре вычисления.

Устройство способно работать в режиме кодирования полным и укороченным циклическими кодами с проверочными символами в конце кодового слова. В этом случае работают только элементы 1, 2, 4, 6, 1!, 15, так как коэффициент счета в делителе 3 (число информационных символов, расположенных после проверочных) равен нулю, следовательно, элемент И 12 всегда открыт, а элемент И 13 всегда закрыт, в формирователь

7 ничего не вводится, и при опросе его ячеек с помощью счетчика IO и мультиплексора 9 на вход сумматора 8 поступают нули.

Использование устройства для кодирования в том случае, когда проверочные символы укороченного циклического кода располагаются внутри кодового слова, обеспечивает значительное повышение быстродействия, особено в случае п ((и.

1336255

ЙИ::::АЗИЗЕ Е ЛБЕ:

< ЛЛПЛЛПП ЛЛЛЛЛ. 1UUUUL ЛЛЛЛП г ЛПЛППЛЛ П ЛППП ЛЛЛЛЛ

1 у 1

| е

1 1

ПЛПЛ Л

П

1 м 1

Л;. — ——

Фиг. 2

Составитель О. Ревинский

Редактор Н. Егорова Техред И. Верес Корректор Е. Рошко

Заказ 3815/57 Тираж 901 Подпис ное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 Г3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 которого соединен со счетным входом первого делителя частоты, выход которого соединен с S-входом первого триггера, прямой и инверсный выходы которого подключены соответственно к первому входу первого элемента И и к управляющему входу первого формирователя проверочных символов, выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого и информационный вход первого формирователя проверочных симво- )p лов объединены и являются информационным входом устройства, R-вход первого триггера и входы обнуления первого формирователя проверочных символов и первого делителя частоты объединены и являются входом синхронизации устройства, выход пер- 15 вого элемента ИЛИ является выходом устройства, отличающееся тем, что, с целью поышения быстродействия устройства при кодировании укороченными циклическими кодами с проверочными символами внутри кодового слова, в устройство введены второй формирователь проверочных символов, мультиплексор, счетчик, сумматор, второй делитель частоты, второй триггер, второй, третий и четвертый элементы И и второй элемент

ИЛИ, первый вход которого и входы обну- 25 ления счетчика, второго делителя частоты и второго формирователя проверочных симво6 лов объединены и подключены к входу синхронизации устройства, второй вход второго элемента ИЛИ подключен к выходу первого делителя частоты, выход второго элемента ИЛИ соединен с S-входом второго триггера, счетный вход второго делителя частоты и первые входы второго, третьего и четвертого элементов И объединены и подключены к выходу генератора тактовых импульсов, выход второго делителя частоты соединен с R-входом второго триггера, прямой и инверсный выходы которого подключены к вторым входам соответственно второго и третьего элементов И, выходы которых соединены с входами синхронизации соответственно первого и второго формирователей проверочных символов, выход первого формирователя проверочных символов подключен к первому входу сумматора, выход которого соединен с вторым входом первого элемента И, второй вход четвертого элемента И подключен к прямому выходу первого триггера, выход четвертого элемента

И соединен со счетным входом счетчика, выходы которого подключены к адресным входам мультиплексора, выходы второго формирователя проверочных символов подключены к информационным входам мультиплексора, выход которого соединен со вторым входом сумматора.