Способ преобразования произведения двух напряжений в частоту следования импульсов и устройство для его осуществления

Иллюстрации

Показать всеРеферат

чособ преобразования произведени двух напряжений в частоту следования импульсов реализован в устройстве , содержащем интегратор 1, источ : ик (И) 2, 10 входного напряжения (Н), И 4 эталонного Н, гииерболичес- K:-ai преобразователь 5, элементы 6, 9 .равнения, блоки 7, 8 памяти, резистивный делитель 11. Интегрируют первое Н до заданного уровня, уравновешивают его интегральное значение импульсами эталонного Н длительностью, обратно пропорциональной среднему значению второго Н, и формируют выходной импульс в течение каждого цикла уравновешивания. Фиксируют интегральное значение Н в начальный момент формирования уравновешивающего импульса , инвертируют и фиксируют интегральное значение Н в момент окончания уравновешивающего импульса. Определяют среднее значение двух фиксированных Нив момент достижения интегральным значением Н среднего значения формируют следующий уравновешивающий импульс эталонного Н. При этом каждый выходной импульс формируют после окончания уравновешивающего импульса в момент достижения интегральным значением Н нулевого уровня. Изобретение noBbmiaer точность преобразования . 2 с.п. ф-лы, 2 ил. с (О (Л со GO СО 4

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

4 А1 ()9) ())) (5))4 С О1 R 21 06

Р жтг:;) 6

) 3g 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АBTOPCKOMV СВИДЕТЕЛЬСТВУ

Фиг г

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4053921/24-21 ,(22) 09. 04. 86 (46) 15.09.87. Бюл. М 34 (72) Л.П.Колобаев (53) 621.317(088.8) (56) Авторское свидетельство СССР

)) 617803, кл. Н 03 В 19/00, 1976.

Авторское свидетельство СССР

М - 1045381, кл. Н 03 К 13/20, 1981. (54) СПОСОБ ПРЕОБРАЗОВАНИЯ ПРОИЗВЕДЕНИЯ ДВУХ НАПРЯЖЕНИЙ В ЧАСТОТУ СЛЕДОВАНИЯ ИМПУЛЬСОВ И УСТРОЙСТВО ДЛЯ ЕГО

ОСУЩЕСТВЛЕНИЯ (57) (и соб преобразования произведени двух напряжений в частоту следования импульсов реализован в устройстве, содержащем интегратор 1, источ: ик (И) 2, 10 входного напряжения (Н), И 4 эталонного Н, гиперболическ:п) преобразователь 5, элементы 6, 9 . равнения, блоки 7, 8 памяти, резистивный делитель 11. Интегрируют первое

Н до заданного уровня, уравновешивают его интегральное значение импульсами эталонного Н длительностью, обратно пропорциональной среднему зна— чению второго Н, и формируют выходной импульс в течение каждого цикла уравновешивания. Фиксируют интегральное значение Н в начальный момент формирования уравновешивающего импульса, инвертируют и фиксируют интегральное значение Н в момент окончания уравновешивающего импульса. Определяют среднее значение двух фиксированных Н и в момент достижения интегральным значением Н среднего значения формируют следующий уравновешиЮ вающий импульс эталонного Н. При этом каждый выходной импульс формируют после окончания уравновешивающего импульса в момент достижения интеграль- С ным значением Н нулевого уровня. Изобретение повьппает точность преобразования. 2 с.п. ф-лы, 2 ил. ния импульсов за счет уменьшения динамической погрешности.

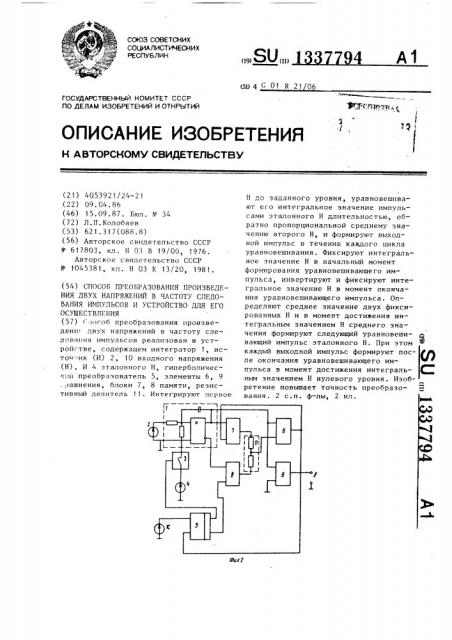

Па фиг. 1 представлены диаграммы напряжений, поясняющие способ преобразования произведения двух напряжений в частоту следования импульсов, на фиг. 2 — схема устройства, реализующего этот способ, Устройство содержит интегратор 1, 1 первый источник 2 входного напряжения, ключ 3, источник 4 эталонного напряжения гиперболический преоб1

20 разователь 5, первый элемент 6 сравнения, первый и второй блоки 7 и 8 памяти, второй элемент 9 сравнения, второй источник 10 входного напряжения и реэистивный делитель 11 напря6 жения. Вход интегратора 1 подключен к выходу первого источника 2 входного напряжения и через ключ 3 к выходу источника 4 эталонного напряжения, Первый вход гиперболического преобразователя 5 подключен к второму источнику 10 входного напряжения первый выход — к управляющему входу ключа 3, а второй вход — к выходу первого элемента 6 сравнения, первый вход которого подключен к выходу интегратора 1. Аналоговые входы первого и второго блоков 7 и 8 памяти подключены соответственно к неинвертированному и инвертированному выходам интегратора 1, импульсные входы — к

40 выходу первого элемента 6 сравнения и второму выходу гиперболического преобразователя 5,а выходы — к крайним точкам резистивного делителя 11 напряжения, средняя точка которого 45 подключена к второму входу первого элемента 6 сравнения. Первый вход второго элемента 9 сравнения подключен к выходу интегратора 1, второй вход — к общей шине, а выход являет- 50 ся выходом устройства.

Способ осуществляют следующим образом.

Интегрируют первое напряжение до заданного уровня (диаграмма изменения первого входного напряжения представлена на фиг. 1а, интегральное значение напряжения — на фиг. 1в). Затем

1 133779

Изобретение отностися к электроизмерительной технике и может быть использовано в системах учета и регулирования электрической энергии.

Цель изобретения — повышение точности преобразования произведения двух напряжений в частоту следовауравновешивают интегральное значение первого напряжения импульсами эталонного напряжения длительностью, обратно пропорциональной среднему значению второго напряжения, и формируют очередной выходной импульс в течение каждого цикла уравновешивания.

Далее фиксируют интегральное значение напряжения (фиг. 1в) в начальный момент формирования уравновешивающего импульса (т.е. запоминают максимальное значение напряжения фиг.

lt) инвертируют и фиксируют интегральное значение напряжения в момент окончания уравновешивающего импульса (ипвертированное интегральное значение напряжения представлено на ()III . 1 s ПУHKTHpной линией а фикси рованное значение максимума этого напряжения — на фиг. 1 ). Далее определяют среднее значение двух упомянутых фиксированных напряжений (на фиг.

1г представлено среднее значение от двух напряжений, изображенных на фиг.

1г и 1 ). Ь момент достижения интегральным значением напряжения указанного среднего значения (точка 12 на фи . 1s) cледующий уравновешивающий импульс эталонного напряжения. При этом каждый выходной импульс (фиг. 1и)формируют в момент достижения интегральным значением напряжения (фиг. Is) нулевого уровня. Б результате значения второго сомножителя (фиг. 1 S — заштрихованные части диаграммы) приходятся на середину периода осреднения первого напряжения (фиг. 1a).

Устройство, реализующее способ, работает следующим образом.

Напряжение от первого источника

2 входного напряжения подается на вход интегратора 1, по мере возрастания напряжение на выходе интегратора достигает значения порога срабатывания первого элемента 6 сравнения (операция интегрирования первого напряжения до заданного уровня). После его срабатывания запускающий сигнал поступает на импульсный вход гиперболического преоГ>ра«онателя 5, который преобразует напряжение второго источника 10 входного напряжения, подключенного к его аналоговому входу, во временной интервал (импульс) длительностью, обратно пропорциональной второму напряжению. Этот импульс с первого выхода гиперболического пре3 1э >77 образовате:(я > поступает ня упрявлян>— щий вход ключа 3, с помощью которог О источник эталонного напряжения подключается к второму входу интегратора 1. В результате происходит сброс напряжения на выходе интегратора 1.

Таким образом осуществляется оперязначения первого напряжения импульса- 1 ми эталонного напряжения длител(.«остью, обратно пропорциональной среднему зняченин> второго напряжения.

В момент срзбатыняния первогo 3ле— мента 6 сравнения на выходе последне15

ГО Въ(рябять(вяется кОрОткий импу(lьс > поступающий на импульсньп(вход первого 6(ока 7 памяти, в результате (его на выходе последнего фиксируется ня7Г1 ное зняче(ше этого напряжения в мо30 мент окончания уравновешиваю(пего им1О

45 напряжений.

55 ция уравновешивания интегрального пряжение, равное максимальному значению напряжения на выходе интегря— тора 1. Таким образом Осуществляется операция фиксации интегрального зня— чения напряжения в начальный момент формирования уравновешивающего импульса.

С второго выхода гиперболического преобразоватеня 5 фор((ируется короткий импульс в момент окончания импульса сброса. 11мпульс с второго выходя поступает на импульсный вход второго блока 8 памяти, «а аналоговый вход которого подается инвертированное напряжение интегратора 1. Б результате на выходе второго блока 8 памяти фиксируется максимальное знячение инвертированного выходного напряжения интегратора. !!а средней точке резистивного делителя 11 на((ряжения интегратора. Ня средней точке резистивного делите гя 11 напряжения получается среднее напряжение двух блоков 7 и 8 памяти. Таким образом осуществляется операция определения среднего значения двух фиксированных

Это напряжение поступает на второй вход первого элемента 6 сравнения. К(>гг(а нг(г(ряжение на выходе интегратора 1, подаваемое на первый вход первого ->лемента 6 сравнения, достигяс т ука..(анного уровня, сигнал с его в(,(ход(1 запускает гиперболический преОбр;77овятель 5 и происходит очередной с брос напряжения на выходе интегратора !. Второй элемент 9 срявнсгпгя формирует выходной сигнал при изм(.ненни знака напряжения на выходе инте(раторя 1 с отрицательного

9-(4 ня положител(.ный. Таким образом рея—

Гl И 3 y C Т С Я 1 Я К. (К>Ч(1 Т Е(1 Ь Н Я Я О П Е Р Я Ц И Я формирование каждого выходного импульса после окончаги(я уравновешиваю(((его импульса в момент достижения интегральным значением напряжения нулевого уровня. ф о р м у л а и з о б р .е т е и и я

1. Способ преобразования прои:(ве дения двух напряжений в частоту следовяния импульсов, согласно которому интегрируют первое напряжение до заданного уровня, уравновешивают интегральное значение первого напряжения имп у 11 с (l м« . > т(1 ((o(I (I QI напряжения дли тель«остью, Обратно npo((op((«o((;1:(ьной средне л(у значению второго напряжения и формируют очередной выходной импульс в течение кажпогo цикла ур;(вновешивания, о т л и и а ю шийся тем, что, с целью повышения точности, фиксируют интеграл!,ное значение перного напряжения в начальный момент формирования уравновешивающего импульса, инвертируют и фиксируют интегральпульс я, (>(7ределяют среднее значение двух упомянутых фиксированных няпряжений и в момент достижения интегряльным значением напряжен«!я указанного среднего значения форл(ирук>т следующий урявновешивающии импульс эталонного напряжения, при этом каждый выходной импульс формирун>т после окончания уравновешивающего импульса в момент достижения интегральным значением напряжения нулевого уровня.

2. Устройство для преобразования произведения двух напряжений в часто-,у следования импульсов, содержащее интегратор, подключенный своим входом к выходу первого источника входного напряжения и через ключ — к выходу источника эталонного напряжения, гиперболический преобразователь, подключенный первым входом к второму источнику входного напряжения, первым выходом — к управляющему входу ключа, а вторым входом — к выходу первого элемента сравнения, подключенного своим первым входом к выходу интегратора, о т л и ч а ю щ е е с я тем, что, с целью повышения точности оно дополнительно содержит первый и второй блоки памяти, второй элемент

7794 е

Составитель С.Сафохин

Редактор А.Лежнина Техред В.Кадар

Корректор M. Пожо

Заказ 4125/42 Тираж 730

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная 4

5 133 сравнения и резистивный делитель напряжения, причем первый аналоговый вход каждого из блоков памяти подключен соответственно к неинвертированному и инвертированному выходам интегратора, импульсные входы — к выходу первого элемента сравнения и второму выходу гиперболического преобразователя, а выходы — к крайним точкам резистивного депителя напряжения, присоединенного своей средней точкой к второму входу первого элемента сравнения, при этом в качестбве выхода устройства используется выход второго элемента сравнения, подключенного своим первым входом к выходу интегратора, а вторым входом— к общей шине.