Цифровой измеритель rlc-параметров

Иллюстрации

Показать всеРеферат

Изобретение относится к электроизмерительной технике и может быть использовано при измерении RLC-napa- метров в широком диапазоне частот. Цель изобретения - повышение точности измерений при обеспечении высокой чувствительности и быстродействия достигается путем адаптивно-мультипликативных коррекций и режима накопления , а также формирования результатов после каждого цикла измерений. Для этого в устройство дополнительно введены дифференциальный усилитель 5, источник 7 напряжения смещения , набор фазовращателей 10, аналоговый коммутатор 11, переключатель 12, фаяоинвертор 13 и компараторы 14 и 15. Кроме того, устройство содержит синтезатор 1 частот, исследуемый двухполюсник 2, образцовый двухполюсник 3, активное сопротивление 4, переключатели 6 и 9, источник 8 образцового напряжения, генератор 16 импульсов, интегратор 17, селектор 18, блок 19 управления, вычислительный блок 20 и блок 21 индикации. 1 табл. 2 ил. (Л (Л со 00 00 to фиг

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1337820

Ai (51) 4 Г 01 К 27/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

СФ

СР

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Н ABTOPCKOMY СВИДЕТЕЛЬСТВУ (2 1) 4052428/24-21 (22) 08.04.86 (46) 15.09.87. Бюл. 9 34 (72) Н.И.Грибок, В.В.Бинковский, В.М.Макух, С.А.Савенко и С.Г.Романюк (53) 62 1.3 17 .33 (088 .8) (56) Авторское свидетельство СССР

N- 467302, кл. С 01 К 27/26, 1972.

Авторское свидетельство СССР

Р 868629, кл. G 01 R 27/02, 1981. (54) ЦИФРОВОЙ ИЗМЕРИТЕЛЬ КЕС-ПАРАМЕТРОВ (57) Изобретение относится к электроизмерительной технике и может быть использовано при измерении Ы.С-параметров в широком диапазоне частот.

Цель изобретения — повышение точности измерений при обеспечении высокой чувствительности и быстродействия достигается путем адаптивно-мультипликативных коррекций и режима накопления, а также формирования результатов после каждого цикла измерений.

Дпя этого в устройство дополнительно введены дифференциальный усилитель 5, источник 7 напряжения смеще— ния, набор фазовращателей 10, аналоговый коммутатор 11, переключатель

12, фазоинвертор 13 и компараторы 14 и 15. Кроме того, устройство содержит синтезатор 1 частот, исследуемый двухполюсник 2, образцовый двухполюсник 3, активное сопротивление 4, переключатели 6 и 9, источник 8 образцового напряжения, генератор 16 импульсов, интегратор 17, селектор

18, бпок 19 управления, вычислительный блок 20 и блок 21 индикации. табл, 2 ил.

133

И.«обретение относится к .)лектрои «в мерител«.ной технике и может <)KIT(ис— пользс>вано при измерении И.С-параметров в широком часTQT«to«1 I(Bat«(tao«I(, Целью изобретения является повышение точности измерений RLC-параметров в широком диапазоне частот при обеспечении высокой чувствительности и быстродействия путем введения эффективных адаптивно-мультипликативных коррекций и режима накопления и формирования результатов после каждого цикла измерений.

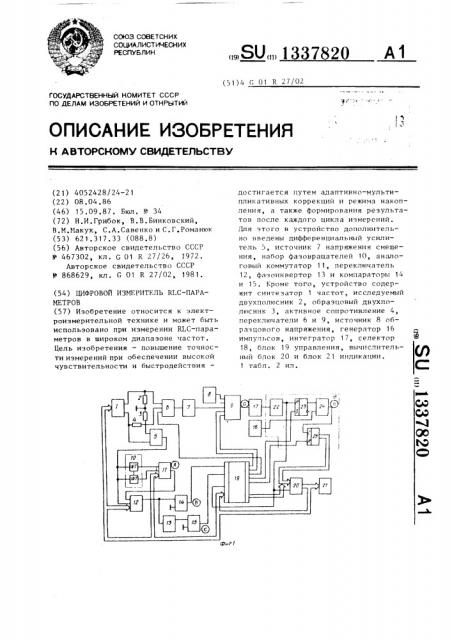

Па фиг. 1 представлена cTpyKTyptta>3 схема цифрового измерителя RJ.Ã-параметров; на фиг. 2 — c.òðóêòóðíaÿ схема блока управления.

Цифровой измеритель И С-параметров содержит синтезатор 1 частот, исследуемый двухполюсник 2, образцовый двухпо.пюсник 3, активное сопротивление 4, дифференциальный усилитель 5, переключатель 6, источник

7 напряжения смещения, источник 8 образцового напряжения, переключатель

9, набор фазовращателей 10, аналоговый коммутатор 11, переключатель !2, фаэоинвертор 13, компараторы 14 и

15, генератор 16 импульсов, интегратор 17, селектор 18, блок 19 управления, вычислительный блок 20 и блок 21 индикации, Селектор 18 состоит из нуль-орга— на 22, триггера 23, элемента 2И 24 и счетчика 25.

1лок 19 управления (фиг. 2) содержит коммутатор 26, формирователь 27, элемент 2 ИЛИ 28, триггеры 29 и 30, - лементы 2И 31- 33„ элемент 2 И. 1È 34, триггер 35, -элеме::. 2 ИЛИ 36, триггер

37, регистр 38, ре; рсивный счетчик

39, элемент 2 1ПИ 4.3, формирователь

41, элемент 2 ИЛИ 42, счетчик 43, триггер 44, дешифратор 45, формирователи 46 и 47, элементы 2 И 111 48 и

49, формирователь 50 и блок )! Ot>poса.

Синтезатор 1 частот первым выходом связан с первым чажимом исследуемого двухполюсника 2 и первым не— подвижным контактом переключателя 6, вторым неподвижным контактом подключенного к точке соединения первого зажима образцового двухпопюсника 3, активного сопротивления 4 и первогo входа дифференциального усилителя 3, второй вход которого подклн)чен к

BTopoMv зажиму активного сопр<тив.те—

7Н "0 2 ния < и вт()р< му 13 lxo, (у синтезатора 1 частот, при «ем 13торые -.эпжимы двухпо:IK)el«I«ho«3 2 и 3 c oå jtntl(íû с корпусом, и п«(нижний к онтпкт переклн>чателя 6

«ере.э источник 7 напряжения смещения свя тпн с третьим tlat lt()j(I3niKI«E III контакт()м 17åðåêní)чптеля 9, второй непoднижный контакт которого остается свободным, и к ттервому подклн>чен выход исTo«It»Ka <3 o«)paattoI3(» o tIattpsteettIlB.

Подвижн««й контакт переключателя 9 соединен через интегратор 17 с первым

1«ходом селектора 18, к второму входу которого подключен выход генератора

16 импулт,сов, и третий и «еттэертый

Bxoj(Bt подключены со; тв Tc TBåíío к пятому и четвертому ьп«хода.(<>:10Ka 19

< с

,> <

3(>

3 а«

<>О управ:тения, K третt,ему 1«ходу которо— го подключен .«ервый Btlxojl селектора

18, второй вых(>д котор< г(> соединен с входной шиной 1<ычислител ьного блока

20, к которой подк II()«et«, кроме того, шест ой выход блока 19 упра(эле«(ия .

Первый выход селектора 18 соединен также с входом управления блока 20.

Выхо.t дифференциального усилителя ) полк тючен к входам набора фачонр.<—

«цателей () и первому II(tlo;(«3««3 ному

Ko1t TaKту переключателя 12, с в т<)ры"-I неподвижным контактом которогo с ое— динен вы::<>д аналогового коммутатора

11 Bxoпены K Kopnvcy < npпвл>«н)1>(««й 13::Очены также упрпвляю«ций вход переKjïî «ателя 12, вхо (блока 2 1 индикации, Bx< jl y««pat)=lett««)I и нплс)гового коммутатора 11 и четвертый вход блока 19 управления. Упрпплян— п(ий вх<)д переключптеля 6 и двп уттравлян)щих входа переключателя 9 сое— динены coo TI1«3:«яется

13378

30

i(t) = I sin t

45 а напРяжения на 2 „ и на 7„ относительно заземленной точки их соединения соответственно будут равны: ход триггера 23 связан с первым входом - лемента И . 4, второй вход которого является вторым входом селектора 18, а выход подк ьючен к входу счетчика 25, вход сброса которого является третьим входом селектора 18, а выход — его вторым выходом.

В блоке 19 управления два входа коммутатора 26 являются соответствен- 10 но первым и вторым входами блока 19.

Первый выход коммутатора 26 соединен с первым входом элемента 2И 31 к второму входу которого подключен выход триггера 30, D-входом связанного с корпусом, а С-входом подключенного к выходу триггера 35, являющемуся первым выходом блока 19 управления,подключенным к входу формирователя 41 и счетчика 43. Выход элемента 2И 31 подключен к входу реверсивного счетчика 39 и С-входам триггеров 35 и 37, D-входы которых соединены с корпусом, причем выход триггера 37 является вторым выходом блока 19 управления. ?.

S-вход триггера 35 подключен к выходу элемента 2 ИЛИ 34, первый вход которого подсоединен к выходу элемента 2И 32, первым входом связанного с инверсным выходом триггера

44, а вторым входом — с вторым выходом коммутатора 26 и первым входом элемента 2И 33, выход которого свя зан с первым входом элемента 2 ИЛИ

36, выходом подключенного к S-входу

35 триггера 37. Вход параллельной установки реверсивного счетчика 39 соединен через регистр 38 с четвертым входом блока 19 управления, а выход перехода через ноль счетчика 39 4п подключен к R-входу триггера 44 и первому входу элемента 2 ИЛИ 42, выход которого соединен с входом установки реверсивного счетчика 39. Прямой выход триггера 44 подключен к второму входу элемента 2И 33. Выходы формирователя 41 и формирователя 50, включенного входом к первому выходу блока 19 управления, являются соответственно пятым и четвертым выходами блока 19 управления. Вход сброса счетчика 43 подключен к выходу элемента 2 ИЛИ 40, первым входом связанного с точкой соединения выхода формирователя 47 и входа элемента 2 ИЛИ

48, к второму входу которого подключен выход формирователя 46. Вход формирователя 46 является выходом состояния "2" дешифратора 45, а вход

1 фс рмпронате: я 47 — вь|ходс м его cnc— тояния "4", Вых 1ды состоянии "1" и

"3" дешпфратора 45 соединены с входами э.цемента 2 И 1И 49, выход которого является третьим выходом блока

19 управления. Второй вход элемента

40 подключен к выходу блока 51 сброса, входу элемента 2 ИЛИ 28 и R-входу триггера 29, D-вход которого связан с его инверсным выходом, при этом прямой и инверсный выходы триггера

29 подключены к управляющим входам коммутатора 26, а С-вход соединен с выходом элемента 2 ИЛИ 48, причем второй вход элемента 2 ИЛИ 28 через формирователь 27 соединен с третьим входом блока 19 управления, а выход элемента 2 ИЛИ 28 соединен с S-входом триггера 30, вторым входом элемента 2 ИЛИ 34, вторым входом элемента 2 ИЛИ 36, вторым входом элемента 2 ИЛИ 42 и 5-входом триггера 44.

Шина состояний "0", " 1", "2", "3" дешифратора 45 является шестым выходом блока 19 управления, а выход счетчика 43 подключен к входу дешифратора 45.

Вычислительный блок 20 является микропроцессорной системой, входная и выходная шины которой являются элементами подсистемы ввода-вывода, а вход управления — входом запроса на прерывание.

Сущность изобретения заключается в следующем °

Если к последовательному соединению образцового 3 (Zо) и исследуе- мого 2 двухполюсников (7„) приложить синусоидальное напряжение, то ток в цепи будет равен:

U>(t) = Т Е„з1п(, t+,)

U,(t) = -I Z,sin(„it+ ч,), где I амплитуда тока в цепи, соответствующие начальные фазы.

Проинтегрировав на интервале от

aT до bT с постоянной времени ",(Т период входного напряжения) суммы напряжений U„(t)+Г, и 11,,(t)+U (U,„ — напряжение смещения) получим:

+ — Б „Т(Ь-а);

ЬТ 1Т

11и « j 1лZîв п(с„ + (о (3 "+" ))см (хт уТ

2? . (Л(Ь-а) . ГсоТ ,= — — sin — * — 2 $3.п(-х-(Ь-а)+(1+

w о (2 о4(+ 1) „Т(Ь-а) .

Рассмотрим случай, когда U< про(г„ порционально Z„sin p„, а Б„ пропоро, ционально -2 sin v . Дпя этого необ о 20 ходимо, чтобы ()Т(Ь+а)

= 0

2 (()Т (Ь-а) sin — ) 0

Отсюда Ъ = -а (оТ (Ь-а) 0t — t л

Учитывая ()Т = 2)(, 0 с -2а))с)( (2) 1 са с0

Выражения (1) и (2) дают правило для определения пределон интегрирования.

Рассуждая аналогично, получим условия когда U пропорционально

40 оx

-Z

Ь = 1-а, (3) 0 (aс

ДЛя UI) - Z„COS (гахн U„-Z,СО$4, необходимо, чтобы (4) 1

Ь ==-а

1 1 — — с а с—

4 4 (6) и для U() Ä -Z cos q è Пс) 2,со$ (( необходимо, чтобы

b = — — — а

2 (7)

Э 1 — с а с ——

4 4 (8) 13378

ЬТ

U„— 1 I Z„sin(wts q,)dt+ -) U,„dt

1 1 вх

UIZ аТ

21,. (T(b-а) . Г ыТ

sin Z„sini (Ь-а)+ Sf+

Uè = a,„+à,Ä 2„sin с „+

Xl

+ Е (; (Z„) + "(2„)j

In-3,3 .. ,„-,„Z„»n V„+ (x7 — х) («)

% 7,4..

" а3,3..

Uu = а +а,„Z sin (Р +

01 о .>» ((z",)+ (z",)) ь= 3,5... а (,„-а1„2»n o +

+ Q ((z"",,) — (z,)7

k 7,4

1ь=35"

U(I = ао„+а1о Z хсо$ (, +

ВХ3

+ (U((z „)+ (z „)7

ks 74

Ь а3,5. ь)() аОи а)() 2 со$ (+ х4

+,С Г "(2",)- (2„)7

ks 7,4 -.

Inа 3,5... а U„+a 1(1 Z () co s Мо +

+, (>(z. )+ (z".)j

Хаг ...

ms),5..

Ug = ио„а), 2осо$ ((+

М о4 о(1 о

Е Г«(2",) — (z,)) (а7,4... (9. 1) (9.2) (9.3) (9.4) (10 ° 1) (10.2) (10. 3) (10.4) tns3,5...

)I где а т

2I„ а

10 л

Д(2«)» о(2 о) нелинейная погрешность интегратора четных степеней, нелинейная погрешность интегратора нечетных степеней. о (2 ) "(2о) Преобразован напряжения (9) и (10) процедурой двухтактного интегрирования в числа импульсов, получим

sð,„„+az„Z „sin (I Äi с Гс((2 „)+I(Z к)3

Хаги...

Ъа3,5.. 1

UOdt = ПСмНь °

-1 о

Учитывая (1) — (8), можно избрать пределы интегрирования для перечисленных случаев.

Пределы интегрирования являются фазовыми значениями в цепи, начальная фаза которого выбрана равной нулю.

Таким образом, выбирая пределы интегрирования, на выходе интегратора можно получить:

133 782О

Г."(Z „) - (Z,)1

1О2,6..

m=3 5 и,о -а„, Z-, sin ц, + (13.4) о о а „+а „Z sin 1.+

kH-." 3

I)(= 3,5...

30 где f — частота заполнения о У вЂ” опорное разрядное напряжение, напряжение смещения нульоргана.

Образуя разности М1-N2, N>-N4, N5 N N7 N и ВычислЯЯ отноше—

1У2

ИИЛ вЂ” ПОЛУ IHM

Updt Uñìíñ у о а()() а ((З1П (ус+ (a(Z")-.и,))—

«Иг, . оли 3, 5

U,de =U о откуда

N,= — (a „-и „)+ — a«Z„sing,+ 20 о о (12.1) 25 (Z cos

К5-Кс

N -N

7 о (Z (12.2) 30 (ип3,5

f, ) — — а,„Z, sin(I,+ о о (12.4) mH3,5 (17) fo

N = — (а

U ou о «=26

+ 6о о (((Z „) + u" (Z „) ), (13. 1) (13.2) «И2 Ф.55 при однородности Е„ и Хо в случае измерения LC-параметров — и от их частоты.

В пределах получения пар результатов (М,,N2), (Ы,, N,), (NÄ N,), rH- :3, 5 — f (Z".). и ™,)) о а(„ о соз Ч, + (13. 3) М11 5 (11)

Х. (d (Z".)+d(Z-))— — Е и(",) Ф3 о

fp f, о о

+ — Q lg(z«Ä)-gz,)); . Up (И -P5...

f, f, N = — (а -U )+ — à Z sin у+

3 U OU (мно U (((о о о

+ — (((2,)+ (Е,)); (12.3)

+ -О.д-, (г(z,) — (г,))

"O «Л2,6... и аналогично для синфаэной составляющей

+ —, (d (Z „) -(Р(Z< )j;

Uo (26

f. f.

N = — (а -U ) — а Z cns u +

Q U о((л(оо (о с, с о ( (Z„sin v„) 2 a„+ о 2/(Z„)

ИУ М1 По (Z(,sin g ) 2 — а т„+ о- Е 2о (Z ) (14) (I ) 2 — а,„+ — 20(Z ) о о

Ч,) 2 а„„+ —, . 2 (Е„)

П î m*35.. (15) Как видим в выражениях (14) и (15); исключены аддитивная составляющая погрешности, а также все нелинейные члены погрешности четных степеней.

Полагая сумму нелинейных членов погрешности нечетных степеней начиная с третьего ничтожно малой, получим

21В1ПИ,-(Е.В1ЛО.) — N (((16)

Nz

Z„cosy„=(Z,сosy ) ()(с

2 «

Следовательно, выполнив измерения для получения N -N и вычислиI тельные операции (16) и (17), можно получить значения синфаэной и квадратурной составляющих исследуемых комплексных двухполюсников. При этом результаты не зависят от f,, U, а,„, 9

133

45 0 0

0 1

1 0

1 1

Нижнее

Среднее

Верхнее

Среднее (N,,11 ) входной измеряемый параметр изменяет только знак, сохраняя неизменным свое абсолютное значение. Это гарантирует стабильность аддитивных погрешностей, поскольку режим работы входных цепей (в частности, обратные токи) не изменяется. Поэтому при образовании разностей N -И N -N з

Nq-Nq» N,-N„ обеспечивается их эффективная коррекция.

Поскольку д я определения N,-NÂ используется процесс двухтактного интегрирования, то для того, чтобы избежать сложностей при определении знака, введено напряжение U,„, смещающее все напряжения в положительную область. Величина Ц на реэультаты измерений не влияет, ее стабильность необходимо обеспечить на время измерений, что просто технически реалиэуется.

Цифровой измеритель RI.Ñ-параметров работает следующим образом, Рассмотрим работу измерителя на произвольной частоте в случае измерения индуктивности двухполюсника, представляемого последовательной RLсхемой замещения, В качестве Z подключается образцовая индуктивность

I., Вектор тока для формирования пределов интегрирования снимается с активного сопротивления 4. Для измерения реактивных составляющих на раэличных частотах фазу управляющего нао пряжения поворачивают на 90 с помощью набора фазовращателей 10, обеспечивающих .стабильность своих характеристик в конкретном диапазоне частот.

С целью увеличения чувствительности на высоких частотах в блоке 19 управления введены регистр 38, реверсивный счетчик 39, элемент 2 ИЛИ 42 и триггер 44, обеспечивающие режим накопления проинтегрированных напряжений, В процессе начальных установок в регистр 38 программно заносится число тактов накопления. Это число заносится в счетчик 39, иэ которого по истечении одного такта вычитается единица. Переходом через "0" счетчика 39 заканчивается цикл накопления, В рассматриваемом примере в счетчик 39 записано число 3. Кроме того, при начальном диалоге вычислительным блоком в синтезатор 1 заносится код частоты и посредством коммутатора 11 вы7820 10 бирается необходимый фазовращатель из набора 10 фазовращателей. При измерении реактивных составляющих переключатель 12 устанавливается в верхнее

> положение.

После начальных установок прогоамма вычислительного блока 20 зацикливается на ожидание внешнего преры»О вания

Из напряжения, пропорционального

Ь» з|п(ыг.+ 1 (точка А), посредством фазоинвертора 13 и компараторов 14 и

15 формируется две последовательности импульсов (В и С), по которым выбираются необходимые пределы интегрирования.

При начальном сбросе (точка D) сбрасываются в нуль счетчик 43 и

2р триггер 29» а триггеры 30, 35, 37 и

44 устанавливаются в "1" по S-входам.

При этом коммутатор 26 соединяет выход компаратора 14 (точка В) с входом элемента 2И 3 1, а выход компара?Ь тора 15 (точка С) — с входами элементов 2И 32 и 33. Если первым приходит импульс. по линии С, то он состояния блока 19 управления не изменяет, поскольку поступает на S-вход находя30 щегося в единичном состоянии триггера 37. Приход первого импульса по линии В после сброса соответствует началу первого такта накопления. Этот импульс через элемент 2И 31 по С-входу записывает в триггеры 35 и 37 нули. Выходы этих триггеров (Е и F) управляют состоянием переключателя

9, для которого таблица истинности имеет вид: г

Е F Положение переключателя

В соответствии с этой таблицей на вход интегратора 17 (после начальных установок переключатель 6 находится в верхнем положении) прикладывается напряжение Zx. Процесс интегрирова13378 код

N ния продолжается до прихода первого импульса по линии С, который установит триггер 37 в единичное состояние и в соответствии с таблицей переклют чатель 9 переведется в среднее положение и прекратится процесс интегрирования, Вновь пришедший импульс по линии В через элемент 2И 31 восстановит нулевое состояние триггера 37, 1О возобновит процесс интегрирования и т.д. Это будет продолжаться до прихода третьего отрицательного фронта на вход счетчика 39 (фиг ° 2 F), по. которому вычтется из него последняя 15 единица, и на его выходе сформируется импульс, переписывающий в реверсивный счетчик 39 вновь число "3", и сбрасывается триггер 44. Тогда через открытый элемент 2И 32, послед- 2р ний в цикле накопления, третий импульс по линии С, воздействуя íà Sвход триггера 35, установит его в "1", чем запретит в соответствии с таблицей, интегрирование, Передний фронт 25 на выходе триггера 35 приведет в нулевое состояние триггер 30, запирающий элемент 2И 31, Это приводит к тому, что описанное состояние блока

19 управления является устойчивым, gp поскольку импульсы ни по линии В, ни по линии С изменить его не могут. В то we время этот передний фронт формирует на выходе формирователя 50 узкий импульс, отпирающий через триг- 35 гер 37 селектор 18. При этом переключатель 9 подключает к входу интегратора 17 разрядное напряжение от источника 8 образцового напряжения.

По истечении первого такта импуль- 4О сом, запирающим триггер 30, записывается единица в счетчик 43, При этом в дешифраторе 45 дешифрируется состояние "1" и через элемент 2 ИЛИ 49 переключатель 6 устанавливается в ниж- 45 нее положение, В момент срабатывания нуль-органа

22 в счетчике 25 накопится число импульсов N) 1, где 1 — число тактов накопления (в данном примере t = 3) (см, также ур-е 12. 1).

20 12

28 возобновляется начальное состояние триггеров 30, 35, 37 и 44, а также производится прерывание программы вычислительного блока 20, по которому он считывает выходной код счетчика

25 и состояние дешифратора 45 для индентификации данных.Код запоминается, после чего возобновляется работа программы ожидания прерывания. Первый же импульс по линии В повторит всю описанную последовательность с той разницей,что на вход интегратора 17 поступает напряжение на Z,. Тогда в соответствии с таблицей и уравнением (12,4) в памяти будет зафиксирован — (а -U ) — — а ы -+

) о 1о о„сммо 11 1() о о о ((г.")- (,))(424.

При этом в дешифраторе 45 активизируется состояние "2", которое формирует на выходе формирователя 46 узкий импульс, изменяющий по С-входу состояние триггера 29. Это, в свою очередь, приводит к перекоммутации коммутатора 26, и импульсы по линии

В поступают на выходы элементов 2И

32 и 33, а импульсы по линии С на вход элемента 2И 3 1. Вследствие этого в третьем и четвертом циклах, в основном аналогичных первому и второму, в память вычислительного блока

20 будут занесены коды

Ы P=) (а -U ) - — а )Ь +

f о

11 оо СМ Но U 1() М о о — ((2,)- (z „))} о 1(=1,4....N) I = 9((a „ -смн ) + — à „L(, + —,) (z(z „) — )(2, )))

"о 4=a 4...

В вычислительном блоке по истечении четырех циклов выполняется операция (см, (16)):

m=),1

N. (= 9 1,— (а,„-U,„„, )+ — a,„Ь„+ — ((z )+t(z,)j) о

При срабатывании нуль-органа 22 формирователем 27 через элемент 2 ИЛИ

Ь =Ь =1 х о )(р

Значение L)(выводится в блок 21 индикации. В памяти вычислительного блока 20 коды N 1, N 1, N 1,,N 1 размещаются в виде четырехкомпонентного вектора, элементы которого воl3 133 эобновляются в каждом цикле иэ четырех описанных. Это позволяет по истечении первых четырех циклов после каждого следующего формировать результат измерений. В самом деле (обозначив вторым индексом порядковый номер результата) уже после пятого цикла в вычислительном блоке 20 вычисляется

1124

N, (— N, после шестого цикла

7820

t)

10 ным контактом второго переключателя, подвижный контакт соединен с входом интегратора, выходом подключенного к входу селектора, к второму входу которого подключен генератор импульсов, первый выход блока управления подключен к входу управления первого переключателя, второй и третий выходы — к управляющим входам второго переключателя, а четвертый и пятый — к управляющим входам селектора, причем выход нуль-органа селектора соединен с третьим входом блока г ггпу г г21 4 х о

31 4"

Nil г Nãт ( х Nçãf после седьмого цикла после восьмого цикла и т.д., т,е. несмотря на наличие принципиально необходимых четырех циклов быстродействие лишь немногим меньше, чем с одним циклом измерения.

При измерениях активных сопротивлений и проводимостей, а также синфаэных составляющих комплексных сопротивлений работа измерителя отличается только тем, что переключатель 12 находится в нижнем положении, а коды, считываемые в память вычислительного блока 20, описываются уравнением (13) Формула изобретения

Цифровой измеритель R1.Ñ-параметров, содержащий синтезатор частот, выходами подключенный к последовательно соединенным клеммам для подключения исследуемого двухполюсника, образцового двухполюсника и активного сопротивления, причем общий вывод исследуемого и образцового двухполюсников подключен к корпусу, общий вывод синтезатора частот и исследуемого двухполюсника соединен с первым неподвижным контактом первого переключателя, второй неподвижный контакт которого подключен к общему выводу соединения образцового двухполюсника и активного сопротивления, а источник образцового напряжения соединен с первым неподвиж15

2г

50 г35 управления и управляющим входом вычислительного блока, к входной информационной шине которого подключены выходная шина селектора и выходная шина блока управления, а к выходной шине вычислительного блока подключен вход блока индикации, о т л и ч а ю шийся тем, что, с целью повышения точности измерений RI,Ñ-параметров в диапазоне частот при обеспечении высокой чувствительности и быстродействия, введены дифференциальный усилитель, источник напряже— ния смещения, набор фазовращателей, аналоговый коммутатор, третий переключатель на два положения, фаэоинвертор и два компаратора, причем дифференциальный усилитель двумя входами подключен параллельно активному сопротивлению, а выходом соединен с входами всех фаэовращателей и первым неподвижным контактом третьего переключателя, причем выходы всех фазовращателей подключены к соответствующим входам аналогового коммутатора, выход которого соединен с вторым неподвижным контактом третьего переключателя, подвижный контакт которого соединен с входами фаэоинвертора и первого компаратора, а выход фазоинвертора через второй компаратор подключен к второму входу блока управления, с первым входом которого соединен выход первого компаратора, причем вторые входы обоих компараторов соединены с корпусом, а выходная шина вычислительного блока подключена к входам управления синтезатора частот, третьего переключателя, аналогового коммутатора и к четвертому входу блока управления, причем источник напряжения смещения включен между подвижным контактом первого переключателя и третьим неподвижным контактом второго переключателя.

1 3 37820

Составитель H.ÌèõàëåB

Редактор Л.!3ежнина Техред M.Ходанич Корректор А.Тяско

Заказ:«1. 7/4-« Тираж 730 Подписное !

3!33!3!!!!! осударственного комитета СССР по делам изобретений и открытий

11303>, Москва, Ж-35, Раушская наб., д, 4/5 !!!«п««в, п«т««.:«в — т«опиграфическое предприятие, г. Ужгород, у:r. !!роектная, 4