Синтезатор частот

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и обеспечивает уменьшение уровня помех. Синтезатор содержит накапливающие сумматоры (НС) 1 и 11, регистр 2 памяти, мультиплексор 3, ЦАП 4, интегрирующее звено 5, пороговый злемент 6, формирователь 7 импульсов коммутации,злемент 8 разряда,блок 9умножения и деления (БУД) и сумматор 10кодов. На кодовые входы БУД 9 поступают числа q-1, b, а. Число а задает значение выходной частоты согласно соотношению f, , число b задает значение шага сетки частот /) f fp/b, - количество разрядов входного кода ЦАП 4. БУД 9 выдает частное х и остаток 4х. НС 11 преобразовывает остаток Зх в импульс переполнения. Число х, сформированное сумматором 10, задает емкость НС 1. НС 1 формирует ступенчатую пилообразную функцию x(t).Остаток x.(t) при переполнении НС 1 записывается в регистр 2 по импульсу переполнения p(t). В зависимости от состояния НС 1 формирователь 7 обеспечивает прохождение через мультиплексор 3 одного из чисел: число О - во время действия импульса переполнения , число Xj,(t) - на следующем после переполнения такте опорной импульсной последовательности, число (q-1) - на последующих тактах до переполнения НС 1. 1 ил. (Л Сдд со со со

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 Н 03 В 19 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ

g-l

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4034842/24-09 (22) 12 ° 02.86 (46) 15.09,87. Бюл. У 34 (75) В.И. Козлов и В,И. Никифоров (53) 62 1.373.42(088.8) (5e) Авторское свидетельство СССР

N- 978314, кл. Н 03 В 19/00, 12.01.81.

Авторское свидетельство СССР

11 1256132, кл. Н 03 В 19/00, 09.04.85. (54) СИНТЕЗАТОР ЧАСТОТ (57) Изобретение относится к радиотехнике и обеспечивает уменьшение уровня помех. Синтезатор содержит накапливающие сумматоры (НС) 1 и 11, регистр 2 памяти, мультиплексор 3, ЦАП 4, интегрирующее звено 5, пороговый элемент 6, формирователь 7 импульсов коммутации, элемент 8 разряда, блок

9 умножения и деления (БУД) и сумматор

10 кодов. На кодовые входы БУД 9 поступают числа q-1, b, а. Число а задает значение выходной частоты f<

„„SU„„1337990 А1 согласно соотношению f = à fo/b, число Ь задает значение шага сетки частот d f = fo/Ь, q 2 " — количество разрядов входного кода ЦАП 4. БУД 9 выдает частное х0 и остаток х. НС

11 преобразовывает остаток х в импульс переполнения, Число х, сформированное сумматором 10, задает емкость НС 1. НС 1 формирует ступенчатую пилообразную функцию х„().Остаток х (t) при переполнении НС 1 за2 писывается в регистр 2 по импульсу переполнения p(t), В зависимости от состояния НС 1 формирователь 7 обеспечивает прохождение через мультиплексор Э одного из чисел: число 0 во время действия импульса переполнения, число х2(С) — на следующем после переполнения такте опорной импульсной последовательности, число (q-1) на последующих тактах до переполнения НС 1. 1 ил.

45

1 133799

Изобретение относится к радиотехнике и может использоваться в приемопередающей и измерительной аппаратуре.

Цель изобретения — уменьшение с, уровня помех.

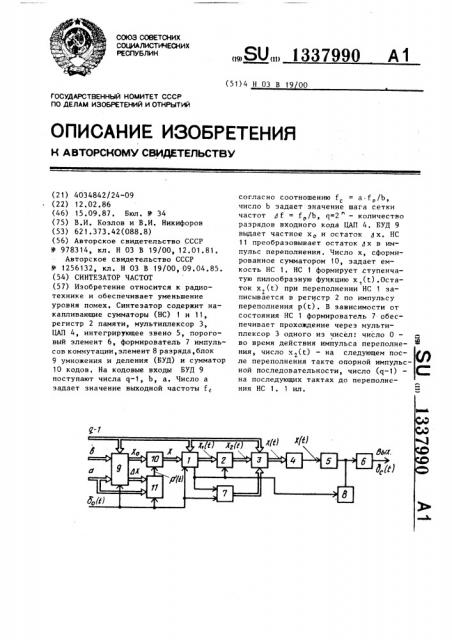

На чертеже представлена электрическая структурная схема синтезатора частот.

Синтезатор частот содержит первый накапливающий сумматор (НС) 1, регистр 2 памяти, мультиплексор 3, цифроаналоговый преобразователь (ЦАП) 4, интегрирующее звено 5, пороговый элемент 6, формирователь 7 импульсов коммутации, элемент 8 разряда, блок 9 умножения и деления, сумматор 10 кодов, второй НС 11, Синтезатор частот работает следующим образом.

На первый, второй и третий кодовые входы блока 9 умножения и деления,тактируемого импульсной последовательностью ",(t) с частотой 1, поступают соответственно числа (q-1), Ь и а и где q=2 количество разрядов входного кода ЦАП 4, число Ь задает значение шага сетки частот LIf = f,/Ъ, число а задает значение выходной частоты f согласно соотношению f =а1 /Ь, Блок 9 умножения и деления обеспечивает формирование числа x=b(q-1) /а, поступающего на второй вход первого

НС 1 и определяющего его емкость, и выдает частное х и остаток Llx на первом и втором выходах соответствен35 но.

Второй НС 11, емкость которого устанавливается числом а, преобразовывает остаток х на его втором входе в импульс переполнения р (t). Число

1 х формируется в виде суммы х=х +р„ (t) в сумматоре 10. Далее число х поступает на второй вход первого НС 1, задавая его емкость. Код числа (q-1) поступает на первый вход первого НС

1, который тактируется опорными импульсами c",(t), Первый НС 1 формирует ступенчатую пилообразную функцию х,(t), величина приращений которой на каждом такте опорной импульсной последовательности d (t) равна (q-1), Остаток х (t) при переполнении первого НС 1 записывается в регистр 2 с помощью импульса переполнения p(t).

Остаток x„(t) и число (q-1) поступают на входы мультиплексора З,управляемого формирователем 7, Управляю0 2 щий сигнал на выходе формирователя 7 представляет собой логические уровни на шине данных, зависящие от состояния первого НС 1, и обеспечивает прохождение через мультиплексор 3 на вход ЦАП 4 одного из трех чисел: числа 0 — во время действия импульса переполнения; числа x (t) — на следующем после переполнения такте опорной импульсной последовательности d0(t); числа (q-1) — на последующих тактах до переполнения первого НС 1.

Формирователь 7 может быть выполнен, например, в виде последовательно соединенных D-триггера и элемента

ИЛИ-НЕ (на чертеже не показано). Выход импульсов переполнения первого

НС 1 подключен к информационному входу D-триггера и к второму входу элемента ИЛИ-НЕ, а тактовый вход D-триггера подключен к опорному входу синтезатора частот. Управляющие сигналы на мультиплексор 3 снимаются с выходов D-триггера и элемента ИЛИ-НЕ.

ЦАП 4 преобразовывает входную последовательность чисел x(t) в последовательность выходных напряжений.При этом на вход интегрирующего звена 5 поступают квантованные по уровню и времени значения сигнала.

На первом интервале времени элемент 8 разряда, управляемый импульсом переполнения p(t) первого НС 1, производит разряд и установку интегрирующего звена 5 в исходное нулевое состояние ° В течение второго и третьего временных интервалов напряжение на выходе интегрирующего звена

5 возрастает пропорционально числам х () и (q-1) соответственно, В результате сигнал U(t) на выходе интегрирующего звена 5 по форме представляется отрезками прямых линий, причем на третьем временном интервале сигнал имеет постоянный наклон, так как (q-1) число постоянное.

Значения функции V(t), взятые на третьем интервале, повторяются с периодом Т = Т, х/(q-1) = Т Ь/а, где

Т, = — — период опорной импульсной

fo последовательности d, (t), Поэтому частота HMIlvJIbcoB Pc(t) на выходе порогового элемента 6 постоянна и равна

f0,a/Ь. Шаг сетки частот йГ

f,/Ь задается, таким образом, выбором значений опорной частоты f u теля импульсов коммутации и с тактовым входом регистра памяти и подклюc((q-2) T, U М (1-1) K-17 T вателя импульсов коммутации и являго накапливающего сумматора и является входом первого перемножаемого сигнала синтезатора частот, второй вход блока умножения и деления являФор мул аизобретения умножения и деления и подключен к опорному входу синтезатора частот.

Ковалев ич Корректор И. Муска

Заказ 4141/52 Тираж 901

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 13379 числа h, а выходная частота f, — числом а.

В качестве порогового элемента 6 можно, например, использовать последовательно соединенные триггер Шмид5 та и одновибратор (на чертеже не показано) . Поскольку значение остатка х1() от цикла к циклу изменяется в диапазоне значений от 0 до (q-2), соответственно изменяются начальное и конечное значения функции 0(с) на третьем временном интервале. Поэтому порог U срабатывания порогового элемента 6 необходимо выбирать в диапазоне 15 где — произведение коэффициентов преобразования ЦАП 4 и ин- 20 тегрирующего звена 5;

K=ent(x/(q-1)) — целая часть отношения величины емкости х первого НС 1 к входному числу (q-1) . 25

Размах процесса x(t) на входе ЦАП

4 постоянен (не зависит от выбранного значения f ) и равен (q-1), что соответствует максимальному уровню сигнала на выходе ЦАП 4. В этом слу- 30 чае полностью используется амплитудно-кодовая характеристика ЦАП 4 и, следовательно, влияние его нелинейности на ухудшение соотношения сигнал/ помеха минимально. При достаточно большом количестве разрядов ЦАП 4, когда можно считать, что (q-1) q, блок 9 умножения и деления упрощается, причем делимым является число Ь, сдвинутое на и разрядов в сторону 4р старшего разряда. На первом входе первого НС 1 действует в этом случае число q представляющее собой единицу в п-м, считая от старшего, разряде. 45

Синтезатор частот, содержащий последовательно соединенные первый íà- 5р

Составитель Ю.

Редактор М. Дылын Техред И.Попов

90 4 к аплин ающий сумматор, ре гис тр памяти, мультиплексор, цифроаналоговый преобразователь, интегрирующее неH(и пороговый элемент, а также элемент разряда и формирователь импульсов коммутации, при этом первый вход первого накапливающего сумматора объединен с вторым входом мультиплексора> управляющий вход элемента разряда объединен с первым входом формировачен к выходу переполнения первого накапливающего сумматора, сигнальный вход элемента разряда соединен с выходом интегрирующего звена, тактовый вход первого накапливающего сумматора объединен с вторым входом формироется опорным входом синтезатора частот, выход формирователя импульсов коммутации подключен к управляющему входу мультиплексора, о т л и ч а ю шийся тем, что, с целью уменьшения уровня помех, в него введены блок умножения и деления и последовательно соединенные второй накапливающий сумматор и сумматор кодoR,Bbl ход которого подключен к второму входу первого накапливающего сумматора, первый вход блока умножения и деления объединен с первым входом первоется входом второго перемножаемого сигнала синтезатора частот, третий вход блока умножения и деления соединен с первым входом второго накапливающего сумматора и является входом сигнала делимого синтезатора частот, первый и второй выходы блока умножения и деления подключены соответственно к первому входу сумматора кодов и к второму входу второго накапливающего сумматора, тактовый вход которого объединен с тактовым входом блока