Многовходовый д-триггер

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано при построении параллельных регистров , реверсивных сдвигающих регистров, счетчиков с адресной записью, многофункциональных регистров на КМДП-транзисторах. Цель изобретения - повышение быстродействия и расширение области применения достигается путем использования D-триггера с бистабильной ячейкой с отключаемой обратной связью и входных логических элементов , соединенных по схеме Монтажное ИЛИ. Многовходовый D-триггер содержит схему управления и Гь-триггер 1 , К шин 2 синхронизации, К информационных пшн 3, прямую выходную 4 и инверсную выходную 5 шины, шины 6 и 7 питания и общую, К логических элементов 8 с тремя состояниями, инверторы 9 и 10, транзисторы 11 и 12, элемент ИЛИ-НЕ 13. В режиме записи инвертор 1Q D-триггера 1 отключается от цепи питания. При наличии на всех К шинах 2 синхронизации сигналов с уровнем О устройство находится в режиме хранения. При этом элементы 8 с тремя состояниями отключаются от цепи питания. 1 ил. i (Л . л. л. -П. / / /- X./.X. СО 00 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1 А1 (19) (11) (51) 4 Н 03 К 3 3

ОПИСАНИЕ ИЗОБРЕТЕНИЯ л л

П.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4043238/24-21 (22) 24.03.86 (46) 15.09.87. Бюл. М 34 (72) А.E. Заболотный, В.А. Максимов и Я.Я. Петричкович (53) 621.374(088.8) (56) Авторское свидетельство СССР

У 1138930, кл. Н 03 К 3/286, 1983.

Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. M.: Сов. радио, 1975, с. 124, рис. 3.40,б. (54) МНОГОВХОДОВЫИ D-ТРИГГЕР (57) Изобретение относится к импульсной технике и может быть использовано при построении параллельных регистров, реверсивных сдвигающих регистров, счетчиков с адресной записью, много— функциональных регистров на КМДП-транзисторах. Цель изобретения — повышение быстродействия и расширение области применения достигается путем использования D-триггера с бистабильной ячейкой с отключаемой обратной связью и входных логических элементов, соединенных по схеме "Монтажное

ИЛИ . Многовходовый Р-триггер содержит схему управления и D-триггер 1, К шин 2 синхронизации, К информационных шин 3, прямую выходную 4 и инверсную выходную 5 шины, шины 6 и 7 питания и общую, К логических элементов 8 с тремя состояниями, инверторы 9 и 10 транзисторы 11 и 12, элемент ИЛИ вЂ 13. В режиме записи инвертор 10 D-триггера 1 отключается от цепи питания. При наличии на всех с ф

К шинах 2 синхронизации сигналов с уровнем 0 1 устройство находится в режиме хранения. При этом элементы 8 с тремя состояниями отключаются от це- С пи питания. 1 ил.

1 338015

20

2В

ИЛИ-НЕ, прямой и инверсный выходы

Корректор Л. Бескид ар

Заказ 4142/53 Тираж 501 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Изобретение относится к импульсной технике и может быть использовано при построении параллельных регистров, реверсивных сдвигающих регистров, счетчиков с адресной записью, многофункциональных регистров АЛУ на КМДПтранзисторах.

Цель изобретения — повышение быстродействия, расширение области применения достигается путем использования D-триггера с бистабильной ячейкой с отключаемой обратной связью и входных логических элементов, соединенных по схеме пМонтажное ИЛИ .

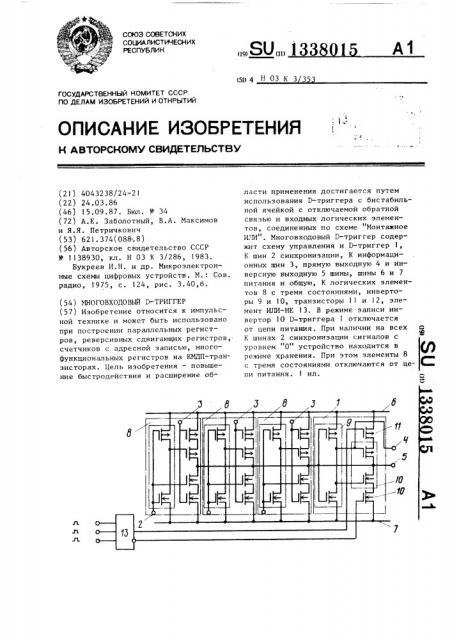

На чертеже представлена принципиальная электрическая хема предлагаемого устройства.

Многовходовый 0-триггер на КМДПтранзисторах содержит схему управления и D-триггер 1, К шин 2 синхронизации, К информационных шин 3, прямую выходную шину 4, инверсную выходную шину 5, шину 6 питания, общую шину 7, К логических элементов 8 с тремя состояниями, выходы которых соединены со входом Р-триггера 1, построенного на бистабильном кольце на первом 9 и втором 10 инверторах, исток р-транзистора инвертора 10 соединен со стоком р-транзистора 11, исток которого соединен с шиной 6 питания, исток и-транзистора инвертора

10 соединен со стоком п-транзистора 12, исток которого соединен с общей шиной 7, ши,ны 2 синхронизации соединены с соответствующими входами К-входового элемента ИЛИ-НЕ 13, прямой и инверсный выходы которого соединены соответственно с затворами р- и и-транзисторов 11 и 12, К-я шина 2 синхронизации соединена с входом управления К-го логического элемента с тремя состояниями, К-я информационная шина 3 соединена с информационным входом К-го логического элемента 8 с тремя состояниями.

Устройство работает следующим образом.

При подаче на К-ю шину 2 синхроСоставитель

Редактор Н. Киштулинец Техред В.Кад низации сигнала с уровнем "I" разрешается запись информационного сигнала с К-й информационной шины 3 в Dтриггер 1. В режиме записи инвертор 10 D-триггера 1 отключается от цепей питания, таким образом размыкается ОС триггера и интенсифицируются переходные процессы. При наличии на всех К шинах 2 синхронизации сигналов с уровнем "0" устройство находится в режиме хранения, причем элементы 8 с тремя состояниями отключены от цепи питания.

Формула изобретения

Многовходовый D-триггер на КМДПтранзисторах содержит схему управления, D-триггер, К-входовый элемент

ИЛИ-НЕ, К шин синхронизации, К информационных шин, прямую выходную шину, инверсную выходную шину, шину питания, общую шину, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия и расширения области применения, схема управления содержит К логических элементов с тремя состояниями, а элемент ИЛИ-НЕ дополнен прямым выходом, выходы которых соединены с входом D-триггера, построенного на бистабильном кольце на первом и втором инверторах, исток р-транзистора второго инвертора Р-триггера соединен со стоком р-транзистора D òðèãгера, исток которого соединен с шиной питания, исток и-транзистора второго инвертора D-триггера соединен со стоком и-транзистора D-триггера, исток которого соединен с общей шиной, шины синхронизации соединены с соответствующими входами К-входового элемента которого соединены соответственно с затворами р- и и-транзисторов D-триг45 гера, К-я шина синхронизации соединена с входом управления К-го логического элемента с тремя состояниями, К-я информационная шина соединена с информационным входом К-го логического элемента с тремя состояниями.

А. Кабанов