Устройство для кодирования аналоговой информации

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике. Его /7 оиспользование в системах преобразования и передачи информации позволяет повысить информативность устройства. Устройство для кодирования аналоговой информации содержит дельта-модулятор 1, логические блоки 2, 3, реверсивный счетчик 5, блок 8 сравнения и триггер 11. Благодаря введению реверсивных счетчиков 6, 7, блока 4 уп равления, блока 9 сравнения и регистра 10 в устройстве осуществляется адаптивная дискретизация входного сигнала, близкая к оптимальной, обеспечивающая более высокий коэффициент сжатия данных. 2 -з.п. ф-лы, 6 ил. ./4 § (Л 00 00 о 4;

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (Я) 4 Н 03 М 7/38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСВ ВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4046773/24-24 (22) 31.03.86 (46) 15.09.87. Бюл. М 34 (71) Московский авиационный институт им. Серго Орджоникидзе (72) А.З,Ходоровский (53) 621.376.5(088,8) (56) Г1атент США У 3795900, KJI H 03 К 13/22, опублик. 1974 °

Авторское свидетельство СССР

108!789, кл. Н 03 M 3/04, 1982. (54) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ АНАЛОГОВОЙ ИНФОРМАЦИИ (57) Изобретение относится к автоматике и вычислительной технике. Его

„„SU„„1338074 А1 использование в системах преобразования и передачи информации позволяет повысить информативность устройства.

Устройство для кодирования аналоговой информации содержит дельта-модулятор 1, логические блоки 2, 3, ревер сивный счетчик 5, блок 8 сравнения и триггер ll. Благодаря введению реверсивных счетчиков 6, 7, блока 4 уп равления, блока 9 сравнения и регистра 10 в устройстве осуществляется адаптивная дискретизация входного сигнала, близкая к оптимальной, обеспечивающая более высокий коэффициент сжатия данных. 2 .з.п. ф-лы, 6 ил.

1338074

Изобретение относится к автоматике и нычислительной технике и может применяться в системах преобразования и передачи информации.

Цель изобретения — повышение ин5 формативности устройства путем увеличения коэффициента сжатия кодированных данных.

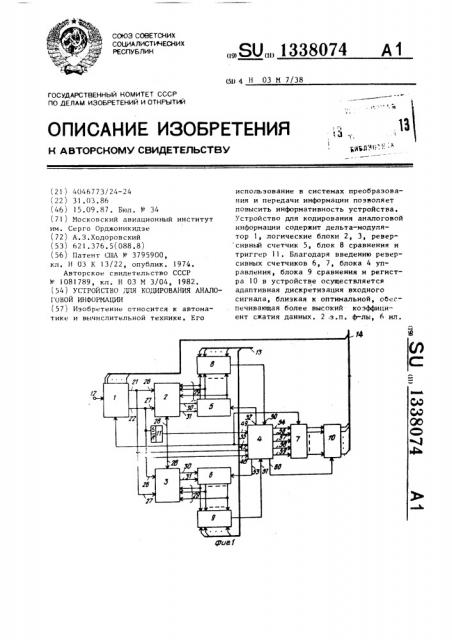

На фиг. 1 изображена блок-схеМу предлагаемого устройства; на фиг.2 дельта-модулятор; на фиг. 3 — логический блок; на фиг. 4 — блок управления; на фиг. 5 — пример реализации третьего реверсивного счетчика; на фиг. 6 — временные диграммы работы устройства.

Устройство для кодирования аналоговой информации содержит дельта-модулятор 1 первый 2 и второй 3 логи I

20 ческие блоки, блоки 4 управления, первый 5, второй 6 и третий 7 реверсивные счетчики, первый 8 и второй 9 блоки сравнения, регистр 10 и триггер

11. На блок-схеме (фиг, 1) обозначены также информационный вход 12, установочные входы 13 и выходы 14 устройства.

Дельта-модулятор 1 идентичен дельта-модулятору устройства-прототипа и включает н себя (фиг. 2) компа30 ратор 15, генератор 16 импульсов, квантователь 17, реверсивный счетчик

18, цифроаналоговый преобразователь (ЦАП) 19 и регистр 20. На фиг, 2 обозначены также первый 21 и второй 22 35 выходы дельта-модулятора l.

Логические блоки 2 и 3 имеют одинаковое выполнение (фиг. 3) и включают в себя каждый элемент ИЛИ 23, первый 24 и второй 25 элементы И. На фиг, 3 обозначены первый 26, второй

27, третий 28 и четвертый 29 входы, первый 30 и второй 31 выходы.

Блок 4 управления выполнен (фиг.4) на первом — третьем одновибраторах 45

32-34, триггере 35, первом — пятом элементах 36-40 задержки, первом и втором элементах ИЛИ 41, 42, первом— третьем элементах И 43-45 и элементе 46 ЗАПРЕТ, на фиг. 4 обозначены 50 перный — пятый входы 47-51 и первый девятый выходы 52-60 блока.

Третий реверсивный счетчик 7 может быть выполнен в соответствии с фиг. 5. Каждый иэ разрядов 61-65 55 счетчика включает в себя триггер 66 и первый элемент ИЛИ 67, а старший разряд 65 — второй 68 и третий 69 элементы ИЛИ. Каждый (кроме младшего) из разрядов 62-65 включает также первый 70 и второй 71 элементы И. На фиг. 5 обозначены вход 72 обнуления, установочный нход 73, первый 74 и второй 75 суммирующие входы, первый

76 и второй 77 вычитающие входы, Такое выполнение счетчика 7 обеспечивает суммирование и вычитание не только как в обычном реверсивном счетчике, но и (при необходимости) отдельно в трех старших разрядах.

Устройство для кодирования аналоговой информации работает следующим образом.

В исходном состоянии триггер 11, первый, второй и третий реверсивные счетчики 5-7, а также реверсивный счетчик 18 дельта-модулятора .1 находятся в нулевом состоянии. Цепи начального обнуления не показаны, Весь процесс функционирования состоит иэ двух режимов — режима начальной отработки (интервал t t, на фиг. 6) и режима слежения С t На участке

1 начальной обработки на суммирующий вход реверсивного счетчика 18 поступают импульсы с первого выхода квантователя 17, в результате чего на выходе цифроаналогового преобразователя 19 формируется ступенчато нара+ стающий сигнал x(t) (фиг ° ба). На первом выходе 21 дельта-модулятора 1 формируется последовательность импульсов (фиг. бб). В режиме начальной отработки первый — третий реверсивные счетчики 5-7 остаются в нулевых состояниях.

Процесс увеличения кода, записанного в реверсивном счетчике 18, продолжается до момента появления первого импульса на нтором выходе квантователя 17 (фиг. бв), соответствующего первому отрицательному перепаду функции х(С) (момент времени

t на фиг. 6), Этот импульс с второго выхода 22 дельта-модулятора 1 поступает íà S-вход триггера 11, переводя его в единичное состояние (фиг, бг), Положительным перепадом напряжения с выхода триггера ll, поступающим на третий вход 49 блока 4 управления, запускается второй одновибратор 33 этого блока, формирующий импульс (фиг. бд), который с выхода

55 блока 4 управления поступает на управляющий вход дельта-модулятора

l и на установочный вход 73 третьего счетчика 7.

1338074 4 дельта-модулятора 1 в момент времени

С, поступает через открытый элемент

И 24 первого логического блока 2 на суммирующий вход первого реверсивно-! го счетчика 5. Если же в момент появляется импульс на втором выходе

22 дельта-модулятора l то через открытый элемент И 24 второго логического блока 3 он поступает на суммиl0 рующий вход второго реверсивного счетчика 6. Одновременно эти импульсы через открытые второй 44 и второй 45 элементы И блока 4 управления поступают ма первый суммирующий или на

15 первый вычитающий входы третьего реверсивного счетчика 7. Обозначим логические переменные, соответствующие появлению импульсов на втором выходе

22 дельта-модулятора 1 через b ., а на первом выходе 21 — через b,. Тогда процесс формирования текущего значения числа в первом реверсивном счетчике 5, можно представить рекуррентным выражением вида:

В результате в регистре 20 дельта модулятора 1 фиксируется код числа, содержащегося в реверсивном счетчике

18. 11олученный код с выходов регистра 20 дельта-модулятора 1 поступает на выходную шину 14 устройства. Одно временно в третий реверсивный счетчи

7 заносится код отрицательного значения допустимой ошибки представлени (апертуры) — 1". ° Отрицательные числа представляются в третьем реверсивном счетчике 7 в дополнительном коде. Be личина апертуры выбирается равной целой степени числа два, т ° е, равна

1Ю

2 дискрет, где m — целое число. При этом разрядность и первого 5 и второ го 6 реверсивных счетчиков должна равняться п=тп+2, а третьего реверсив ного счетчика 7 — n+l. При этом на входе 13 устаггавливается код удвоенной величины апертуры, т.е. код чисrn+ 1 ла 2, Дополнительный код апертуры записывается в реверсивном счетчике

7 путем перевода триггеров 66 в единичное состояние сигналом, подаваемым на вход 73. Начиная с этого момента, устройство работает в следящем режиме и обесггечг вает кодирование разностей между ординатами отрезков ступенчатого полинома, близкого к поли30 ному наилучшего равномерного приближения входного сигнала x(t). В соотВетствии с теоремой Чебышева ординаты отрезков наилучшего приближения х(С) 5

35 В этих выражениях а и а — cock тояния триггеров k-x разрядов первого 5 и второго 6 реверсивных счетчиков соответственно.

Аналогичное выражение для тре40 тьего реверсивного счетчика 7 записывается в виде:

Нюкггий индекс i в обозначении моментов времени t., указывает на номер

1 интерваЛа аппроксимации, а верхний индекс,j — - на порядковый номер очеред ного импульса на выходах 21 или 22 дельта-модулятора 1 на данном интервале аппроксимагГии (С;, t .,,). Определение моментов окончания интервалов аппроксимации осуществляется с помощью реверсивных счетчиков 5 и 6, а кодирование разностей между значени- 50

1 ями ординат отрезков полинома на данном и предыдущем интервалах аппроксимации обеспечивается третьим реверсивным счетчиком 7. Единичный потенциал с выхода триггера 11, подаваемый на входы 28 первого и второго логических блоков 2 и 3, открывает по одному из входов элемента И 24, 25. Очередной импульс с выхода 21

Ь, N, =(b b, ebb; ) 2 (— 1)+, (— 1), (4), =!

45 должны удовлетворять на интервалах с 0 аппроксимации (С,-, С;„ 1 условию:

x(t)=мин x(t)+h=ìàêñ x(t)-h, (-;, = ...

1манс

115=, (Ь! -Ь (а у а - у... га „)), (2) а во втором реверсивном счетчике

6 — в виде:

Ь =, (пг.- - (а v i...íà )) . (Э) г

В момент времени, когда код в одном из реверсивньгх счетчиков 5 или 6 становится равен пороговому коду, на выходе соответствующего блока 8 или 9 сравнения формируется импульс, который поступает на четвертый 50 или пятый 51 входы блока 4 управления соответственно. При этом блок 4 управления при условии Ь, г . Ч1 b

=1, формирует импульс коррекции кода в реверсивном счетчике 7, который появляется на выходе 57, если t .=0 (фиг, бе), и на выходе 59, если, =1 (фиг. 6ж). В первом случае в соответ1338074 ствии с выражением (4) число в третьем реверсивном счетчике 7 увеличиFnw I вается на 2 единиц, а во втором— уменьшается на 2

Увеличение кода производится путем подачи импульса с выхода 57 блока 4 управления на второй суммирующий вход 75 третьего реверсивного счетчика 7. При вычитании импульс с выхода 59 блока 4 управления подается на второй вычитающий в-.од 77 счетчика 7.

Для запоминания и хранения на интервале аппроксимации значения перео менной о, используется триггер 35 блока 4 управления. !!осле коррекции с задержкой, достаточной для изменения кода в реверсивном счетчике 7, на выходе 60 блока 4 управления появ?О ляется импульс, которым в регистре !

О фиксируется очередное значение раэностного кода, поступающего на выходы 14,фиг. 6з). Одновременно импульсами с выходов 52 и 53 блока 4 управления обнуляются реверсивные счетчики 5 и 6, а в триггер 35 заносится значение переменной Ь . =1. """, Затем со сдвигом во времени, определяемым постоянной времени пятого

30 элемента 40 задержки, на выходе 54 блока 4 управления появляется импульс, которым обнуляется третий реверсивный счетчик 7. Далее весь процесс повторяется.

Рассмотрим для примера работу уст- 35 ройства, когда допустимая ошибка приближения выбрана равной двум дискретам. В этом случае разрядность первого 5 и второго 6 реверсивных счетчиков должна равняться трем, а разрядность третьего реверсивного счетчика 7 — четырем. Ila установочные входы 13 подается код числа 4. Данный пример поясняется диаграммой на фиг. 6. Начальный код, устанавлива- 45 емый в третьем реверсивном счетчике о

7 в момент t„, равен Olli. Здесь младший разряд кода записан слева.

Старший разряд кода указывает на знак числа, содержащегося в счетчике 50

7 ° Он равен единице, если число отрицательное, и нулю, если — положительное ° Импульсы с выхода 21 дельта-модулятора 1 в моменты времени ь

1 >

t,, соответствующие положительным 55 перепадам ступенчатой функции х(t) поступают на суммирующий вход первого реверсивного счетчика 5, увеличивая каждый раз его содержимое на единицу. Одновременно происходит увеличение числа, записанного в третьем реверсивном Вто рой реверсивный счетчик 6 остается в нулевом состочнии, так как элементы И 24 и 25 логического блока 3 закрыты, Изменение чисел в реверсивных счетчиках 5-7 в процессе работы устройства показаны в таблице, где приведены также текущие значения кода в третьем реверсивном счетчике 7 и выходной код устройства, формируемый после окончания очередного интервала аппроксимации. г

Таким образом, предлагаемое устройство осуществляет адаптивную дискретизацию входного сигнала с использованием алгоритма сжатия данных на основе интерполятора нулевого порядка и кодированием разностей между ординатами отрезков, близких к отрезкам наилучшего равномерного приближения °

IIo сравнению с методом сжатия, реализованном в прототипе, данный алгоритм обеспечивает для широкого класса процессов в 3-5 раз более высокие коэффициенты сжатия данных, обеспечивая значительное сокращение объемов формируемых сообщений, что позволяет более эффективно использовать пропускную способность каналов передачи информации, уменьшить объемы памяти регистрирующих и запоминающих устройств, Ф о р м у л а и з о б р е г е н н я

I,Устройство для кодирования аналоговой информации, содержащее дельтамодулятор, первый выход которого соединен с первым входом первого логического блока, первый выход которого подключен к входу суммирования первого реверсивного счетчика, выходы которого соединены с первыми входами первого блока сравнения, второй выход дельта-модулятора соединен с вторым входом первого логического блока, Г-входом триггера и первым входом второго логического блока, второй вход которого подключен к первому выходу дельта-модулятора, выход триггера соединен с третьими входами первого и второго логических блоков, первый вход дельта-модулятора является информационным входрм устройства, вторые входы первого блока сравнения являются установочными входами устройства, третьи выходы дель133807÷ та-модучятора являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения информативности устройства, B него введены регистр, второй блок сравнения, второй и третий реверсивные счетчики и блок управления, первый и второй выходы которого соединены с входами обнуления соответствующих-реверсивных счетчиков, четвертые входы и второй выход первого логического блока подключены соответственно к выходам и нычитающему входу первого реверсивного счетчика, первый и второй выходы второго логического блока соеl0 динены соответственно с суммирующим и вычитающим входами второго реверсивного счетчика, выходы которого подключены к соответствующим четвертым 2р входам второго логического блока и первым входам второго блока сравнения, вторые входы которого подключены к соответствующим установочным входам устройства, первый, второи и третий 25 входы блока,правления подключены соответственно к первому и второму выходам дельта-модулятора и выходу триггера, выходы первого и второго блоков сравнения соединены соответст- 3Q венно с четвертым и пятым входами блока управления, третий выход которого соединен с входом обнуления третьего реверсивного счетчика, четвертый выход блока управления подключен

35 к установочному входу третьего реверсивного счетчика и управляющему входу дельта-модулятора, пятый — восьмой выходы блока управления соединены соответственно с первым и вторым

40 суммирующими и первым и вторым вычитающими входами третьего реверсивного счетчика, выходы которого подключены к информационным входам регистра, девятый выход блока управления

45 соединен с управляющим входом регистра, выходьt которого подключены к выходам устройства.

2. Устройство по и ° 1, о т л ич а ю щ e e с я тем, что логический блок выполнен на первом и втором элементах И и элементе ИЛИ, выход которого соединен с первым входом второго элемента И, первый вход первого и второй вход второго элементов

И являются соответственно первым и вторым входами логического блока,второй вход первого и третий вход второго элементов И объединены и являются третьим входом логического блока, входы элемента ИЛИ являются четвертыми входами логического блока, выходы первого и второго элементов И являются соответствующими выходами логического блока.

3, Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок управления выполнен на триггере, элементах задержки, элементах ИЛИ, элементах И, элементе ЗАПРЕТ и одновибраторах, выход первого одновибратора соединен с входами первого и второго элементов задержки, выход первого элемента задержки подключен к первым входам первого и второго элементов

ИЛИ, выход второго элемента задержки соединен с первым входом первого элемента И, выход второго одновибратора ! подключен к второму входу первого элемента ИЛИ, выход которого соединен с Б-входом триггера, выход которого подключен к второму входу первого элемента И и запрещающему входу элемента ЗАПРЕТ, выход третьего одновибратора соединен с входами третьего и четвертого элементов задержки, выход третьего элемента задержки подключен к S-входу триггера и второму входу второго элемента ИЛИ, выход которого соединен с входом пятого элемента задержки, выход четвертого элемента задержки соединен с разрешающим входом элемента ЗАПРЕТ, первые входы второго и третьего элементов И являются соответственно первым и вторым входами блока управления, вторые входы второго и третьего элементов И объединены с входом второго одновибратора и являются третьим входом блока управления, входы первого и третьего одновибраторов являются соответственно четвертым и пятым входами блока управления, выходы первого, третьего и пятого элементов задержки, выход второго одновибратора, выход второго элемента И, выход элемента ЗАПРЕТ, выходы третьего и первого элементов И и выход второго элемента ИЛИ являются соответственно первым — девятым выходами блока управления.

1338074

Изменение кода функ ции

5 6 7

-2 0111

-1 1111

0 0000

1 1000

2 0100

0100

-1 1111

С

-2 0111

-1 llll

0 0 0000

0 1 1000

0 2 0100

0 1 1000

t 1

0100

2 э

0 0000

1 1000

1 0 0000

2 — 1 1111

t, -1

=t -1

5 4

3 -2 pill

4 -3 +1 1011 !QQP

1000 — 1 Illl г

Сэ

0111

1111

0 0000

t<

4 — 1

-1 1111

0 0000

С

0 1000

-4

0 2 -2 0100 0111 pill

I — 1 1111

4 7

1 — 1

2 -2 0111

3 -3 1011

+4

4 -4 - 0 0011 0000 0000

Число записанное в реверсивном счетчик

Текущий код Выходной в реверсив- код ном счетчике 7!

338074

ФАЗ

1338074

Фиг.6

Заказ 4145/56

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

7S

7Ч

Составитель О.Ревинский

Редактор А.Маковская Техред И.Попович Корректор АеТяско

Тираж 901 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5