Устройство цифровой передачи звукового сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к области эл.связи. Цель изобретения - повышение точности передачи звукового сигнала путем уменьшения искажений амплитудно-частотного спектра этого сигнала. Работа устр-ва на взаимной компенсации амплитудно-частотных искажений , возникающих при обработке на двух интерполяторах нулевого порядка прямого и инверсного представлений сигнала и их последующем суммировании . Логич. блок 8 обеспечивает путем управления мультиплексорами 7 и 12 поочередное считывание из буферньк регистров 5-1 и 5-2 поступакгщей информации. В момент смены информации в указанных регистрах производится считывание информации, записанной в регистрах на предьщущем такте. Блок 8 реализован на базе стандартного триггера с динамич. воздействием по входу синхронизации, имеющего два входа и два выхода. 3 ил. i (Л 00 со 00 о 00 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51) 4 Н 04 1 3/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3920125/24-09 (22) 28.06.85 (46) 15.09,87. Бюл. и 34 (71) Московский электротехнический институт связи (72) С.В.Бобровников, M В.Гитлиц, В,В.Добровольский, А.Ю.Зеленин и О.Б.Попов (53) 621.395.43 (088.8) (56) Патент США tt- 4058682, кл. Н 04 J 3/06, 1976. (54) УСТРОЙСТВО 1 ИФРОВОЙ ПЕРЕДАЧИ

ЗВУКОВОГО СИГНАЛА (57) Изобретение относится к области эл.связи. Цель изобретения — повышение точности передачи звукового сигнала путем уменьшения искажений амплитудно-частотного спектра этого

„„SU„„1338088 А i сигнала. Работа устр-ва на взаимной компенсации амплитудно-частотных искажений, возникающих при обработке на двух интерполяторах нулевого порядка прямого и инверсного представлений сигнала и их последующем суммировании ° Логич. блок 8 обеспечивает путем управления мультиплексорами

7 и 12 поочередное считывание из буферных регистров 5-1 и 5-2 поступающей информации. В момент смены инфор-. мации в указанных регистрах производится считывание информации, записанной в регистрах на предыдущем такте.

Блок 8 реализован на базе стандартного триггера с динамич ° воздействием по входу синхронизации, имеющего два входа и два выхода. 3 ил.

8088 2

Логический блок 8 обеспечивает

10

1 133

Изобретение относится к электрической связи, а именно к технике передачи цифрового сигнала, и может быть использовано в цифровом радиовещании при согласовании взаимно несинхронизированной аппаратуры.

Целью изобретения является повышение точности передачи звукового сигнала путем уменьшения искажений амплитудно-частотного спектра этого сигнала.

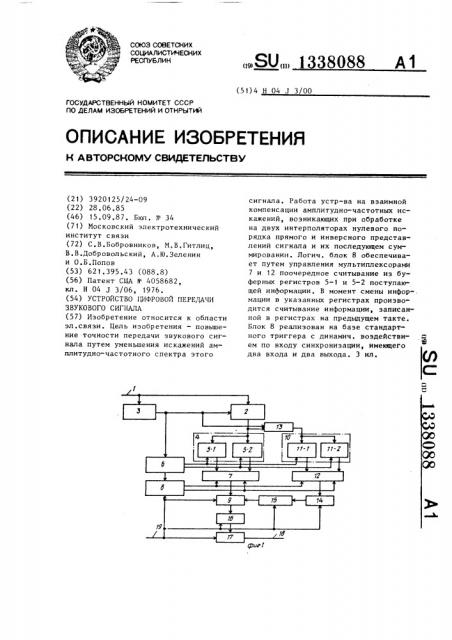

На фиг. 1 изображена структурная схема устройства цифровой передачи звукового сигнала; на фиг. 2 — диаграммы работы блока умножения; на фиг. 3 — диаграммы работы логического блока.

По временной оси отложены значения параллельных кодовых слов, велиЧина Которых S1, и S ь (выделен 3х. ные тактовые последовательности сопрягаемых цифровых потоков, Б ы, и

$ „„ (управляющие последовательности для управления мультиплексорами) .

Устройство содержит вход 1, последовательно-параллельный преобразователь 2 кода, выделитель 3 синхрочастоты, первый блок 4 буферных регистров, состоящий из буферных регистров

5-1 и 5-2, переключатель 6, первый мультиплексор 7, логический блок 8, сумматор 9, второй блок 10 буферных регистров, состоящий из буферных регистров 11-1 и 11-2, второй мультиплексор 12, первый 13 и второй 14 инверторы, первый 15 н второй 16 блоки умножения, параллельно-последовательный преобразователь 17 кода, выход

18 устройства цифровой передачи звукового сигнала, вход 19 синхрочастоты устройства °

Инверторы 13 и 14 осуществляют инверсию спектра. Каждый иэ упомянутых инверторов спектра представляет собой схему, изменяющую знак каждого второго отсчета сигнала, и выполнен на параллельном регистре. Для осу ществления инверсии в указанных блоках необходимо наличие двух входов информационного и тактирующего °

Блок 15 умножения обеспечивает сдвиг по частоте путем умножения сигнала на гармонический сигнал с частотой, равной половине разницы частот дискретизации входного и вьг ходного потоков. Блок 15 содержит генератор гармонического сигнала и блок умножения.

55 путем управления мультиплексором поочередное считывание иэ буферных регистров 5-1 и 5-2 поступающей информации. В момент смены информации в указанных регистрах производится считывание информации, записанной в регистрах на предыдущем такте. Логический блок 8 реализован на базе стандартного триггера с динамическим воздействием по входу синхронизации, имеющего два входа и два выхода, Работа устройства построена на взаимной компенсации амплитудно-частотных искажений, возникающих при обработке на двух интерполяторах нулевого порядка прямого и инверсного представлений сигнала и их последующем суммировании.

Цифровой сигнал поступает по шине

1 на первый вход преобразователя 2, который преобразует последовательный цифровой поток в параллельный под действием сигналов управления с выхода выделителя 3 синхрочастоты. С выхода преобразователя 2 сигнал поочередно заносится в буферные регистры 5-1 и 5-2 под действием сигналов управления с переключателя 6. Поочередное считывание из буферных регистров 5- 1 и 5-2 производится через первый мультиплексор 7 под действием командных импульсов с логического блока 8 в соответствие с поступающей на него по шине 19 синхрочастотой выходного сигнала. Логическим блоком 8 предусмотрен запрет на считывание новой информации в момент ее смены в буферных регистрах, в этом случае считывается предыдущая информация.

С буферных регистров 5- 1 и 5-2 интерполированный сигнал через мультиплексор 7 поступает на первый вход сумматора 9.

Инверсная ветвь интерполятора выполнена на буферных регистрах 11- i и

11-2 и втором мультиплексоре 12. Сигнал на эту ветвь подается через первый цифровой инвертор 13, а его обратная инверсия производится вторым инвертором 14. Для компенсации смещения спектра сигнала, возникающего при цифровой инверсии в случае отличия входного и выходного цифровых потоков, сигнал с выхода второго инвертора 14 подается на первый блок 15 умножения, где осуществляется его сдвиг по частоте путем умножения на

1338088 половинную частоту разницы частот дискретизации входного и выходного потоков.

С выхода умножителя 15 цифровой сигнал поступает на второй вход сумматора 9, где складывается с сигналом, обработанным в прямой ветви интерполятора. Сигнал после сумматора

9 превышает исходный по уровню. Для его нормализации введен блок 16 умножения ° Полученный сигнал преобразуется в преобразователе 17 из параллельного кода в последовательный.

Функционирование инвертора 14, блоков 15 и 16 умножения, сумматора

9 и преобразователя 17 происходит в соответствии с синхрочастотой выходного цифрового потока.

1О

Фор мул а и э о б р е т е н и я

Устройство цифровой передачи звукового сигнала, содержащее вьщелитель синхрочастоты, вход которого является информационным входом устройства циф25 ровой передачи звукового сигнала и подключен к первому входу последовательно-параллельного преобразователя кода, выход которого через первый блок буферных регистров, к первому и второму тактовым входам которого подключены первый и второй выходы переключателя, подключен к первому и второму информационным входам первого мультиплексора, а также параллельно- 35 последовательный преобразователь кода, выход которого является выходом устройства цифровой передачи звукового сигнала, о т л и ч а ю щ е е с я тем, что, с целью повышения точности передачи звукового сигнала путем уменьшения искажений амплитудно-частотного спектра этого сигнала, в него введены логический блок, к входу которого подключен выход вьщелителя синхрочастоты через переключатель, последовательно соединенные первый инвертор, к тактовому и информационному входам которого подключены вьгходы вьщелителя синхрочастоты и последовательно-параллельного преобразователя кода, второй блок буферных регистров, к первому и второму тактовым входам которого подключены первый и второй выходы переключателя, второй мультиплексор, к тактовым входам которого и тактовым входам первого мультиплексора подключены выходы логического блока, второй инве1 р, первый блок умножения, сумматор, к второму входу которого подключен тактовый выход первого мультиплексора, и второй блок умножения, выход которого подключен к информационному входу параллельно-последовательного преобразователя кода,тактовый вход которого подключен к тактовым входам логического блока, сумматора, первого и второго блоков умножителя, второго инвертора и является входом синхрочастоты устройства цифровой передачи звукового сигнала.

1338088

Составитель В.Паницкий

Редактор А.Маковская Техред B.Kàäàð Корректор В.Бутяга

Заказ 4147/57 Тираж 638 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4