Устройство тактовой синхронизации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - повышение помехоустойчивости путем снижения воз- , действия случайных фазовых сдвигов в радиоканале. Устр-во содержит дифференцирующий блок 1, эл-т ИЛИ 2, счетный триггер 3, эл-ты И 4 и 5, фазовый дискриминатор (ФД) 6, состоящий из эл-тов И 15 и 16 и RS-триггера 17, счетчик 7 импульсов , блок регистров 8 сдвига, блок перемножения 9 на весовые коэффициенты, сумматор 10, формирователь 11 корректирующих сигналов, делитель 12 частоты, блок добавления и исключения (БДИ) 13 импульсов и задающий г-р 14. Цель достигается введением эл-та ИЛИ 2, триггера 3, элтов И 4 и 5, счетчика 7. блока регистров 8, блока перемножения 9, сумматора 10 и формирователя 11, с помощью которых в БДИ 13 осуществляется косвенная подстройка частоты импульсов, поступающих от г-ра 14, и, следовательно , изменение фазового положения импульсов тактовой частоты на выходе делителя 12, Устр-во . 2 ф-лы отличается выполнением ФД 6,1 з.п.ф-лы, 2 ил. (Л со QO 00 о (Х 4

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1338094 А1 (5D 4 Н 04 L 7/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ яраг г

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3868532/24-09 (22) 13.03.85 (46) 15.09.87. Бюл. У 34 (71) Ленинградский институт инженеров железнодорожного транспорта им. акад. В.Н.Образцова (72) А.Е.Красковский и Г.А.Лешин

<53) 621.394.662(088.8) (5e) Авторское свидетельство СССР

Ф 803 115, кл. Н 04 L 7/04, 1980.

Шляпоберский В.И. Основы техники передачи дискретных сообщений. M.:

Связь, 1973, с. 275, рис. 5.15. (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ (57) Изобретение относится к электросвязи. Цель изобретения — повышение помехоустойчивости путем снижения воз, действия случайных фазовых сдвигов в радиоканале. Устр-во содержит дифференцирующий блок 1, эл-т ИЛИ 2, счетный триггер 3, эл-ты И 4 и 5, фазовый дискриминатор (ФД) 6, состоящий иэ эл-тов И 15 и 16 и RS-триггера 17, счетчик 7 импульсов, блок регистров 8 сдвига, блок перемножения 9 на весовые коэффициенты, сумматор 10, формирователь 11 корректирующих сигналов, делитель 12 частоты, блок добавления и исключения (БДИ) 13 импульсов и задающий r-p 14. Цель достигается введением эл-та ИЛИ 2, триггера 3, элтон И 4 и 5, счетчика 7 блока регистров 8, блока перемножения 9, сумматора 10 и формирователя 11, с помощью которых в БДИ 13 осуществляется косвенная подстройка частоты импульсов, поступающих от г-ра 14, и, следовательно, изменение фазового положения импульсов тактовой частоты на выходе делителя 12. Устр-во по п. 2 ф-лы отличаетсяя выполнением ФД 6. 1 s. и. ф-лы, 2 ил.

1338094

Изобретение относится к электросвязи и может использоваться н системах передачи дискретной информации по радиоканалам для осуществления тактовой

6 синхронизации.

Цель изобретения — повышение помехоустойчивости путем снижения воздействия случайных фазовых сдвигов в радиоканале. 10

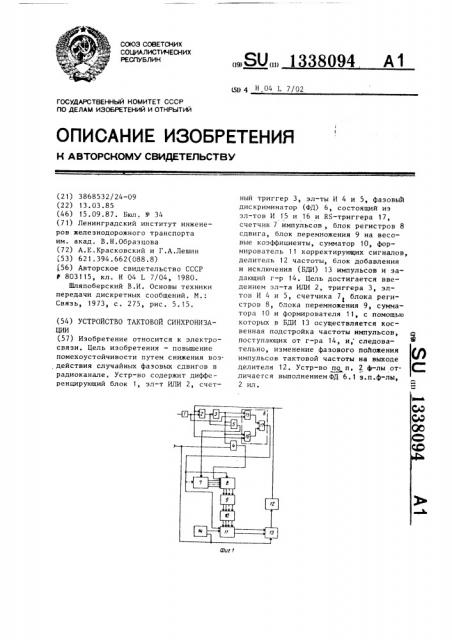

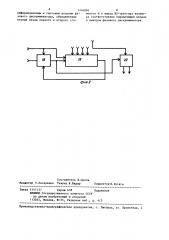

На фиг. 1 представлена структурная электрическая схема устройства тактовой синхронизации; на фиг ° 2 — структурная электрическая схема формирователя корректирующих сигналов. 15

Устройство тактовой синхронизации содержит дифференцирующий блок 1, элемент ИЛИ 2, счетный триггер 3, пер вый 4 и второй 5 элементы И, фазовый дискриминатор 6, счетчик 7 импульсов, блок 8 регистров сдвига, блок

9 перемножения на весовые коэффициенты, сумматор 10, формирователь 11 корректирующих сигналов, делитель 12 частоты, блок 13 добавления и исключе-25 ния импульсов, задающий генератор 14, Фазовый дискриминатор 6 содержит первый 15 и второй 16 элементы И и

RS — триггер 17.

Формирователь 11 корректирующих сигналов содержит ключ 18, счетчик 19 импульсов и коммутатор 20, Устройство тактовой синхронизации работает следующим образом.

Входной сигнал поступает на дифференцирующий блок 1 (фиг, 1), вырабатывающий узкие импульсы, соответствующие фронтам посылок входного сигнала. Импульсы с выхода дифференцирующего блока 1 и импульсы с выхода

40 делителя 12 поступают на вход счетного триггера 3, который изменяет свое состояние на противоположное по переднему фронту входного импульса. Сигнал с выхода счетного триггера 3 открывает ключ, реализованный на перном элементе И 4, на выходе которого формируется пачка импульсон (с частотой задающего генератора 14). Количество импульсов в пачке пропорционально длительности сигнала на выходе РО счетного триггера 3 (т,е. величине фазового рассогласования между. фронтом входного сигнала и выходным сигналом устройства тактовой синхронизации). 55

На выходе нторого элемента И 5 формируется импульс,.соответствующий второму (по времени) импульсу, поступившему на вход счетного триггера

3, В зависимости от знака фазового рассогласования это может быть импульс с выхода дифференцирующего блока 1 или импульсы с выхода счетчика

7. Импульс с выхода второго элемента

И 5 поступает на тактоный вход блока

8 регистров, срабатывающий по заднему фронту данного импульса. В фазовом дискриминаторе 6 первый элемент И 15 ньщеляет импульс с выхода дифференцирующего блока 1, если он пришел раньше импульса с выхода делителя 12. Если же первым пришел импульс с выхода делителя 12, то данный импульс вьщеляется вторым элементом И 16 фазового дискриминатора 6. Импульсы с выходов первого 15 и второго 16 элементов И управляют RS-трнтгером 17. Выходной сигнал RS-триггера 17 несет информацию о знаке фазового рассогласования.

Па выходе первого элемента И 4 формируется импульс, соответствующий моменту окончания пачки импульсов на выходе второго элемента И 5, В момент действия данного импульса на выходе фазового дискриминатора 6 присутствует ."1" илн "0" в зависимости от знака фазового рассогласования. Количество импульсов, поступающих с выхода второго элемента И 5, подсчитывается счетчиком 7, который выполняет функцию преобразователя последонательного кода в параллельный ° Импульс на выходе первого элемента И 4 записывает сформированное счетчиком 7 число и блок 8 регистрон и обнуляет счетчик 7. При этом н старший (знаковый) разряд числа, занесенного в блок 8 регпстрон, записывается "1" или 0 с выхода фазового дискриминатора 6. Таким образом, н блок 8 регистров записывается число со знаком, соответствующее величине и направлению рассогласования фазы. Запись каждого нового числа н блок 8 регистров вызывает сдвиг информации в нем на один разряд. При этом блок 8 регистров представляет собой память величины (и знака) фазовых рассогласонаний на предыдущих тактовых интервалах.

Числа со знаком с выходов блока 8 регистров поступают на входы блока

9 перемножения, который состоит иэ постоянных запоминающих блоков (ПЗБ).

Каждое число с выходов блока 8 регистров поступает на адресные входы

1338094

40 соответствующего ПЗБ. При этом на выходе данного ПЗБ выдается информация, предварительно "зашитая" по данному адресу, а именно число, равное произ- 5 ведению кода адреса на соответстнующий коэффициент. Таким образом, каждое число с выходов блока 8 регистров умножается на коэффициент, величина которого определяется положением чис- 1ð ла в соответствующем регистре блока

8 регистров, в результате чего обеспечивается большой вклад величины расстройки на непосредственно предшествующих данному тактовых интервалах при15 определении необходимой коррекции фазового положения.

Произведения величин рассогласонания на соответствующие весовые коэффициенты суммируются сумматором 10, на выходе которого формируется число со знаком, которое несет информацию о необходимой величине и направлении коррекции фазы тактовых импульсов.

По окончании импульса на выходе 25 первого элемента И 4 число с выхода сумматора 10 записывается в счетчик

19 формирователя 11 (фиг. 2). Одновременно открывается ключ 18, через который импульсы с задающего генератора 14 поступают на тактовый вход счетчика 19 и уменьшают записанное в него число. В момент прохождения счетчика 19 через нуль на его выходе формируется импульс, который закрывает ключ 18. При этом на выходе ключа 18 формируется пачка импульсов, количество которых пропорционально величине требуемой коррекции фазы импульсов тактовой частоты.

Пачка импульсов с выхода ключа

18 поступает на информационный вход коммутатора 20. В зависимости от знака числа на выходе сумматора 10 импульсы с информационного входа коммутатора 20 поступают на соответствую. 45 щие коррекционные входы блока 13 добавления и исключения импульсов, на тактовый вход которого поступают импульсы с выхода задающего генератора

14. При этом в блоке 13 добавления и исключения импульсов осуществляется косвенная подстройка частоты импульсов, посутпающих от задающего генератора 14, и, следовательно, изменение фазового положения импульсов тактовой 55 частоты на выходе делителя 12.

Формула и з о б р е т е н и я

1. Устройство тактовой синхронизации, содержащее последовательно соединенные задающий генератор, блок добавления и исключения импульсов, делитель частоты и фазовый дискриминатор, а также дифференцирующий блок, ныход которого подсоединен к информационному входу фазового дискриминатора, причем вход дифференцирующего блока и ныход делителя частоты являются соответственно входом и выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости путем снижения воздействия случайных фазовых сдвигов в радиоканале, введены последовательно соединенные элемент ИЛИ, счетный триг гер, первый элемент И и счетчик импульсов, последовательно соединенные второй элемент И и формирователь корректирующих сигналов, а также блок регистров сдвига, блок перемножения на весовые коэффициенты и сумматор, при этом выходы дифференцирующего блока и делителя частоты подсоединены соответственно к первому и второму входам элемента ИЛИ, выход которого подсоединен к первому входу второго элемента И, второй вход которого объединен с управляющим входом фазового дискриминатора и подключен к выходу счетного триггера, выход фазового дискриминатора и выходы разрядов с етчи-. ка импульсов подсоединены к соответствующим информационным входам блока регистров сдвига, тактовый вход которого подсоединен к ныходу второго элемента И, выходы блока регистров сдвига через блок перемножения на весовые коэффициенты и сумматор подсоединены к соответствующим информационным входам формирователя корректирующих сигналов, тактовый вход которого подсоединен к дополнительному выходу задающего генератора, выход которого подсоединен к второму вход первого элемента, а первый и второй выходы формирователя корректирующих сигналов подсоединены к соответствующим коррекционным входам блока добавления и исключения импульсон.

2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что фазовый дискриминатор выполнен в виде последовательно соединенных первого элемента И и RS-триггера, а также нторого элемента И, выход которого подсоединен к К-входу Rs-триггера, причем первые входы первого и второго элементов И являются соответственно

5 1338094 е информационным и тактовым входами фа- ментов И и выход RS-триггера являютзового дискриминатора, объединенные ся соответственно управляющим входом втаоые входы первого и второго эле- и выходом фазового дискриминатора. ф7иа2

Составитель В.Орлов

Редактор Т.Лазаренко Техред В.Кадар Корректор В. Бутяга

Заказ 4147/57 Тирам 638 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4