Устройство для формирования цифровых последовательностей

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для формирования сигналов, представленных в цифровой форме, предназначенных для контроля и отладки автоматизированных 11 информационно-измерительньп: систем. Отличительной особенностью устройства является то, что оно обеспечивает формирование последовательности видоизменяющихся реализаций сигнала, представленного в цифровой форме, с быстропеременными значениями формы сигнала в каждой реализации. Целью изобретения является расширение функциональных возможностей за счет обеспечения переменной длительности и переменного периода импульсов формируемой последовательности. Поставленная цель достигается за счет введения блока 5, формирования временных интервалов, который содержит счетчики 13, узел 14 переключателей, элементы ШШ 15, 16, дешифратор 17. 1 3.п. ф-лы, 2 ил. СЛ 00 со со ел 00 со Фиг.2

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 0 I 4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3961463/24-24 (22) 09.10.85 (46) 23.09.87. Бюл. N9 35 (72) А.И.Пахарин, А.В.Чернориэ и Н.М. Ядрошникова (53) 681.3(088.8) (56) Авторское свидетельство СССР

763879, кл . С 06 F 1/02, 1980 .

Патент США Ф 4404644, кл. G 06 F 1/02, 1983. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

ЦИФРОВЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для формирования сигналов, представленных в цифровой форме, предназначенных для контроля и отладки автоматизированных

„„SU„„13395 9 информационно-измерительных систем.

Отличительной особенностью устройства является то, что оно обеспечивает формирование последовательности видоизменяющихся реализаций сигнала, представленного в цифровой форме, с быстропеременными значениями формы сигнала в каждой реализации. Целью изобретения является расширение функциональных возможностей за счет обеспечения переменной длительности и переменного периода импульсов формируемой последовательности. Поставленная цель достигается за счет введе. ния блока 5, формирования временных интервалов, котбрый содержит счетчики 13, узел 14 переключателей, элементы ИЛИ 15, 16, дешифратор 17.

I з.п. ф-лы, 2 ил.

1339539

Изобретение относится к автоматике и вычислительной технике и может быть использовано для формирования сигналов, представленных в цифровой форме, предназначенных для контроля и отладки автоматизированных информационно-измерительных систем, систем сбора и обработки информации, в автоматизированных системах контроля. )p

Цель изобретения — расширение функциональных возможностей за счет обеспечения переменной длительности и переменного периода импульсов формируемой последовательности. 15

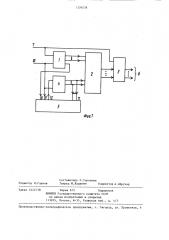

На фиг. I приведена структурная схема предлагаемого устройства; на фиг.2 — структурная схема блока формирования временных интервалов.

Устройство содержит счетчик 1, блок 2 памяти, регистр 3, счетчик 4, блок 5 формирования временных интервалов, группу 6 выходов, тактовый вход 7, выход 8 переноса счетчика 1, вход 9 сброса блока 5 формирования 25 временных интервалов, вход 10 сброса, группу 11 выходов счетчика 4, счетный вход 12 счетчика 4.

Блок 5 формирования временных интервалов содержит счетчики 13, узел gp

14 переключателей, элементы ИЛИ 15 и 16 и дешифратор 17.

Устройство работает следующим образом.

Сигналом сброса, поступающим по первому входу 10 сброса, устанавливаются в исходное состояние счетчики 1 и 4, счетчики 13 блока 5 формирования временных интервалов. Блок

2 памяти работает в режиме постоян- 40 ной выборки.

В блоке 2 памяти в п зонах памяти хранится информация о форме сигнала для и его отличающихся реализаций.

Счетчик 1 адресует ячейку памяти из п зон памяти (т.е. формирует младшие разряды адреса блока 2 памяти), выбирая последовательность значений формы сигнала для одной реализации.

Счетчик 4 определяет зону памяти (т.е. формирует старшие разряды адреса блока 2 памяти), выбирая одну из и реализаций сигнала.

Блок формирования временных интервалов задает временной интервал, в течение которого реализация выходного сигнала не изменяется. По истечении заданного интервала блок 5 вырабатывает импульс на своем выходе 12, по которому наращивается второй счетчик 4. Это приводит к выбору следующей реализации сигнала в их последовательности и т.д.

Из ячейки памяти, адресуемой счетчиком 1, зоны, адресуемой счетчиком

4, считывается информация. По заднему фронту тактового импульса, поступающего по тактовому входу 7 устройства, она заносится в регистр 3 и выдается в группу 6 выходов устройства. Одновременно наращивается счетчик 1, Считанная из блока 2 памяти информация по очередному тактовому импульсу заносится в регистр 3 и выдается на группу 6 выходов. Таким образом, на выходах группы 6 формируется последовательность значений сигнала (в цифровой форме), соответствующая одной реализации сигнала., После того, как все ячейки зоны памяти просмотрены (счетчик 1 досчитывает до максимума), по очередному тактовому импульсу на тактовом выходе 7 устройства. счетчик 1 на выходе переноса формирует сигнал, который подается на синхровход 8 блока 5 формирования временных интервалов.

Состояние счетчика 4 подается по группе 11 информационных входов блока 5 формирования временных интервалов на дешифратор 17. Сигнал на выходе последнего, соответствующий коду на его входах, появляется при налични сигнала переноса на его стробирующем входе и подается на счетный вход счетчика 13, соответствующего выбранной реализации сигнала. Счетчики 13 в исходном состоянии сброшены сигналом, поступающим на их входы сброса по входу 9 сброса блока 5 через элемент ИЛИ 15. Количество счетчиков 13 соответствует количеству различных реализаций сигнала. По пос-. тупающим на счетный вход импульсам осуществляется наращивание соответствующего счетчика 13. Узлом 14 переключателей осуществляется выбор разряда счетчика 13. Причем может быть выбран только один разряд счетчика, т.е. повторение может, быть 2,4,8, 16,... раз.

Сигнал с выхода узла 14 переключателей выдается на вход элемента

ИЛИ 16, сигнал с выхода которого сбрасывает счетчик 13 (через элемент

ИЛИ 15), и выдается на выход 12 блока 5„ По этому сигналу наращивается

1339539 состояние счетчика 4, что приводит к смене зоны блока 2 памяти и к изменению реализации выходного сигнала.

При этом дешифратором 17 выбирается

5 следующий счетчик 13, который наращивается до состояния, заданного узлом 14 переключателей.

Выходной сигнал устройства задержан на один такт относительно импульсной последовательности на тактовом входе 7. При значение сигнала в соседних выборках может быть задано произвольно в пределах, определяемых разрядностью блока 2 памяти и ре- 15 гистра 3, что позволяет формировать быстропеременный (в каждой выборке) сигнал в каждой его реализации.

Формула изобретения 2p

1. Устройство для формирования цифровых последовательностей, содержащее два счетчика, .блок памяти и регистр, причем группа выходов разря- >5 дов первого счетчика соединена с первой группой адресных входов блока памяти, выходы которого соединены с информационными входами регистра, группа выходов разрядов которого яв- 30 ляется группой информационных выходов устройства, о т л и ч а ю щ е ес я тем, что, с целью расширения функциональных возможностей за счет обеспечения переменной длительности и переменного периода импульсов формируемой последовательности, в устройство введены блок формирования временных интервалов, причем тактовый вход устройства соединен со счет- 4g ным входом первого счетчика и с входом разрешения записи регистра, вход сброса устройства соединен с входом сброса первого счетчика, с входом сброса второго счетчика и с входом сброса блока формирования временных интервалов, выход переноса первого счетчика соединен с синхровходом блока формирования временных интервалов, выход которого соединен со счетным входом второго счетчика, группа разрядных выходов которого соединена с второй группой адресных входов блока памяти и с группой информационных входов блока формирования временных интервалов.

2. Устройство по п.1, о т л и— чающее ся тем, чтоблокформирования временных интервалов содержит дешифратор, два элемента ИЛИ и и счетчиков (где и — число выходов дешифратора), узел переключателей, причем синхровход блока формирования временных интервалов соединен со стробирующим входом дешифратора, группа информационных входов которого является группой информационных входов блока, выходы дешифратора с первого по п-й соединены соответственно со счетными входами счетчиков, с первого по и-й входы сброса которых объединены и подключены к выходу первого элемента ИЛИ, первый вход которого является входом сброса блока, выходы разрядов счетчиков соединены с входами узла переключателей, выходы которого соединены с входами второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ и является выходом блока.

1339539

Фиа1

Составитель Н. Торопова

Техред М. Ходанич Корректор А.Обручар

Редактор И.Горная

Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1)3035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4222/38

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4