Устройство для вычисления булевых функций

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и предназначено для вычислений булевых функций. Цель изобретения - повьшзение быстродействия за счет исключения из процесса вычисления булевых функций аргументов, от значений которых функции Не зависят. Устройство соСлЭ СО СО ел 4; ел

t, 1, д., СОЮЗ СОВЕТСКИХ

СО11ИАЛИСТИЧЕСНИХ вЂ” РЕСПУБЛИН

091 (И) А1 (511 4 G 6 F 7 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

"- "NBFtAP

Ä13

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4005634/24-24 (22) 08,01.&6 (46) 23.09.87. Бюл. Ф 35 (72) А.И.Арсюков, В.Н.Василов, E.Ñ.ÂàëüøîHîK, В.Д.Митин и А.С.Сигалов (53) 681.3 (088,8) (56) Авторское свидетельство СССР

У 1218376, кл, G 06 F 7/00, 1984, Авторское свидетельство СССР

М - 955027, кл. G 06 F 7/00, )980 (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ БУЛЕвых ж нкций (57) Изобретение относится к автоматике и вычислительной технике и предназначено для вычислений булевых функций. Цель изобретения — повышение быстродействия за счет исключения из процесса вычисления булевых функций аргументов, от значений которых функции не зависят. Устройство со1339545

35 держит мультиплексор 1, блок ". памяти программ, дешифратор 3, две группы

4 и 11 триггеров, генератор импульсов

5, вход 6 начальной установки, элемент HE 7, триггер 8, формирователь импульсов 9, элемент И 10, информационные входы 12 и выходы 13. 1!оложительный эффект, заключающийся в обеспечении зависимости процесса вы—

Устройство относится к автоматике и вычислительной технике и может быть использовано для вычисления булевых функций в системах контроля и управления техническими и технологическими средствами.

Цель изобретения — повышение быстродействия за счет исключения из процесса вычисления булевых функций ар- 1р гументов, от значения которых функции не зависят.

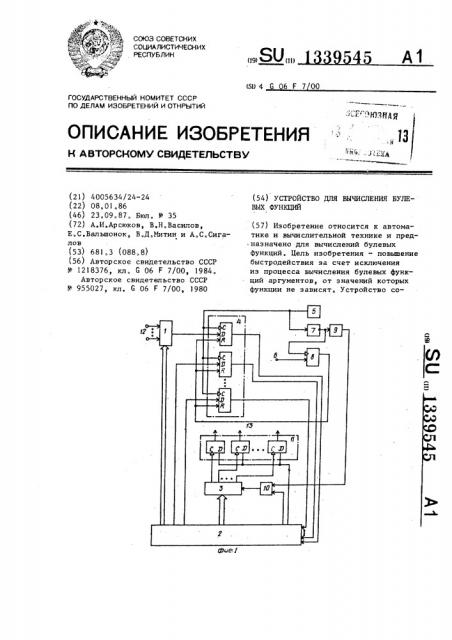

На фиг.l представлена схема устройства для вычисления булевых функций; на фиг.2 — граф †схе алгоритма вы- 15 числения булевых функций, Устройство для вычисления булевых функций содержит мультиплексор 1, блок 2 памяти программ, дешифратор 3, группу триггеров 4, генератор 5 им- 20 пульсов, вход 6 начальной установки, элемент НЕ 7, триггер 8, формирователь 9 импульсов, элемент И 10, группу триггеров 11, информационные вхо— ды 12, выходы 13„ 75

Устройство работает следующим образом.

Когда на входе 6 начальной уста— новки имеет место сигнал, запрещающий работу устройства, по отрицательному фронту первого после появления сигнала запрета импульса на выходе триггера 8 формируется сигнал установки группы триггеров 4 в начальное состояние, При этом на выходах группы триггеров 4 имеет место нулевой код независимо от поступления на его тактовые входы тактовых импульсов. При появлении на входе 6 сигнала, разре4l) шающего работу устройства, по отрицательному фронту первого тактового имчисления бчлевых функций c т значений их аргуме IToB обеспечивается тем, что при анализе значения любого из

GpI ументов логикеcY,èõ функций по ре— зультату анализа формируется условный переход к команде, по которой производится анализ другого аргумента или формируется результат вычисления. 2 ил °, 1 табл. пульса, поступающего с выхода генератора 5 импульсов, на выходе триггера

8 формируется сигнал, разрешающий ра боту группы триггеров 4 по тактовым входам. По положительным фронтам тактовых импульсов производится вызов команд программы вычисления булевых функций, записанной в блоке 2 памяти программ„

Каждая команда содержит код адреса опрашиваемого аргумента, поступающий на управляющие входы мультиплексора 1, код старших разрядов адреса условного перехода, поступающий на информационные входы группы триггеров 4, при этом на информационный вход его первого триггера поступает сигнал, равный значению опрашиваемого аргумента, — так формируется младший разряд кода условного перехода, код адреса результата вычисляемой функции, который поступает на адресные входы дешифратора 3, результата вычисления логической функции, который поступает на информационные входы группы триггеров 11„

Сигнал разрешения записи результата вычисления, который поступает на первый вход элемента И 10.

Вычисление булевых функций осуществл я е тся следующим о бра з ом.

По первой команде программы, которая формируется на выходах блока 2 памяти программ, когда устройство находится в состоянии ожидания, на первый информационный вход группы триггеров 4 поступает сигнал, соответствующий значению первого опрашиваемого аргумента первой функции, на

1339545

По этой команде производится onрос аргумента х, и, поскольку х, =О, формируется код условного перехода

00100 к команде N 4.

Переход к этой команде осуществляется по следующему тактовому импульсу. Затем опрашивается х и, так как х, =О, осуществляется переход к команде. 9 7. Далее опрашивается х и осуществляется переход к команде N - 8, так как х =О, Здесь опрашивается х, поскольку х =1, осуществляется переход к команде

У 11, по которой производится запись результата вычисления Y =0 по адресу 0 в группе триггеров 11, и одновременно опрашивается первый аргумент функции Y - х,, так как х, =О, формируется код условного перехода к команде Р 18, по которой опрашивается аргумент х . По условию х, =1, поэтоостальные информационные входы группы триггеров 4 поступают старшие разряды кода условного перехода, Таким образом, на информационных входах группы

5 триггеров 4 формируется код условного перехода, который зависит от значения опрашиваемого аргумента и определяет, какую команду устройство выполнит на первом такте работы. 10

После появления на установочных входах группы триггеров 4 сигнала, разрешающего его работу по тактовым входам, по положительному фронту первого тактового импульса код услов- 15 ного перехода записывается в группу триггеров 4 и формируется на его выходах. По этому коду на выходах блока 2 памяти программ формируется код следующей команды, по которой в 20 зависимости от значения опрашиваемого ранее аргумента опрашивается какой-либо из следующих аргументов этой функции, или, если, значение опрошенного аргумента полностью опре- 25 деляет значение вычисляемой функции, опрашивается первый аргумент следующей функции. При этом осуществляется запись результата вычисления функции в один из триггеров группы триггеров Зб

11, Запись результата осуществляется .по одному из тактовых входов группы. триггеров 11. Результат вычисления поступает из блока 2 памяти программ.

Номер тактового входа определяется кодом адреса результата, который поступает на адресные входы дешифратора 3 из блока 2 памяти программ. ДеШифратор 3 стробируется импульсом, 4р формируемым по отрицательному фронту тактового импульса формирователем 9 импульсов, Этот импульс поступает на стробирующий вход дешифратора 3 с выхода элемента И 10 при наличии 45 на его первом входе сигнала разрешения записи результата, который поступает из блока 2 памяти программ.

После опроса всех необходимых для вычисления данных булевых функций ар- о гументов, устройство можно повторить всю процедуру вычисления либо прекратить ее и выполнять две пустых, не имеющих значения команды, выполнение которых не влияет на результаты вычисления. Коды условных переходов, формирующиеся в результате выполнения этих двух команд, приводят к последующему выполнению одной из них.

Устройство находится в режиме выполнения этих команд до появления на шине 6 начальной установки сигнала, запрещающего работу группы триггеров 4 по тактовому входу.

Для циклического повторения процедуры вычисления логических функций необходимо в каждой команде, в которой имеется результат последней иэ вычисляемых функций, сформировать код условного перехода на первые два слова программы, В таблице представлена программа вычисления функций

Y — х (х Y х (х х х)у х х ) У вЂ” х х чх ° х (х чх о) (1) Граф-схема алгоритма бинарной прог; раммы вычисления функций (1} представлена на фиг.2.

Вычисление функций (1) при значе íx аргументов хо = 1. х, = ОФ следующее.

При нулевом коде на адресном входе блока 2 памяти программ производится опрос аргумента х, входящего в первую вычисляемую функцию. При хо

=1 на выходе группы триггеров 4 по первому тактовому импульсу формируется код условного перехода 00011, поэтому на выходе блока 2 памяти программ формируется команда (слово)

Р 3.

1339545

Код команды

Разрешение

Код старКод адреса х;

Команда ших разрядов адреса УП выдачи Y

00000

0011

0000

00001 хххх хххх

00010

1001

0001

00011

0010

0001

00100

0011

0110 му происходит условный переход к команде У 23 и опрашивается аргумент х, . По значению х, =0 осуществляет о ся переход к команде N 24, по которой

5 происходит запись значения 1 =0 по первому адресу, и формируется условный переход к пустым командам

11 30 и 31, Выполнение этих команд приводит независимо от значения опра- 10 шиваемого аргумента к формированию адреса условного перехода в одной из них, Следовательно, происходит зацикливание программы„

Таким образом, устройство осуществляет вычисление булевых функций с учетом значений аргументов, входящих в эти функции, тем самым исключаются участки процесса вычисления, не влияющие на конечный результат вычисления, а сам процесс вычисления зависит от значений аргументов.

Например, если х =О, вычисление первой функции заканчивается на первом такте, осуществляется переход к ко— маиде У 2, по которой рассматривается значение аргумента х,, как аргу— мента функции У, и происходит запись значения У1 =0 в группу триггеров по адресу О.

Формула изобретения

Устройство для вычисления булевых функций, содержащее блок памяти программ, мультиплексор, генератор импульсов, дешифратор, триггер, элемент НЕ, элемент И, причем выходы кода адреса опрашиваемого аргумента блока памяти программ соединены с управляющими входами мультиплексора, 10 о т л и ч а ю щ е е с я тем, что, с целью повьш ения быстродействия за счет исключения из процесса вычисления булевых функций аргументов, от значений которых функции не зависят, оно содержит две группы триггеров и формирователь импульсов, причем информационные входы устройства соединены с информационными входами мультиплексора, выход которого соединен с информационным входом первого триггера первой группы, информационные входы остальных триггеров которой соединены с выходами кода адреса условного перехода блока памяти программ, выходы кода адреса результата которого соединены с адресными входами дешифратора, стробирующий вход которого соединен с выходом элемента

И, первый вход которого соединен с выходом разрешения записи результата блока памяти программ, второй вход элемента И соединен с выходом формирователя импульсов, вход которого соединен с тактовым входом триггера и выходом элемента НЕ, вход которого соединен с выходом генератора импульсов и тактовыми входами триггеров первой группы, установочные входы которых соединены с выходом триггера, информационный вход которого соединен с входом начальной установки устройства, выходы которого соединены с выходами .триггеров второй группы, тактовые входы которых соединены с выходами дешифратора, а информационные входы триггеров второй группы соединены с выходом значения результата блока памяти программ адресные входы которого соединены с выхо-. дами триггеров первой группы, !

339545

Продолжение таблицы

0001

1001

1 О

1 0О101

0010

0101

00!10

01 1

0100

00111

0010

0101

OI0OO

0001

1001

01001

0011! а

0110

01010

0001

1001

01011

0101

0111

01100

1001

0001.01101

0001

1001 15

0100

1000

10000

0001

1001

10001

0001! 001

10010

1001

10!1

0010

1010

10011

1001

1011

10100

10101 хххх

1000

1101

10110

1010

1100

10! l l

11000 хххх

1000

1101

11001

11010 хххх

0111

1110

11011

11100 хххх

lll01

29 хххх

Ill!0

30 хххх

111 l 1

31 хххх

П р и и с ч а н и е. и означает, что разряд может принимать любое значение — -- †††--т4 5 6

01111! 339545

7 О

Х10 й= Уг=1

Фиг. 2

Яг=0

Составитель О,Березикова

Редактор И, Горная Техред М. Ходанич

Kopgeктор Н.Король

Заказ 4222/38

Тираж 672

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д,4/5

Подписное

Производственно-полиграфическое предприятие, г.ужгород, ул,Проектная,4