Устройство для алгебраического сложения чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в операционных системах, цифровых процессоров. Цель изобретения - расширение функциональных возможностей за счет одновременного формирования суммы или разности многоцифровых десятичных чисел, представленных в единичном нормальном коде. Устройство для алгебраического сложения чисел содержит первый 1, второй 2 и третий 4 сдвиговые регистры, сумматор 3, узел 5 записи знаков, узел 6 суммирования по модулю два, узел 7 сравнения, счетчик 8 и программный блок управления. С помощью узла суммирования по модулю два и узла сравнения определяется больший из операндов во время параллельного поразрядного сдвига информации, представленной в единичном нормальном коде в сдвиговых регистрах первого и второго операндов. Результат вычитания двух чисел фиксируется в третьем , . сдвиговом регистре, результат сложения двух чисел - в сумматоре. 4 ил., 4 табл. (О С СО 00 со сд СП t .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

yg 4 G 06 F 7/50

С Г1ИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 Ф а 1д

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

Il0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4066856/24-24 (22) 13.05.86 (46) 23.09,87. Бюл. N 35 (71) Винницкий политехнический институт (72) В.П.Кожемяко, З.О.Джалиашвили, T Б.Мартынюк и Т.В.Княгинина (53) 681.325.5(088.8) (56) Заявка Японии ¹ 52-35580, кл. G 06 F 7/38, 1977.

Авторское свидетельство СССР № 1136 148, кл. G 06 Р 7/50, 1983. (54) УСТРОЙСТВО ДЛЯ АЛГЕБРАИЧЕСКОГО

СЛОЖЕНИЯ ЧИСЕЛ (57) Изобретение относится к вычислительной технике и может быть использовано в операционных системах, цифровых процессоров. Цель изобретения— расширение функциональных возможнос тей за счет одновременного формирова° э0 1ИЭЫ2 А 1 ния суммы или разности многоцифровых десятичных чисел, представленных в единичном нормальном коде. Устройство для алгебраического сложения чисел содержит первый 1, второй 2 и третий 4 сдвиговые регистры. сумматор 3, узел 5 записи знаков, узел 6 суммирования по модулю два, узел 7 сравнения, счетчик 8 и программный блок управления. С помощью узла суммирования по модулю два и узла сравнения определяется больший иэ операндов во время параллельного поразрядного сдвига информации, представленной в единичном нормальном коде в сдвиговых регистрах первого и второго операндов. Результат вычитания двух чисел фиксируется в третьем сдвиговом регистре, результат сложения двух чисел — в сумматоре. 4 ил., 4 табл.

1339552 2

Изобретение относится к вычислительной технике и может быть использовано в операционных схемах цифровых процессоров.

Цель изобретения — расширение функциональных возможностей за счет одновременного формирования суммы или разности многоцифровых десятичных чисел, представленных в единичном нормальном виде.

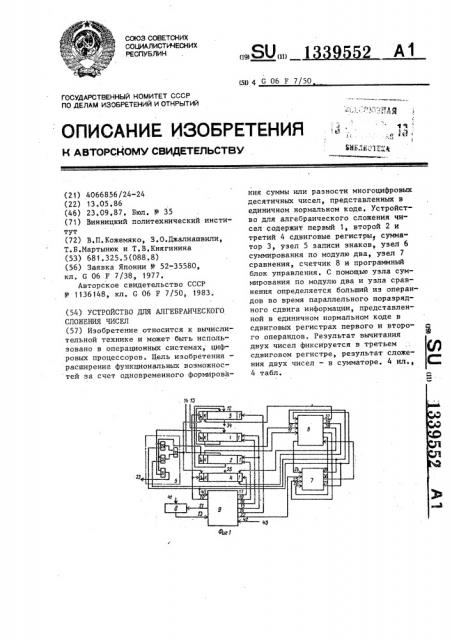

На фиг. 1 изображена структурная схема устройства для алгебраического сложения чисел; на фиг„ 2 — функциональная схема узла суммирования по модулю два и узла сравнения; на фиг, 3 — алгоритм, описывающий работу программного блока управления на фиг. 4 — функциональная схема блока управления.

Устройство для алгебраического сложения чисел (фиг. 1) содержит цва сдвиговых регистра 1 и 2 операндов

А и В соответственно, сумматор 3, регистр 4 разности, узел 5 записи знака результата, узел 6 суммирования по модулю два, узел 7 сравнения, счетчик 8, программный блок 9 управления, информационный выход старшего k-го разряда регистра I является входом 10 узла б суммирования по модулю два, а информационныи выход старшего k-ro разряда регистра 2 является входом 11 узла 6 суммирования по модулю два, информационные выходы регистров 1 и 2 соединены с информационным входом 12 сумматора 3, входы 13 и 14 являются шинами записи слагаемого А в регистр 1, слагаемого

В в регистр 2 соответственно, выходы 15 — 17 программного блока 9 управления соединены с входами управления сдвигом в регистрах 1 и 2, сумматоре 3, регистре 4 соответственно, выходы 18, 19 программного блока 9 управления соединены с входами управления считыванием информации из регистров 1 и 2 соответственно, выход

20 программного блока 9 управления

Соединен с входом разрешения записи знака в знаковый разряд сумматора 3 и регистра 4, выход 21 программного блока 9 управления соединен с входом счетчика 8, выход 22 программного блока 9 управления соединен с входом установки в начальное состояние узла

7 сравнения, вход 23 программного блока 9 управления соединен с выходом нулевого содержимого счетчика 8, 5

45 входы 24 — 26 узла 7 сравнения соединены с соответствующими выходами узла 6 суммирования по модулю два, выходы 27 и 28 узла 7 сравнения соединены с соответствующими входами узла 6 суммирования по моцулю два и вторыми входамй элементов И 29 и 30 узла 5 записи соответственно, выход знакового разряда регистра 1 соединен с первыми входами элементов И 29 и

РАВНОЗНАЧНОСТЬ 31, а выход знакового разряда регистра 2 соединен с первым входом элемента И 30 и вторым входом элемента РАВНОЗНАЧНОСТЬ 3 1 узла 5 записи знака, выходы обоих элементов И 29 и 30 соединены с входами элемента ИЛИ 32, выход которого соединен с информационным входом знакового разряда сумматора 3 и регистра

4, выход элемента РАВНОЗНАЧНОСТЬ 31 соединен с выходом 33 узла 5 записи знака и является выходом присутствия результата в сумматоре 3, выход 34 сумматора 3 и выход 35 регистра 4 являются первым и вторым выходами устройства соответственно, выход 36 узла 7 сравнения соединен соответствующим входом узла 6 суммирования по модулю два, выходы 37 — 39 которого соединены с информационным входом k-го разряда сумматора 3, с прямым и дополнительным входами младшего разряда регистра 4 соответственно, вход 40 программного блока 9 управления соединен с выходом 27 узла 7 сравнения, вход 41 счетчика 8 является его информационным входом, а вход 42 программного блока 9 управления соединен с входом 43 запуска устройства, Узел суммирования по модулю два (фиг, 2) содержит первый элемент И

44, элемент НЕРАВНОЗНАЧНОСТЬ 45, элементы И 46 — 51, три элемента

ИЛИ 52 — 54.

Узел сравнения (фиг. 2) содержит четыре RS-триггера 55 — 58, три элемента И 59 — 61.

Программный блок 9 управления (фиг. 4) содержит генератор 62 тактовых импульсов, программируемое ПЗУ

63, регистр 64, дешифратор 65, RS-триггер бб, логический блок 67.

Устройство работает следующим образом.

Запись операнда А в регистр 1 выполняется по информационной шине 13, запись операнда В в регистр 2 — по

3 1339552 информационной шине 14, а запись величины k (где k — разность операндов) в счетчик 8 и информационному входу

42. Запись операндов осуществляется в единичном нормальном коде. Во время первого такта работы устройства выполняется установка в начальное состояние узла 7 сравнения по сигналу с выхода 22 программного блока 9 управления

За второй такт выполняется сдвиг на один десятичный разряд влево информации в регистрах 1 и 2 по управляющему сигналу на выходе 15 программного блока 9 управления, при этом содержимое счетчика 8 уменьшается на единицу, а информация из старших k-х разрядов регистров 1 и 2 поступает в узел 6 суммирования по модулю два, после чего результирующие значения записываются в k-й разряд сумматора 3 и первый разряд регистра 4. Одновременно с этим в узле

7 сравнения происходит формирование признаков соотношения А ) В или А (В

Затем выполняется проверка содержимвго счетчика 8 на равенство нулю.

Если значение счетчиков не равно нулю, то за третий такт по управляющему сигналу на выходах 16 и 17 программного блока 9 управления производится сдвиг информации в сумматоре 3 и регистре 4 влево на один десятичный разряд. Сумматор 3 и регистры I и 2 являются циклическими, т.е. при сдвиге влево содержимое их старших разрядов переписывается в соответствующие младшие разряды.

Затем вновь выполняется сдвиг на один десятичный разряд влево содержимое регистров 1 и 2, который будет происходить до тех пор, пока содержимое счетчика 8 не станет равно нулю.

Узлом 6 суммирования по модулю два при обработке k-х разрядов обоих операндов определяется большая цифра и разность соответствующих разрядов, причем величина большей цифры с выхода 37 узла 6 суммирования по модулю два поступает на информационный вход k-го разряда сумматора 3. Таким образом, на втором такте работы устройства в сумматоре 3 фиксируется величина большей из двух старших цифр dÄ п Ь чисел А и В.

Разность старших цифр а„и b операндов А и В с выхода 38 узла 6 суммирования по модулю два записывается по прямому входу в первый разряд регистра 4. Одновременно с формированием величины разности старших цифр операндов в узле 7 сравнения выполняется фиксация признака одного из соотношений операндов А ) В или А с В на его соответствующих выходах 27 и 28.

Таким образом, при следующих тактах сдвига информации в регистрах

1 и 2 с выхода 37 узла 6 суммирования по модулю два в k-й разряд сумматора 3 записывается величина цифры большего из операндов, т.е. 1;, если зафиксировано соотношение А > В, или

Ь;, если А (В, Одновременно с этим в первый разряд регистра 4 записывается величина разности двух одноименных разрядов операндов в прямом или дополнительном коде в зависимости от зафиксированного соотношения, т.е. величина (a; Ъ; ) записывается по прямому входу в первый разряд регистра 4, если а. ъЬ; при А ) В и a; < b, при А (В и величина (a; — Ь; ) записывается по дополнительному входу в первый разряд регистра 4, если а; Ъ, при А с В и а„ а Ь; при А > В.

После того, как содержимое счетчика 8, обнулится, в следующем такте в сумматоре 3 по управляющему сигналу поступившему с выхода 16 программного блока 9 управления, происходит сдвиг информации влево на один разряд а по сигналу разрешения записи знака на выходе 20 программного блока 9 управления единичный сигнал на выходе

27 узла 7 сравнения разрешает запись в знаковые разряды сумматора 3 и регистра 4 знака первого операнда для случая: когда А > В, а единичный сигнал на выходе 28 узла 7 сравнения разрешает запись знака второго операнда в знаковые разряды сумматора 3 и регистра. 4 для случая, когда А с.В, т.е. в случае операции сложения знак второго операнда при записи его в регистр 2 остается без изменения, а в случае операции вычитания — изменяется на противоположный. Поэтому при фиксации знака результата знаку суммы и знаку разности присваивается знак большего из операндов, что следует из табл. 1.

1339552

Таблица 1

Соотношение

Выполненная

Преобразованный знак

Знак

Знак второКод

oneЗнак между операндами результата первого операция второго операнда рации го операнда операнда

А В

А(В

AoÂ

АсВ

А >В

АсВ

А)В

А(В

А >В

А аВ

А )В

А (В

АoB

А аВ

А>В

А <В

В соответствии с данными табл. 1 можно определить нахождение результа- 45 та: если знаки операндов, записанные .в знаковые разряды регистров 1 и 2 совпадают, о чем свидетельствует наличие сигнала на выходе 33 узла 5 записи знака, то результат находится Вд в сумматоре 3, в противоположном случае результат следует считывать из регистра 4.

После этого в соответствии с полученным соотношением между величинами

А и В, зафиксированным на одном из выходов 27 или 28 узла 7 сравнения, выполняется суммирование в сумматоре

3 находящегося там большего из oneрандов с меньшим из операндов. В результате в сумматоре 3 находится сумма обеих величин А и В, а в регистре

4 — их разнрсть.

В результате одновременного поразрядного сдвига информации в регистрах

1 и 2 длительность единичных сигналов поступает на входы 10 и 11 элемента

И 44 узла 6 суммирования по модулю два (фиг. 2). Все RS-триггеры 55 - 58 узла 7 сравнения находятся в единичном состоянии, При наличии одновременно двух единичных сигналов на входах элемента

И 44 единица с его выхода поступает

7 13 .через элемент ИЛИ 52 на информационный вход k-ro разряда сумматора 3.

Таким образом, элементом И 44 определяется общая часть двух цифр, на.ходящихся в старших k-х разрядах регистров 1 и 2, а затем она фиксируется в k-м разряде сумматора 3.

Как только один из старших k-x разрядов регистров 1 и 2 обнулится, единичный сигнал на выходе элемента

НЕРАВНОЗНАЧНОСТЬ 45 разрешает прохождение через элементы И 46 или 47 единичных сигналов, соответствующих разности цифр в старших k-x разрядах регистров 1 и 2, которые при наличии единичных сигналов на обоих выходах

27 и 28 узла 7 сравнения и при наличии нулевого сигнала на его выходе

36 через элементы И 49 или 51 поступают на вход элемента ИЛИ 52, т.е ° добавляются к полученной частичной сумме н k-м разряде сумматора 3, а также на вход элемента И 53„ в результате чего величина разности цифр а „ и Ь» поступает на прямой вход первого разряда регистра 4.

Одновременно с этим единичный сигнал на выходе элемента НЕРАВНОЗНАЧНОСТЬ 45 узла 6 суммирования по модулю два поступает на R-вход

RS-триггера 55 узла 7 сравнения,устанавливая его в нулевое состояние.

Но единичный сигнал с инверсного выхода RS-триггера 55 не проходит через элемент И 61, так как на его инверсном входе присутствует нулевой сигнал. Таким образом, RS-триггер 58 остается в единичном состоянии и единичный сигнал на его прямом выходе ра.зрешает прохождение единичного сигнала с выхода элементов И 46 или

47 узла 6 суммирования по модулю два через элементы И 59 или 60 на R-вход

RS-триггера 57 или 56 узла 7 сравнения, устанавливая их в нулевое состояние.

Так, наличие единичного сигнала на выходе элемента И 46, когда а„вЬ вызывает сброс в нулевое состояние

RS-триггера 57. При этом RS-триггер

56 остается в единичном состоянии, что соответствует фиксации соотношения А > В в виде единичного сигнала на выходе 27 узла 7 сравнения. При наличии единичного сигнала на выходе элемента И 47, когда а„ Ь, в нуль сбрасывается RS-триггер 56 и сохраняется единичное состояние RS-триг39552

55 гера 57, что соответствует фиксации соотношения А а В в виде единичного сигнала на выходе 28 узла 7 сравнения.

После завершения обработки старших цифр а и Ь„ операндов появление нулевых сигналов на входе элемента НЕРАВНОЗНАЧНОСТЬ 45 узла 6 суммирования по модулю два приводит к возникновению нулевого сигнала на входе

24 узла 7 сравнения, который разрешает прохождение единичного сигнала с инверсного выхода RS-триггера 55 узла 7 сравнения через элемент И 6 1 на R-вход RS-триггера 58 и сбрасывает его в нулевое состояние, Таким образом, в дальнейшем при обработке цифр а; и Ь, одноименных разрядов обоих операндов запрещено прохождение единичных сигналов через элементы И 59 и 60 узла 7 сравнения с помощью нулевого сигнала на прямом выходе RS-триг"гера 58 узла 7 сравнения и разрешено прохождение единичных сигналов через элементы И 48 и 50 узла 6 суммирования по модулю два с помощью единичного сигнала на инверсном выходе

RS-триггера 58 узла 7 сравнения. Следовательно, если при обработке старших цифр а и b обоих операндов определяется соотношение между операндами А ) В или A c В, то оно сохраняется на время обработки всех последующих одноименных цифр обоих операндов.

В случае, если при обработке старших цифр а и Ь„ операндов не определены соотношения А ) В или А В, т.е. когда а — b„, то присутствие нулевого сигнала на выходе элемента

НЕРАВНОЗНАЧНОСТЬ 45 узла 6 суммирования по модулю два сохраняет нулевой сигнал на инверсном выходе

RS-триггера 55 узла 7 сравнения, а значит и сохраняется единичный сигнал на прямом выходе и нулевой сигнал на инверсном выходе RS-триггера 58, т.е. в узле 7 сравнения сохраняются все условия, необходимые для формирования признака соответствующего соотношения А > А или А с В на его выходах

27 или 28. В данном случае обработка следующих одноименных цифр операндов выполняется аналогично обработке рассмотренных ранее старших цифр а и

Ь„ операндов.

В случае, когда А о В при очередном сдвиге а„ > b., а также для случая, 9 1339 когда А <В при очередном сдвиге а; Ъ. как только один из старших k-x разрядов регистров 1 или 2 обнулится, единичный сигнал на выходе элемента

НЕРАВНОЗНАЧНОСТЬ 45 разрешает прохож5 дение через элементы И 46 или 47 соответственно разности цифр в старших

k-x разрядах регистров 1 или 2, которые при наличии единичного сигнала 10 на одном иэ выходов 27 или 28 узла 7 сравнения соответственно через элемента И 49 или 51 поступают на вход элемента ИЛИ 53, а с его выхода 38 на прямой вход первого разряда регист-15 ра 4. Одновременно информация с выходов элементов И 49 или И 51 поступает через элемент ИЛИ 52 в k-й разряд сумматора 3.

Если А > В и при очередном сдвиге а; аЪ|, а для А «В при очередном сдвиге а; ) Ъ1, единичный сигнал на выходе элемента НЕРАВНОЗНАЧНОСТЬ 45 разрешает прохождение через элементы

И 47 или 46 единичных сигналов, ко- 25 торые при наличии единичного сигнала на одном иэ выходов 27 или 28 узла

7 соответственно через элементы И 50 или .48 поступают на вход элемента

ИЛИ 54, а с его выхода 39 на соот- ЗО ветствующий дополнительный вход регистра 4.

Для наглядности рассмотрим пример, когда А ) В: A=45, B=32 Исходные числа в регистрах 1 и 2 в единичном нормальном коде представлены следующим образом: регистр 1 : 45 — 111100000 111110000 регистр 2 : 32 — 111000000 110000000

При одновременном сдвиге содержимого старших разрядов обоих регистров 1 и 2 на выходе элемента И 44 присутствует единичный сигнал в течение 3, где Т вЂ” время записи и сдвига одной 45 единицы в регистрах 1, 2, 4 и сумматоре 3, который будучи подан через элемент ИЛИ 52 с выхода 37 узла 6 на вход k-ro разряда сумматора З,приводит к записи в его старшем k-м разряде величины общей части старших зна значащих цифр а и Ь слагаемых А и В т.е. 3.

Как только старший разряд регистра 2 обнулится, единичный сигнал на выходе элемента НЕРАВНОЗНАЧНОСТЬ 45 разрешает прохождение через элемент

И 46 единичного сигнала длительностью

552 lO

i сбответствующего разности цифр в старшем разряде регистров 1 и ?, который при наличии единичного сигнала на выходе 27 узла 7 сравнения через элемент И 49 поступает на вход элементов ИЛИ 52 и 53, а с выхода элемента ИЛИ 53 — на прямой вход первого разряда регистра 4. Таким образом в первом разряде регйстра 4 будет записана разность (а — Ь ) равная 1, а в узле 7 сравнения будут зафиксированы единичный сигнал на его выходе

27 и нулевой сигнал на его выходе 28, что соответствует соотношению А В, Кроме того, единичный сигнал с выхода элемента ИПИ 52 поступает на вход

k-ro разряда сумматора 3, где суммируется с его содержимым. Следовательно, в k-м разряде сумматора 3 будет записана величина 4. После сдвига информации в обоих регистрах 1 и 2 в старших разрядах будут находиться значения следующих разрядов, т.е. а и b<. При сдвиге информации в сумматоре 3 и регистре 4 старший разряд сумматора 3 и младший разряд регистра

4 освобождаются для записи в них соответствующей информации. Время сдвига является величиной фиксированной и равно 9Г .

При следующем сдвиге содержимого регистров 1 и 2 на выходе элемента

И 44 присутствует единичный сигнал течение 2 3, который будучи подан через элемент ИЛИ 52 с выхода 37 узла 6 суммирования по модулю два на вход k-го разряда сумматора 3, приводит к записи в него величины общей части младших значащих разрядов, т. е . 2.

После обнуления регистра 2 единичный сигнал на выходе элемента НЕРАВНОЗНАЧНОСТЬ 45 разрешает прохождение через элемент И 46 единичного сигнала длительностью 3 ь, который при наличии единичного сигнала на выходе 27 узла 7 сравнения через элемент И 49 поступает на вход элементов

ИЛИ 52 и 53, а с их выходов соответственно на вход k разряда сумматора

3 и на прямой вход первого разряда регистра 4. В итоге в сумматоре 3 получаем величину 45, равную большему из операндов — операнду А, а в регистре 4 — разность 13. Одновременно с этим осуществляется запись знака числа А через элементы И 29, или 32 узла 5 записи знака,в знаковый разряд

Таблица 2

Связь

У п/п

Примечание

Название

Номер Обозначение

Сигнал нулевого содержимого счетчика 8 результата

ll

13395 сумматора 3 и регистра 4, поскольку в данном случае выполняется соотношение А ъ В и знаку разности и суммы присваивается значение знака больше5

ro операнда А.

Возможен случай, когда А Â, а;аЬ; или А с В; íî а; Ь . Например А =

= 45, B=39, 10 регистр i 45 — 111100000 111110000 — — а2 а, регистр 2:39 — 111000000 111111111 — — >

Ь Ь

При сравнении цифр младших разрядов (5 и 9) на выходе элемента И 44 присутствует единичный сигнал в течение 5, который через элемент ИЛИ 52 г записывается в k-м разряде сумматора.

3. При дальнейшем сдвиге информации в регистрах 1 и 2, как только k-й разряд регистра 1 обнуляется, единичный сигнал на выходе элемента НЕРАВНО- 25

ЗНАЧНОСТЬ 45 разрешает прохождение через элемент И 47 единичного сигнала длительностью 4 ь, который при наличии единичного сигнала на выходе 27 узла

7 сравнения через элемент И 50 посту- gp пает на вход элемента ИЛИ 54, а затем на дополнительный вход первого разряда регистра 4. В результате этого в первом разряде регистра 4 разность величин а, и Ь записывается в дополнительном до 10-ти коде, т.е. 6, и происходит уменьшение на единицу величины в старшем разряде регистра 4, т.е ° ранее записанной там единицы.

52 12

Таким образом, в сумматоре 3 зафиксировано число 45, а в регистре 4 разность, равная 6.

Алгоритм алгебраического сложения чисел (фиг. 3) реалиэуемьп программным блоком 9 управления, заключается в следующем: устанавливаются в начальное состояние все RS-триггеры узла 7 сравнения, выполняется сдвиг на один десятичный разряд влево информации в обоих регистрах 1 и 2, содержимое счетчика 8 уменьшается на единицу, проверяется условие равенства содержимого счетчика 8 нулю (если содержимое счетчика 8 не равно нулю, то в сумматоре 3 и регистре 4 выполняется сдвиг информации на один десятичный разряд влево), затем выполняется предыдущая операция, если содержимое счетчика 8 равно нулю, то в сумматоре 3 выполняется сдвиг информации на один десятичный разряд влево, а в знаковый разряд сумматора 3 и регистра 4 записывается знак результата, проверяется условие А > В, если условие А о В выполняется то к содержимому сумматора 3 прибавляется содержимое регистра 2, если условие

А В не выполняется, то к содержимому сумматора 3 прибавляется содержимое регистра t. Операция сложения закончена.

Необходимые для управления функционированием устройства управляющие и логические сигналы приведены в табл. 2, а последовательность формирования управляющих сигналов у, уд на представленном алгоритме (фиг. 3).

При Х< = 1 в сумматоре 3 выполняется сдвиг информации на один десятичный разряд влево, в знаковый разряд.сумматора 3 и регистра 4 записывается знак

14

1339552

Продолжение табл.2

Примечание

Связь

Название

Х, Сигнал соотношения А > В

При Х = 1 к содержимому сумматора 3 прибавляется содержимое регистра 2

Режим х

При Х = 1 выполня3 ется операция сложения

Установка в начальное состояние узла 7 сравнения

У<

Сдвиг в регистрах 1 и 2

21

Разрешение счета счетчика 8

16

Уд

Управление сдвигом в сумматоре 3

Управление с,цвигом в регистре 4

Уб

Запись знака в знаковый разряд сумматора 3 и регистра

Считывание информации из регистра 2

10 l9

У, Считывание информации из регистра 1

У к

"-:авершение микропрограммы

Устройство управления может быть построено на основе принципа программного управления, использующего операционно-адресную структуру управ- ð ляющих слов. Синтез устройства управления (УУ) с программируемой логикой сводится к разработке схемы УУ и к разработке микропрограммы, которая должна быть записана в ПЗУ. 55

Таблица 3

У2

У 001

Уг 010

Разбивка закодированных управляющих сигналов по полям микрокоманды представлена в табл, 3.

И и/и

Номер Обозначение

У 011

У2. 100

У 101

001

У 010

У, 011

У 100

1339552 16

Таблица 4

7 110

Содержимое ПЗУ для случая принудительной адресации и алгоритма (фиг. 3) представлено в табл. 4, Ф Адрес У1 У2 Х АО А1 п/п

1 000 001 000 00 001 000

2 001 010 001 01 010 011

3 010 011 011 00 001 000

4 011 011 010 10 101 100

5 100 100 000 00 110 000

6 101 000 100 00 110 000

101 000 00 000 000

На фиг.,4 представлена функциональная схема программного блока 9 управ- . ления, на которой приняты следующие обозначения: ГТИ вЂ” генератор тактовых З0 импульсов, ROM — программируемое ПЗУ (K155 РЕЗ), RG — регистр (K155 ИР13), DC — дешифратор (K155 ИДЗ), RS — триггер (К155 TM2), а входы и выходы программного блока 9 управления обоз- З5 начены в соответствии с фиг. 1.

Формула изобретения

Устройство для алгебраического 40 сложения чисел, содержащее три сдвиговых регистра, сумматор, узел суммирования по модулю два, узел записи знака результата, содержащий два элемента И и элемент ИЛИ, узел сум- 45 мирования по модулю два содержит три элемента И, два элемента ИЛИ, причем входы разрядов первого сдвигового регистра соединены с входами первого операнда устройства, входы второго 50 сдвигового регистра соединены с входами второго операнда устройства, выходы старших разрядов первого и второго сдвиговых регистров подключены соответственно к первому входу узла суммирования но модулю два, ко1 торый соединен с первым входом первого, второго элементов И узла суммирования по модулю два и второму его входу, который соединен с первым входом третьего и вторым входом первого элементов И узла суммирования по модулю два, выход первого элемента И которого соединен с первым входом первого элемента ИЛИ узла суммирования по модулю два, выход которого соединен с первым выходом узла суммирования по модулю два, который соединен со старшим разрядом сумматора, второй выход узла суммирования по модулю два соединен с прямым входом младшего разряда третьего сдвигового регистра, выход второго элемента ИЛИ узла суммирования по модулю два соединен со вторым выходом узла суммирования по модулю два, выход знакового разряда первого сдвигового регистра соединен с первым входом первого элемента И узла записи знака, выход которого соединен с первым входом элемента ИЛИ узла записи знака, второй вход которого соединен с выходом второго элемента И узла записи знака, первый вход которого соединен с выходом знакового разряда второго сдвигового регистра, вторые входы первого и второго элементов И узла записи знака соединены соответственно с третьим и четвертым

,входами узла суммирования по модулю два, выход элемента ИЛИ узла записи знака соединен с входом знакового разряда третьего сдвигового регистра, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет одновременного формирования суммы или разности многоцифровых десятичных чисел, представленных в единичном нормальном виде, в него введены узел сравнения, счетчик и программный блок управления узел записи знака дополнительно содержит элемент РАВНОЗНАЧНОСТЬ, узел суммирования по модулю два дополнительно содержит четвертый, пятый, шестой и седьмой элементы,И, третий элемент ИЛИ и элемент НЕРАВНОЗНАЧНОСТЬ, узел сравнения содержит четыре RS-триггера и три элемента И, причем первые входы первого и второго элементов И узла записи знака соединены соответственно с первым и вторым входами элемента равнозначность, выход которого соединен с выходом присутствия результата устройства, выход элемента ИЛИ узла записи знака соединен с входом знакового разряда сумматора, информационные входы всех раз18

17

1339552 рядов сумматора, кроме старшего, соединены с соответствующими выходами разрядов первого и второго сдвиговых регистров, первый, второй и третий выходы программного блока управления соединены с входами управления сдвигом первого и второго сдвиговых регистров, сумматора, третьего сдвигового регистра соответственно, чет вертый и пятый выходы программного блока управления подключены к входам управления считыванием первого и второГо сдвиговых регистров соответственно, шестой, седьмой и восьмой выходы программного блока управления соединены с входом разрешения записи знака в знаковый разряд третьего сдвигового регистра и сумматора, с вычитающим входом счетчика и с установочным входом узла сравнения соответственно, первый, второй входы программного блока управления соединены с .выходом значения нулевого содержимого счетчика, с третьим входом узла суммирования по модулю два и входом запуска устройства соответственно, третий выход узла суммирования по модулю два соединен с дополнительным входом младшего разряда третьего сдвигового регистра, третий выход узла суммирования по модула два соединен с выходом третьего элемента ИЛИ узла суммирования по модулю два, первый и второй входы которого соединены соответственно с выходами четвертого и пятого элементов И узла суммирования по модулю два, первый вход четвертого элемента И узла суммирования по модулю два соединен с четвертым входом узла суммирования по модулю два, прямым выходом первого RS-триггера узла сравнения и первым входом шестого элемента И узла суммирования по модулю два, второй вход которого соединен с четвертым выходом узла суммирования по модулю два, выходом третьего и первым входом пятого элементов И узла суммирования по модулю два и первым входом первого элемента И уз ла сравнения, второй вход которого соединен с первым входом второго элемента И узла сравнения и прямым выходом второго RS-триггера узла сравнения, инверсный выход которого соединен с пятым входом узла суммирования

?0

40 с 5

55 по модулю два и вторыми входами четвертого и пятого элементов И узла суммирования по модулю два, первый и второй входы первого элемента И узла суммирования по модулю два соединены соответственно с первым и вторым входом элемента НЕРАВНОЗНАЧНОСТЬ узла суммирования по модулю два, выход которого соединен с вторыми входами второго и третьего элементов И узла суммирования по модулю два, пятым выходом узла суммирования по модулю два, R-входом третьего RS-триггера узла сравнения и инверсным входом третьего элемента И узла сравнения, выход которого соединен с R-входом второго RS-триггера, установочный ,вход которого соединен с установочными входами первого, третьего и четвертого RS-триггеров узла. сравнения и с установочным входом узла сравнения, инверсный выход третьего

RS-триггера соединен с прямым входом третьего элемента И, входом узла сравнения, выходы второго и первого элементов И узла сравнения соединены соответственно с R-входами первого и четвертого RS-триггеров узла сравнения, прямой выход четвертого RS-триггера соединен с третьим входом узла суммирования по модулю два, первым входом седьмого и третьим входом пятого элементов И узла суьалирования по модулю два, третий вход четвертого элемента И узла суммирования по модулю два соединен с выходом второго и вторым входом седьмого элементов И узла суммирования по модулю два, шестым выходом узла суммирования по модулю два и вторым входом второго элемента И узла сравнения, выход седьмого элемента И узла суммирования по модулю два. соединен с вторым входом первого и первым входом второго элементов ИЛИ узла суммирования по модулю два, выход шестого элемента И узла суммирования по модулю два сое,динен с вторым входом второго и третьим входом первого элементов ИЛИ узла суммирования по модулю Два, суммирующий вход счетчика соединен с входом записи разрядности операндов устройства, выходы разрядов суммато-. ра и третьего регистра соединены Соответственно с первым и вторым выходами результата устройства, 1339552

Фиг.7

1339552

Составитель N.Åñåíèíà

Техред М,Дидык .

Редактор Е. Папп

Корректор M.Шароши

Подписное.Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

Заказ 4223/39 Тираж 672

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

21 я 7 р 9