Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычисли- .тельной технике и может использоваться при построении микропрограммных процессоров. Цель изобретения - расширение области применения за счет организации механизма косвенной адресации . Устройство содержит блик 1 памяти микропрограмм, блок 2 связи с памятью, регистр 3 микрокоманд, группу элементов И 4, регистр 5 адреса , -триггер 6 блокировки, злемент ИЛИ 7, блок 8 памяти таблиц, коммутатор 9, триггер 10 и шифратор 11. Устройство обеспечивает динамическое преобразование логических адресов микрокоманд в реальные адреса управляющей памяти и динамическую загрузку микропрограмм в процессе вьтолнения программы. 2 ил. u.f

СОЮЗ СОВЕТСНИХ

СОЩ4АЛИСТИЧЕСНИХ

РЕСПУБЛИН

»80 .1ИЫ60 А1

150 4 G 06 F 9 22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ в д:,1,,13

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4031063/24-24 (22) 28.02.86 (46) 23.09.87. Бюл. Р 35 (72) В.А.Мальцева, В.Г.Васендо, М.Л.Мархасин, А.Л.Радкевич и А.К.Го лован (53) 681 ° 3(088.8) (56) Авторское свидетельство СССР

Ф 752341, кл. G 06 F 15/00, 1980.

Авторское свидетельство СССР

М - 118533 1, кл. G 06 F 9/22, 1984. (54) УСТРОЙСТВО МИКРОНРОГРАММНОГО

УПРАВЛЕНИЯ (57) Изобретение относится к вычисли-. .тельной технике и может использоваться при построении микропрограммных процессоров. Цель изобретения — расширение области применения эа счет органиэации механизма косвенной адресации. Устройство содержит блок 1 памяти микропрограмм, блок 2 связи с памятью, регистр 3 микрокоманд, группу элементов И 4, регистр 5 адреса, триггер 6 блокировки, элемент

ИЛИ 7, блок 8 памяти таблиц, коммутатор 9, триггер 10 и шифратор 11.

Устройство обеспечивает динамическое преобразование логических адресов микрокоманд в реальные адреса управляющей памяти и динамическую загрузку микропрограмм в процессе выполнения программы. 2 ил.

1339560

Изобретение относится к вычислиг-ельной технике и может использоваться при построении микропрограммньгх процессоров.

Цель изобретения — расширение области применения за счет организации механизма косвенной адресации.

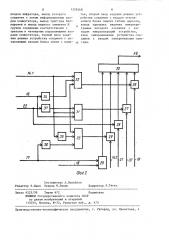

На фиг. 1 приведена функциональная схема устройства микропрограммного управления; на фиг. 2 — функциональная схема коммутатора.

Устройство (фиг. 1) содержи блок

1 памяти микропрограмм (управляющая память), блок 2 связи с памятью, регистр 3 микрокоманды,группу 4 элементов И, регистр 5 адреса., триггер 6 блокировки, элемент ИЛИ 7, блок 8 памяти таблиц адресов, коммутатор 9, триггер 10 и шифратор 11, первый вход

12 логических условий устройства (шина "Запросы" ), первый вход 13 данных .устройства (шина "Данные ОП"), выходы 14 микроопераций устройства (шина "Микрокоманда"), выходы 14, и

14 группы 4 элементов И, выход 15, микроопераций устройства (шина Состояние УП"), второй вход 15 задания режима устройства, второй вход

16 логических условий устройства (вход "Расширение КОП 1), третий вход

17 логических условий устройства (вход "Управление ЦП"), первый вход 18 кода команды устройства (шина

"Данные ЦП"), второй вход 19 кода команды устройства (шина "Код операции")35 третий вход 20 кода команды устройства (шина "Расширенный код операции"), выход 21 шифратора, выход 22 тригге— ра блокировки, вход 23 синхронизации устройства, первый вход 24 задания режима устройства.

Коммутатор 9 (фиг. 2) содержит группы 25-29 элементов И, группу >О элементов ИЛИ; группы 31-33 элементов И и 34-37 элементов НЕ.

Устройство работает следующим образом.

С помощью специальных микропрограмм загружаются все таблицы в память 50

8 таблиц (перед началом работы). Изменение информации во время работы в этой памяти доступно только специальным микропрограммам и осуществляется с помощью шины 18 "Данные

ЦП". При этом адрес поступает через группу 25 элементов И и группу 30 элементов ИЛИ, а информация — непосредственно в память 8 таблиц, При переходе на выполнение текущей команды программы по коду операции (или расширенному коду операции) через коммутатор 9 происходит обращение к таблице начальных адресов микропрограмм и выбирается из памяти 8 таблиц строка, содержащая адрес, признак на шину 15 "Состояние УП" и признак наличия искомой микропрограммы в управляющей памяти 1 (УП). Если микропрограмма загружена в УП, адрес из памяти 8 таблиц передается в регистр

5 адреса микрокоманд и начинается выполнение требуемой микропрограммы.

Если микропрограмма не загружена, по сигналу из памяти 8 таблиц устанавливаются триггер 10 и через схему

ИЛИ 7 триггер 6 блокировки, который запрещает распространение микрокоманды, только что прочитанной по выбранному адресу.. Потенциал с выхода триггера, 10 поступает на шифратор 11 для формирования адреса строки памяти 8 таблиц, где хранится начальный адрес микропрограммы загрузки требуемого блока микропрограмм.

Во время выполнения микропрограммы возможен переход из одного блока в другой (если микропрограмма занимает несколько блоков). В текущий момент не все блоки могут находиться в УП и место расположения блоков, кроме того, произвольно. Поэтому адреса переходов за пределы того блока,г в котором работает текущая микропрограмма, преобразуются в реальные адреса блоков УП. Таблица реальных адресов блоков по объему рассчитана на максимальное количество блоков, размещаемых в ОП. В рассматриваемом примере 512 таких блоков и соответственно в таблице 512 строк.

Запись реальных адресов блоков УП осуществляется микропрограммно во время "подкачки" блока по требованию микрокоманды. Если блок не загружен в УП, в соответствующей ему строке . записан признак "наличия" блока, по которому происходит выход на микропрограмму подкачки этого блока, как это описано вышее.

Номер блока из регистра 3 микрокоманд через группу 4 элементов И и коммутатор 9 поступает на адресные входы памяти 8 таблиц, а прочитанный реальный адрес блока и младшая часть адреса микрокоманды поступает в регистр 5 адреса микрокоманд.!

339560

Коммутатор 9, предназначенный для формирования адреса обращения к памяти 8 таблиц, работает следующим образом, 5

Управляющий код из микрокоманды, обозначающий конец предыдущей микропрограммы, с выхода группы 4 элементов И поступает на элементы И 32 и

31 и элемент НЕ 35 для формирования 10 разрешающих потенциалов. При поступлении этого кода на выходе элемента

И 32 появляется разрешающий потенциал на группу элементов И 26 и выдается адрес обращения по коду операции на группу элементов ИЛИ 30.

При появлении разрешающего потенциала на входе 16 "Расширение КОП" с выхода схемы И 31 поступает разрешающий потенциал на выдачу адреса по расширенному коду операции через группу 27 элементов И и группу 30 элементов ИЛИ.

По разрешающему потенциалу с выхода 22 триггера 6 блокировки через 25 группу 28 элементов И на группу 30 элементов ИЛИ выдается адрес по внешним запросам с выхода 21 шифратора 11.

По разрешающему потенциалу с входа

17 "Управление ЦП" через групгу 25 элементов И и группу 30 элементов ИЛИ выдается адрес обращения памяти таблиц для чтения или записи информации.

Если отсутствуют перечисленные вьппе разрешения на выдачу адресов, на З6 выходе схемы И 33 появляется разрешение на выдачу адреса из микрокоманды для преобразования его в реальный адрес управляющей памяти. Этот адрес с выхода 14 группы 4 элементов И выдается на группу 29 элементов И и далее на группу 30 элементов ИЛИ.

Запись информации во все элементы памяти производится по сигналам внешней синхронизации.

Формула изобретения

Устройство микропрограммного управления, содержащее блок памяти микропрограмм, блок связи с памятью, регистр микрокоманды, группу элементов И, регистр адреса, триггер блокировки, элемент ИЛИ, шифРатоР, причем первый вход данных устройства соединен с первым информационным входом блока связи с памятью, первый информационный выход которого соединен с информационным входом блока памяти микропрограмм, выход микроопераций которого соединен с вторым информационным входом блока связи с памятью, второй информационный выход которого соединен с информационным входом регистра микрокоманд, группа выходов поля микроопераций которого соединена соответственно с первыми входами элементов И группы, кроме первого элемента И, выходы которых соединены с выходами микроопераций устройства, управляющий выход блока связи,с памятью соединен с входом чтения-записи блока памяти микропрограмм, выход признака конца микропрограммы регистра микрокоманд соединен с первым входом первого элемента И группы, первый вход логических условий устройства соединен с первым входом шифратора и с первым входом элемента ИЛИ, вьцсод которого соединен с информационным входом триггера блокировки, выход которого соединен с вторыми входами элементов

И группы, вход синхронизации устройства соединен с входами синхронизации триггера блокировок, регистра микрокоманд, блока связи с памятью, регистра адреса, выход регистра адреса соединен с адресным входом блока памяти микропрограмм, о т л и ч а ю— щ е е с я тем, что, с целью расширения области применения за счет организации косвенной адресации, оно содержит блок памяти таблиц адресов, коммутатор, триггер, причем первый, второй и третий входы кода команды устройства соединены соответственно с первым, вторым и третьим информационными входами коммутатора, второй и третий входы логических условий устройства соединены соответственно с первым и вторым управляющими входами коммутатора, выходы элементов И группы объединены и соединены с первым информационным входом регистра адреса и с четвертым информационным входом коммутатора, выход которого соединен с адресным входом блока памяти таблиц, выход которого соединен с вторым информационным входом регистра адреса, второй вход данных устройства соединен с информационным входом блока памяти таблиц адресов, выход признака блокировки которого соединен с информационным входом триггера, выход которого соединен с вторым входом элемента ИЛИ и с вторым

5 1339560 6 гера.

Составитель А.Михайлов

Редактор Е.Папп Техред М.Дидык

Корректор А.Тяско

Заказ 4223/39 Тираж 672

ВНИИПИ Государственного комитета СССР ( по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, r, Ужгород, ул. Проектная, 4

v входом шифратора, выход которого соединен с пятым информационным входом коммутатора, выход триггера блокировки и выход первого элемента И группы соединены соответственно с третьим и четвертым управляющими входами коммутатора, первый вход задания режима устройства соединен с управляющим входом блока связи с памятью, второй вход задания режима устройства, соединен с входом чтениязаписи блока памяти таблиц адресов, 6 выход признака наличия микропро— граммы которого соединен с выходом микроопераций устройства, вход синхронизации устройства соединен с входом синхронизации триг