Аналого-цифровое интергрирующее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в приборостроении , в гибридных вычислительных устройствах для интегрирования сигналов, когда требуются большие постоянные времени интегрирования. Цель изобретения - расширение динамического диапазона интегрируемых сигналов. Устройство содержит аналоговый интегратор 1, реверсивный переключатель 2, схемы сравнения 3 и 4, коммутатор 5, элемент ИЛИ 6, одновибратор 7 и реверсивный счетчик 8. Устройство имеет более широкий по амплитуде динамический диапазон интегрируемых сигналов , обусловленный тем, что отсутствует запаздывание подключения компенсирующего напряжения к аналоговому интегратору, а следовательно, отсутствует запаздывание изменения выходного потенциала аналогового интегратора в сторону убывания. При этом коррекция содержимого интегратора 1 производится сразу же по достижении выходным потенциалом последнего уровня масштабируюш;его потенциала. 5 ил. (Л 6 - 7 -j СО СО СП СО «J XD 2Zir фиг.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1339591 (511 4 G 06 G 7/186

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTGPCHOMY СВИДЕТЕЛЬСТВУ И ;"." (21) 3968650/24 — 24 (22) 21.10.85 (46) 23.09.87. Вюл. ¹ 35 (71) Куйбышевский авиационный институт им. акад. С.П.Королева (72) В.А.Медников и А.Н.Порынов (53) 681.335(088.8) (56) Авторское свидетельство СССР № 389515, кл. G 06 С 7/18, )971.

Авторское свидетельство СССР № 868784, кл. G 06 G 7/186, 1980. (54) АНАЛОГО-ЦИФРОВОЕ ИНТЕГРИРУ)ОЩЕЕ

УСТРОЙСТВО (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в приборострое— нии, в гибридных вычислительных устройствах для интегрирования сигналов, когда требуются большие постоянные времени интегрирования. Цель изобретения — расширение динамического диапазона интегрируемых сигналов. Устройство содержит аналоговый интегра— тор 1, реверсивный переключатель 2, схемы сравнения 3 и 4, коммутатор 5, элемент ИЛИ 6, одновибратор 7 и ре— версивный счетчик 8. Устройство име— ет более широкий по амплитуде динами— ческий диапазон интегрируемых сигналов, обусловленный тем, что отсутствует запаздывание подключения компенсирующего напряжения к аналоговому интегратору, а следовательно, отсутствует запаздывание изменения выход— ного потенциала аналогового интегратора в сторону убывания. При этом коррекция содержимого интегратора 1 производится сразу же по достижении выходным потенциалом последнего уровня масштабирующего потенциала. 5 ил.

133959) Изобретение относится к автоматике и вычислительной технике и может найти применение при построении гибридных вычислительных устройств, ин— формационно-измерительных и вычислительных систем и комплексов.

Цель изобретения — расширение динамического диапазона интегрируемых сигналов.

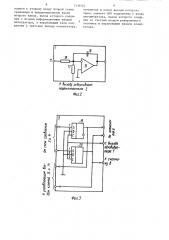

На фиг.1 представлена схема аналого-цифрового интегрирующего устройства; на фиг.2 — схема аналогового интегратора; на фиг.3 и 4 — коммутатор, варианты выполнения; на фиг.5 — диаграммы напряжений, отражающие сущность работы устройства.

Аналого-цифровое интегрирующее устройство (фиг.1) содержит аналого— вый интегратор 1, реверсивный пере.— ключатель 2, две схемы 3 и 4 сравнения, коммутатор 5, элемент ИЛИ 6, одновибратор 7, реверсивный счетчик 8, вход 9 опорного уровня устройства, выход 10 и вход 11.

Реверсивный переключатель 2 состоит из инвертора 12 и двух ключей

13 и 14.

Устройство включает также аналоговый интегратор 15, интегрирующий конденсатор 16 и два масштабных ре.зистора 17 и 18, первые выводы которых являются соответственно вторым и первым информационными входами аналогового интегратора

Коммутатор 5 в первом варианте

его выполнения (фиг.Ç) содержит два

D-триггера 19 и 20, S-входы которых являются первым и вторым входами коммутатора, D-входы соединены с шиной нулевого потенциала, С-входы подключены к управляющему входу коммутатора, а прямые выходы являются его выходами.

Коммутатор (фиг. 4) содержит два элемента И 21 и 22 и D-триггер 23, S-вход которого является входом коммутатора, прямой выход является выходом коммутатора и подключен к первому входу элемента И ?2, инверсный выход D-триггера является другим выходом коммутатора и соединен с первым входом элемента И 21. Вторые входы элементов И 21 и 22 и С-вход

D-триггера подключены к управляющему входу коммутатора. Выходы элементов

И 21 и 22 являются соответствующими выходами коммутатора.

1О

?5

Устройство работает следующим образом.

В исходном состоянии входной сиг,— нал на входе !! устройства (фиг.1) отсутствует. При этом выходной потенциал аналогового интегратора 1 равен нулю, содержимое счетчика 8 нулевое.

Также нулевой уровень напряжений присутствует на первом и втором выходах коммутатора 5 и выходе ключей 13 и 14 реверсивного переключателя 2.

С приходом в момент времени t на вход 11 входного сигнала (см.фиг.5а) начинается процесс интегрирования последнего.

Выходное напряжение аналогового интегратора 1 поступает на первые входы схем сравнения 3 и 4, на вто— рых входах которых действуют опорные потенциалы напряжений противоположных знаков соответственно +U и -U поступающие с входа 9 опорного уровня устройства и с «ыхода инвертора

12 реверсивного переключателя 2.

В момент времени t потенциал выходного напряжения аналогового интегратора I достигает величину +U (фиг.ЗЕ, момент t ).

При этом на выходе схемы 3 сравне— ния формируется импульс напряжения (фиг.5 ь) в момент t» который пос— тупает на первый вход коммутатора 5, при этом на его первом выходе в момент t устанавливается уровень лог гической "1" (фиг.Зу), который через элемент ИЛИ 6 запускает одновибратор

7, формирующий на своем выходе импульс напряжения длительностью (фиг.5 y) .

Во время действия импульса одновибратора 7 на управляющем входе коммутатора 5 на его третьем выходе формируется импульс, совпадаюший по времени с импульсом одновибратора 7 (фиг.5g) . Этот импульс открывает ключ

13 реверсивного переключателя 2, который пропускает компенсирующее напряжение опорного уровня +Б„ на второй информационный вход аналогового интегратора 1, вызывая уменьшение его выходного напряжения с момента (фиг.5 б). При этом напряжение на

c выходе схемы 3 сравнения изменяется с единичного уровня на нулевой.

По окончании действия импульса с выхода одновибратора 7 коммутатор 5 возвращается в исходное состояние, при этом на его выходах устанавли1339591

30 выр ажении . ваются нулевые уровни напряжений, ключи 13 и 14 реверсивного переключателя 2 размыкаются и интервал корректирующего воздействия +U на входе аналогового интегратора 1 заканчивается. Одновременно реверсивный счет— чик 8 получает отрицательное едийичное приращение содержимого, поскопьку во время действия íà его счетном входе импульса с выхода одновибратора 7, на входе установки режима счета присутствовал уровень логического

"0" с пятого выхода коммутатора 5.

Таким образом, аналоговому интегратору 1 сообщается корректирующая вольтсекундная порция воздействия на входе, соответствующая изменению его выходного напряжения на величину. л

dU = U

М где = R С вЂ” постоянная времени

11 16 инте грир ов ания по второму входу интегратора.

Этого воздействия достаточно, чтобы после корректирующего интервала времени, выходной потенциал интегратора 1 снова оказался внутри интервала U„.

Если выходной потенциал интегратора 1 под действием входного сигнала изменяется так, что в некоторый момент времени он оказывается равным величине -U напряжения, действующего на втором входе схемы 4 сравнения, то происходит процесс коррекции, аналогичный описанному. Отличие состоит только в том, что единичный уровень присутствует на втором, четвертом и пятом выходе коммутатора 5, при.этом замыкается ключ 14 реверсивного переключателя 2, отчего коррекция содержимого интегратора 1 производится под действием инверсного компенсирующего напряжения опорного уровня (с выхода инвертора.12 ), а реверсивный счетчик 10 получает положительное приращение содержимого на епиницу.

Потенциал опорного уровня, действующего на входе 9 уровня устройства, определяет величины корректирующих потенциалов +U и -U, а через них— цену единицы младшего разряда реверсивного счетчика 8 в вольт-секундном

В предлагаемом устройстве отсутствует запаздывание подключения компенсирующего напряжения к второму входу аналогового интегратора, а следовательно, отсутствует и запаздывание изменения выходного потенциала аналогового интегр атора в сторону убывания. При этом коррекция содержимого интегратора 1.производится сразу же по достижении выходным потенциа— лом последнего уровня масштабирующего потенциала.

В результате, последний поднят в предлагаемом устройстве до верхнего значения линейной характеристики (выходных напряжений от входных) интегратора 1, что в пересчете на вход эквивалентно подняло уровень возможных изменений амплитуд входных интегрируемых сигналов.

Предлагаемое устройство обладает также меньшим энергопотреблением от источников питания, что обусловлено в последнем работой блоков генератора импульсов (одновибратора), реверсивного переключателя и триггеров в ждущем режиме.

Формула изобретения

Аналого-цифровое интегрирующее устройство, содержащее аналоговый интегратор, первый информационный вход которого является входом устройства, а выход подключен к первому входу первой схемы сравнения, выход которой подключен к первому информационному входу коммутатора, первый выход которого соединен с входом установки режима счета реверсивного счетчика, выход которого является выходом устройства, и первый ключ, выход которого подключен к второму информационному входу интегратора, а управляющий вход соединен с вторым выхо-. дом коммутатора, о т л и ч а ю щ е ес я тем, что, с целью расширения динамического диапазона интегрируемых сигналов, введены элемент ИЛИ, одновибратор, инвертор, второй ключ и вторая схема сравнения, первый вход которой подключен к выходу интегратора, а выход соединен с вторым информационным входом коммутатора, вход опорного уровня устройства соединен с вторым входом первой схемы сравнения и с информационным входом первого ключа и через инвертор под5 1 33959 I ключен к второму входу второй схемы четвертый и пятый выходы которого сравнения и информационному входу через элемент ИЛИ подключены к входу второго ключа, выход которого соеди- одновибратора, выход которого соединен с вторым информационным входом

5 нен со счетным входом реверсивного интегратора, а управляющий вход под- счетчика и управляющим входом комму— ключен к третьему выходу коммутатора, татора.

77

1 5ыиа8у pe3epcu&roeo переключателя Г

Фиг.Я

С пыхай? .

08нс8ибраN0pN 7

К счвпчину8

l339591 советчику о

Ж Аа.

5 "и

Составитель С.Еелая

Техред М.Дидык

Корректор M.Лев чик

P едак тор А . Вор ович (Заказ 4224/40

Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1I3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, у . р л. П оектная 4

6 ф4

R) м 3

6 иуу

ug) пр. Ум.

У(Я

u(s> имййи. и„, и,д,ц, (б) Ь| иву

Ъх.1

1 ф

)Ц

С дыхооо оРноРцКроторг 7