Устройство для контроля магнитных интегральных схем памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств на цилиндрических магнитных доменах. Целью изобретения является упрощение устройства;Устройство для контроля магнитных интегральных схем памяти содержит счетчик 1, блок управления 2, блок оперативной памяти 3, мультиплексор 4. Счетный вход счетчика 1 является ин- .формационным входом 5 устройства. Вход сброса счетчика 1 подключен к первому входу блока управления 2 и является входом сброса 6 устройства. Второй вход блока управления 2 является первым управляющим входом 7 устройства , третий вход блока управления 2 - вторым управляющим входом 8 устройства, четвертый вход блока управления 2 - третьим управляющим входом 9 устройства. Информационный вход мультиплексора 4 соединен с выходом данных блока 3. Первый выход гультиплексора 4 соединен с информационным входом счетчика 1, а второй выход мультиплексора 4 является выходом 10 устройства. Выход счетчика 1 соединен с входом данных блока 3. Первый выход 11 блока управления 2- соединен с входом разрешения приема на счетный вход счетчика 1, второй выход 12 блока управления 2-е входом разрешения записи по информационному входу счетчика 1, третий выход 13 блока управления 2-е входом установки режима чтения - записи блока 3, четвертый выход 14 блока управления 2 с входом выборки блока 3, пятый выход 5 блока управления 2 - с адресным входом блока 3, шестой выход 16 блока управления 2 с управляющим входом мультиплексора 4, 2 ил. е (Л со со со О5 СП 4

СОЮЗ СОБЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (5D 4 С 11 C 11/14

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3905408/24-24 (22) 30 ° 04,85 (46) 23,09.87, Вюл. № 35 (71) Московский энергетический институт (72) Н,О.Карпенко (53) 681.327,66 (088.8) (56) IEEE Trans, Nagn,, V,Mag-16, ¹ 2, 1980, р,424-430, Digest papers of IEFE Test Corf,, Philadelphia, 1980.

New York, 1980, р,50-55. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МАГНИТНЫХ ИНТЕГРАЛЬНЫХ СХЕМ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств на цилиндрических магнитных доменах, Целью изобретения является упрощение устройства;Устройство для контроля магнитных интегральных схем памяти содержит счетчик 1, блок управления 2, блок оперативной памяти 3, мультиплексор

Счетный вход счетчика 1 является информационным входом 5 устройства, Вход сброса счетчика 1 подключен к первому входу блока управления 2 и является входом сброса 6 устройства.

Второй вход блока управления 2 является первым управляющим входом 7 устройства, третий вход блока управления 2 — вторым управляющим входом 8 устройства, четвертый вход блока управления 2 — третьим управляющим входом 9 устройства. Информационный вход мультиплексора 4 соединен с выходом данных блока 3. .Первый выход мультиплексора 4 соединен с информационным входом счетчика 1, а второй выход мультиплексора 4 является выходом 10 устройства. Выход счетчика

1 соединен с входом данных блока 3.

Первый выход 11 блока управления 2. соединен с входом разрешения приема на счетный вход счетчика 1, второй выход 12 блока управления 2 — с входом разрешения записи по информационному входу счетчика 1, третий выход

13 блока управления 2 — с входом установки режима чтения — записи блока

3, четвертый выход 14 блока управления 2 — с входом выборки блока 3, пятый выход 15 блока управления 2 с адресным входом блока 3, шестой выход 16 блока управления 2 — с управляющим входом мультиплексора 4. 2 ил.

1339654

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств на цилиндрических магнитных доменах (ЦМД).

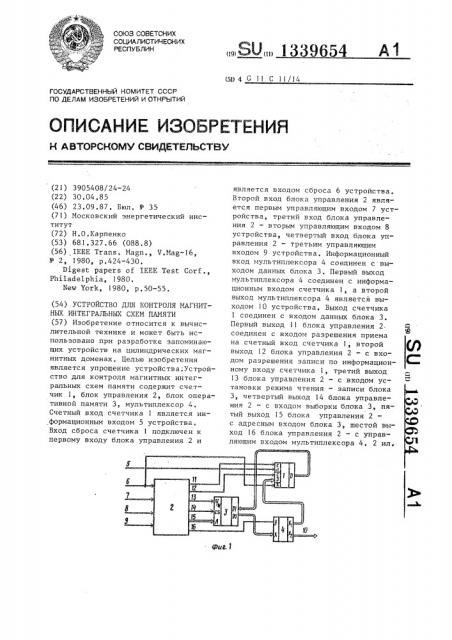

Целью изобретения является упрощение устройства, На фиг.! изображена блок-схема предлагаемого устройства; на фиг,2 блок-схема блока управления;

Устройство для контроля магнитных интегральных схем памяти содержит счетчик 1, блок 2 управления, блок 3 оперативной памяти, мультиплексор 4 °

Счетный вход счетчика 1 является информационным входом 5 устройства, вход сброса счетчика 1 подключен к первому входу блока 2 управления и является входом 6 сброса устройства, второй вход блока 2 управления является первым управляющим входом 7 устройства, третий вход блока 2 управления является вторым управляющим входом 8 устройства, четвертый вход блока управления 2 является третьим управляющим входом 9 устройства. Информационный вход мультиплексора 4 соединен с выходом данных блока 3, первый выход, мультиплексора 4 соединен с информационным входом счетчика 1, а второй выход мультиплексора 4 является выходом 10 устройства. Выход счетчика 1 соединен с входом данных блока 3. Первый выход 11 блока 2 управления соединен с входом разрешения приема на счетный вход счетчика

1; второй выход 12 блока 2 управления — с входом разрешения записи по информационному входу счетчика 1, третий выход 13 блока 2 управления--— с входом установки режима чтениязаписи блока 3; четвертый выход 14 блока 2 управления — с входом выборки блока 3; пятый выход 15 блока 2 управления — с адресным входом блока

3; шестой выход 16 блока управления

2 — с управляющим входом мультиплексора 4.

Блок 2 управления (фиг,2) включает пять элементов задержки 17 — 21, два элемента ИЛИ 22 и 23, два элемента И 24 и 25, элемент ИЛИ-НЕ 26, два

RS-триггера 27 и 28, счетчик 29 адреса. Первый и второй входы 6 и 7 блока 2 управления являются первым и вторым входами элемента ИЛИ 22, выход которого подключен к входу сброса счетчика 29, выход которого явля) (10

55 ется пятым выходом 15 блока 2 управления, Третий вход 8 блока 2 управления является первым входом элемента ИЛИ 23 и S-входом триггера 28, выход которого является шестьм выходом 16 блока 2 управления, Четвертый вход 9 блока 2 управления является вторым входом элемента ИЛИ 23, R-входом триггера 28, вторым входом элемента И 24 и вторым входом элемента И 25, выход которого является вторым выходом 12 блока 2 управления, Выход элемента ИЛИ 23 соединен с S-входом триггера 27 и с входом элемента !7 задержки, выход которого соединен с вторым входом элемента

ИЛИ-НЕ 26 и с входом элемента 18 задержки, выхоц которого соединен с первым входом элемента И 25 и с входом элемента 19 задержки, выход «оторого соединен с первым входом элемента И 24, R-входом триггера 27 и с входом элемента 20 задержки, выход которого соединен с первым входог элемента И31И-НЕ 26 и с входом элемента ?1 задержки, выход которого соединен со счетным входом счетчика 29.

Выход элемента И 24 является первым выходом 11 блока 2 управления, выход элемента ИЛИ- IE 26 является четвертым выходом 14 блока 2 управления„ выход триггера 27 является третьим выходом 13 блока 2 управления, Блок 3 оперативной памяти предназначен для хранения текущих значений числа сбоев, выданных накопительными регистрами проверяемой магнитной интегральной микросхемы, Каждо— му накопительному регистру соответствует отдельное слово в блоке 3. Накопительным регистрам с 1-го по К-й соответствует область адресного пространства с 0 до К-1, Предлагаемое устройство работает следующим образом °

Основными управляющими сигналами в этом режиме являются внешние сигналы "Данные готовы" (по входу 9 устройства) и "Новая страница" (по входу 7 устройства). Сигнал "Данные готовы" указывает на то, что с проверяемой магнитной интегральной схемы считан новый бит, а сигнал "Новая страница" — на то, что начинается считывание нового блока данных из магнитной интегральной схемы. По сигналу "Данные готовып блок управления

2 вырабатывает пять вспомогательных

1339654 аинхроимпульсов, формируемых элементами задержки 17-21, Первый сигнал Данные готовы" устанавливает в состояние "0" выход блока 2 управления, подключенный к

5 управляющему входу мультиплексора 4, что приводит к переключению выхода данных блока 3 на информационный вход счетчика 1 ошибок, 10

Очередность действий по сигналу

"Данные готовы" следующая: выход 13 блока 2 управления задает режим чтения блока 3, выход 14 блока 2 управления выдает сигнал выборки блока 3, 15 по сигналу с выхода 12 блока 2 управления выходные данные блока 3 заносятся в счетчик 1 ошибок, сигнал с выхода 11 блока 2 управления разрешает прием на счетный вход счетчика 1, Zp

В случае наличия внешнего сигнала

"Ошибка" (по входу 5 устройства) содержимое счетчика увеличивается на

"1", выход 13 блока 2 управлений задает режим записи блока 3, выход 14 25 блока 2 управления вьдает сигнал выборки блока 3, по которому модифицированная или неизменная информация со счетчика 1 ошибки заносится в адресуемую ячейку блока 3, происходит 30 наращивание на "1" содержимого счетчика 29 адреса, При поступлении сигнала "Новая страница" происходит обнуление счет35 чика 29 адреса, что позволяет восста-. новить соответствие между адресным пространством блока 3 и опрашиваемыми накопительными регистрами магнитной интегральной схемы памяти, 40

Режим вывода данных в систему организуется внешним сигналом "Пересылка" (по входу 8 устройства)., Для вывода из блока К слоев подается К сиг налов "Пересылка". Вьдача каждого слова сопровождается очисткой выбранной ячейки блока 3, Первый сигнал "Пересылка" переклю- 50 чает мультиплексор 4 на подачу данных с выхода данных блока 3 на выход IG устройства.

Очередность операций по сигналу

"Пересылка" следующая: выход 13 блока 2 управления задает режим чтения блока 3, выход 14 блока 2 управления выдает сигнал выборки блока 3, и считанные данные оказываются на выходе устройства, выход 13 блока 2 управления задает режим записи блока 3, выход 14 блока 2 управления выдает сигнал выборки блока 3; по которому в адресуемую ячейку памяти заносится нулевая информация с выхода счетчика 1 ошибок, содержимое счетчика 29 адреса наращивается на "1".

Формула и з о б р е т е н и я

Устройство для контроля магнитных интегральных схем памяти, содержащее счетчик и блок управления, о т л и— ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит блок оперативной памяти и мультиплексор, причем счетный вход счетчика является информационным входом устройства, вход сброса счетчика подключен к первому входу блока управления и является входом сброса устройства,. второй, третий и четвертый входы блока управления являются соответственно первым, вторым и третьим управляющими входами устройства, первый выход блока управления соединен с входом разрешения приема по счетному входу счетчика, второй выход — с входом разрешения записи по информационному входу счетчика, третий выход — с входом установки режима чтения-записи блока оперативной памяти, четвертый выход — с входом выборки блока оперативной памяти, пятый выход с адресным входом блока оперативной памяти, шестой выход — с управляющим входом мультиплексора, информационный вход которого соединен с выходом данных блока оперативной памяти, вход данных которого соединен с выходом счетчика, информационный вход которого подключен к первому выходу мультиплексора, второй выход которого является информационным выходом устройства, 1339654

Составитель 1О,Розенталь

Техред М.Дидык Корректор М.Пожо

Редактор Н.Лазаренко

Заказ 4232/44

Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д,4/5

Производственно-полиграфическое предприятие, г,Ужгород, ул.Проектная, 4