Постоянное запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в блоках постоянных запоминающих устройств (ПЗУ) микропроцессорных контроллеров. Цель изобретения - повышение быстродействия. Поставленная цель достигается введением в устройство мультиплексора 7, элемента ИЛИ 5, блока 9 сравнения и D-триггера 11. Введение указанных элементов обеспечивает проведение сигнатурного контроля содержимого ПЗУ в промежутках между обращениями. 2 ил. (Л Фиг./

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU<» 1339658 А1 (50 4 G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

r PÄ.г, ...Н А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ.(21) 3737552/24-24 (22) 03,05.84 (46) 23.09.87. Вюл. - 35 (71) Ленинградский институт авиационного приборостроения и Специальное конструкторское бюро систем промышленной автоматики Чебоксарского производственного объединения "Промпри- бор" (72) В.А.Г>ородулин, В.Н.Елизаров и А.A.Иванов (53) 681.327.66(088.8) (5e) Авторское свидетельство СССР

М 777742, кл. С 11 С 29/00, 1979.

Theus С., Leutigen Н. А SelfTesting R0I: Device — in Dig, of

Рар. 1981. — IEEE Jnternational SolidState Circuits Conferense, 1981, February, h - 81 СН 1588-3, р. 176-177, 270: (54) ПОСТОЯННОЕ ЗАПОИИНАЫЦЕЕ УСТРОЙСТВО С CAIIOKOHTPOJIEII (57) Изобретение относится к вычислительной технике и может быть использовано в блоках постоянных запоминающих устройств (ПЗУ) микропроцессорных контроллеров. Цель изобретения повышение быстродействия. Поставленная цель достигается введением в устройство мультиплексора 7, элемента ИЛИ 5, блока 9 сравнения и D-триггера 11. Введение указанных элементов обеспечивает проведение сигнатурного контроля содержимого ПЗУ в промежутках между обращениями. 2 ил.

1339658!!зоГретение относится к вычислительной технике и мох;ет быть использовано в блоках по стоянных запоминающих устройств (ПЭУ) микропроцессор5 ных контроллеров.

Цель изобретения — повышение бы— стродействия устройства.

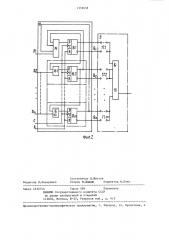

На фиг.l изображена электрическая схема предлагаемого устройства! на фиг.2 — электрическая схема сигнатурного анализатора и блока сравнения °

Устройство содержит вход 1 адреса, вход 2 управления режимом работы, вход 3, блок 4 управления, элемент

ИЛИ 5, счетчик 6, мультиплексор 7, накопитель 8, блок 9 сравнения, сигнатурный анализатор 10, D-триггер 11, выход 12 данных и выход 13 ошибки устройства. 20

Сигнатурный анализатор 10 (фиг. 2) содержит сумматор 14 по модулю два, группу элементов HCKSIM×ÀIPÖÅE ИЛИ

15. 1,..., 5.m-! и группу D-триггеров

16. 1,..., 16.m. Блок 9 сравнения со- 25 держит группу перемычек 17, 1,...,, 17.тп и элемент И 18.

Работа устройства (фиг. 1) начинается с подачи сигнала логической

"1" на вход 3. Этот сигнал переводит в режим прерывания блок 4 управления и устанавливает в нулевое состояние

D-триггер 11 Сигнал со входа 3 начального сброса, воздействуя через элемент ИЛИ 5 на входы сброса счетчика 6 и сигнатурного анализатора 10, устанавливает их триггеры в нулевое состояние. Если после снятия сигнала начального сброса на вход 2 подается логическая "1", то устройство осущест- 40 вляет чтение данных, хранящихся в накопителе 8 по адресу, принимаемому с входа 1. При этом сигнал с входа

2 устройства поступает на управляющий вход мультиплексора 7 и разрешает про-45 хождение сигналов с входа 1 на адресные входы накопителя 8. Считываемые из накопителя 8 данные поступают на выход 12 данных. Единичный сигнал с входа 2 удерживает блок 4 управления 5р в режиме прерывания генерации, поэтому во время чтения данных из накопителя 8 по адресу, определяемому сигналами на входе адреса 1, приема этих данных в сигнатурный анализатор !О и изменения состояния счетчика 6 не. происходит. После снятия сигнала логическж . "1" с входа ? мультиплексор 7 отключает адресные входы накопителя

8 от входа адреса H подключает их к группе информационных выходов счетчика 6. Сигнал логического "0" на входе 2 переводит блок 4 управления в режим генерации импульсов управления и„ если приход нового сигнала логическои "!" на вход 2 не прервет начавшийся в блоке 4 управления процесс генерации импульсов, то через промежуток времени, достаточный для установления данных на выходе накопителя 8, на выходе блока 4 управления появится единичный импульс, фронт которого вызовет запись в сигнатурный анализатор 10 данных с выходов накопителя 8. Эти данные хранятся в накопителе 8 по адресу 00...0, При записи данных в сигнатурный анализатор

10 они складываются по модулю два сумматором 14 и элементами !!СКЛ!ЗЧА10!1, ЕЕ

ИЛИ 15.1,....,15.m-l с содержимым триггеров 16.1 16.m, а результат суммирования записывается в этих триггерах. Спад импульса на выходе блока

4 управления вызывает инкремент содержимого счетчика 6 на единицу. Таким образом подготавливается считывание данных из накопителя 8 по адресу

00...01. Процесс считывания данных из последовательных разрядов накопителя 8 и записи (или иначе — сжатия) этих данных в сигнатурном анализаторе 10 протекает и далее, вплоть до достижения адреса 11...1, прерываясь лишь на время подачи сигнала логической "1" на вход 2, После записи по фронту импульса с номером 2" в сигнатурный анализатор 10 данных„ расположенных в накопителе 8 по адресу

11...1, инкремент содержимого счетчика 6 вызывает появление "1" на выходе переполнения. По фронту сигнала переполнения в D-триггере 11 происходит фиксация выходного сигнала блока

9 сравнения, который формируется следующим образом, Полученное в результате сжатия данных всех адресов накопителя 8 содержимое триггеров 16,1„...

16,m сигнатурного анализатора 10 (т,е, сигнатура) подается через перемычки 17.1...,,17.m на входы элемента И 18, С помощью этих перемычек задается эталонная сигнатура, В данном случае на перемычках задана эта— лонная сигнатура 11 ° . ° 1. Если содержимое сигнатурного анализатора также окажется равным !1...1, единичные сигналы с прямых выходов всех триггеров

1339658

Таким образом, предлагаемое устройство обеспечивает ту же достоверность контроля, что и известное устройство, поскольку для сжатия данных н обоих случаях используются сигнатурный анализатор, но при повьппенном быстродействииии.

40

16.1.. .,16.m пройдут через перемычки 17„1. ..1/,m на входы элементов

И 18. Тогда на его выходе появляется сигнал логическои "1". Если же хотя

5 бы н одном разряде содержимое сигнатурного анализатора 10 отлично от

11...1, то на выходе элемента И 18 появляется сигнал логического "О".

Таким образом, логическая "1" на вы- 10 ходе 13 означает, что устройство исправно, а 01 — неисправно, Сигнал с выхода переполнения счетчика 6 воздействует через элемент ИЛИ 5 на входы сброса счетчика 6 и сигнатурного )5 анализатора 10 ° При этом сигнал переноса счетчика 6 снимается и начинается следующий цикл контроля накопителя 8, Так как перебор и сжатие содержимого последовательных адресов нако- 20 пителя прерывается сразу же по поступлению сигнала на вход 2, то содержимое накопителя 8 выдается устройством на вход 12 данных без какихлибо дополнительных задержек на конт- ". роль. С другой стороны, самоконтроль устройства производится между чтением данных накопителя, не требуя в отличие от известного устройства прерывания работы вычислительной системы на время проведения самоконтроля устройства.

Ф о р м у л а и з о б р е т е н и я

Постоянное запоминающее устройство с самоконтролем, содержащее счетчик, накопитель, сигнатурный анализатор, блок управления, первый вход которого является нходом начального сброса устройстна, выход блока управления соединен со счетным входом счетчика и с тактовым входом сигнатурного анализатора, нходы данных которого соединень| с выходами накопителя, второй вход блока управления является входом упранления режимом работы устройства, о т л и ч а ю щ е е с я тем, что, с целью повыше- ния быстродействия, оно содержит элемент ИЛИ, блок сравнения, D-триггер и мультиплексор, первая группа информационных входов которого является адресным входом устройства, вторая группа информационных входов мультиплексора соединена с группой информационных выходов счетчика, выход переполнения которого соединен со стробирующим входом D-триггера и первым входом элемента ИЛИ, выход которого соединен с входами сброса счетчика и сигнатурного анализатора, а второй вход элемента ИЛИ соединен с входом сброса D-триггера и первым входом блока управления, выход D-триггера является выходом ошибки устройстна, первый вход блока управления соединен с управляющим входом мультиплексора, выходы которого соединены с адресным входом накопителя, выходы которого являются выходом данных устройства, выходы сигнатурного анализатора соединены с входами блока сравнения, выход которого соединен с информационным входом D-триггера, 1339658

Составитель Н,Шустов

Техред М,Дидык Корректор М,Пожо

Редактор Н.Лазаренко

Заказ 4232/44 Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1l3035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул, Проектная, 4