Регулируемый преобразователь переменного напряжения в переменное

Иллюстрации

Показать всеРеферат

-Изобретение относится к электротехнике . Цель изобретения - повышение надежности и исключение высших гармоник в кривой питающего напряжения . Регулирование напряжения осуществляют изменением отношения числа полупериодов сети, при которых на группы встречно-параллельно включенных тиристоров 14 подаются запускающие импульсы к числу полупериодов сети, при которых на выходах блоков 9 и 10 формирования управляющих импульсов запускающие импульсы отсутствуют. Блок логики 13 обеспечивает включение групп встречно-параллельно включенных тиристоров 14 в начале полупериода сетевого напряжения, поля{)- ность которого противоположна полярности последнего полупериода сетевого напряжения в предыдущем интервале проводимости. Это позволяет исключить режим насьпцения трансформатора и вероятность сверхдопустимого тока нагрузки . 3 ил. i (Л С СлЭ со |Х эо

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) А1 (59 4 02 5 257

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Риз. 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4014208/24-07 (22) 31.01. 86 (46) 23,09,87. Бюл. Ф 35 (71) Куйбышевский политехнический институт нм. В.В.Куйбьппева (72) А.И.Данилушкин и Л.В,Синдяков (53) 621.314.2(088.8) (56) Авторское свидетельство СССР

В 471578, кл, С 05 F 1/66, 1975.

Патент США У 3925633, кл. 219-10.49 (Н 05 В 5/04).

Авторское свидетельство СССР

Ф 851691, кл. Н 02 М 5/257, кл. G 05 F 1/44. (54) РЕГУЛИРУЕМЫИ ПРЕОБРАЗОВАТЕЛЬ

ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ПЕРЕМЕННОЕ (57) .Изобретение относится к электротехнике. Цель изобретения — повышение надежности и исключение высших гармоник в кривой питающего напряжения. Регулирование напряжения осуществляют изменением отношения числа полупериодов сети, при которых на группы встречно-параллельно включенных тиристоров 14 подаются запускающие импульсы к числу полупериодов сети, при которых на выходах блоков 9 и 10 формирования управляющих импульсов запускающие импульсы отсутствуют.

Блок логики 13 обеспечивает включение групп встречно-параллельно включенных тиристоров 14 в начале полупериода сетевого напряжения, полярность которого противоположна полярности последнего полупериода сетевого напряжения в предыдущем интервале проводимости. Это позволяет исключить режим насыщения трансформатора и вероятность сверхдопустимого тока нагрузки. 3 ил.

1339819

Изобретение относится к электротехнике, а именно к устройствам для регулирования напряжения потребителей переменного тока промышленной и пос вышенной частот.

Цель изобретения — повышение надежности и исключение высших гармоник в кривой питающего напряжения.

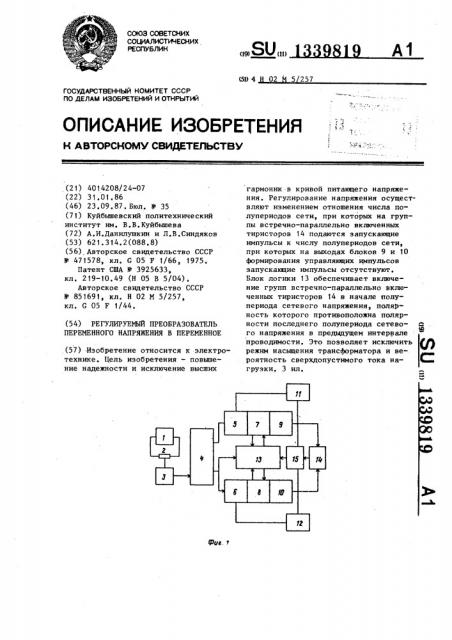

На фиг. 1 представлена блок-схема ð предлагаемого устройства, на фиг,2 электрическая схема блока логики; на фиг. 3 — временная диаграмма, поясняющая работу устройства.

Устройство содержит источник 1 питания, задатчик 2, генератор 3 пилообразного напряжения, блок 4 развязки каналов управления, два блока 5 и 6 формирования сигналов управления, два блока 7 и 8 коммутации,,два блока 9 и 10 формирования управ-, ляющих импульсов, два блока 11 и 12 формирования синхронизирующих импульсов, блок 13 логики, две группы встречно-параллельно включенных тирис-25 торов 14, соединенные последовательно с нагрузкой 15.

Блок 13 логики (фиг. 2) содержит трансформатор 16 тока, два диода 17 и 18, два нуль-органа 19 и 20, логи- д0 ческий элемент HE 2 1, два блока 22 и 23 формирования задержки сигнала управления, причем вход трансформатора 16 тока. подсоединен к нагрузке, один выход через диод 17 и первый нуль-орган 19 подсоединен к первому входу блока 22 формирования задержки сигнала управления, второй выход через диод 18 и второй нуль-орган 20 подсоединен к первому входу блока 23 формирования задержки сигнала управления, к вторым входам первого 22 и второго 23 блоков формирования задержки сигнала управления подсоединен выход первого логического элемента НЕ 4>

21, вход которого и третий вход первого 22 и второго 23 блоков формирования задержки сигналов управления подсоединены к первому выходу блока

4 развязки каналов управления, четвертый вход первого блока 22 формирования задержки сигнала управления подсоединен к одному из выходов первого блока 7 коммутации, четвертый вход второго блока 23 формирования задержки сигнала управления подсоединен к одному из выходов второго блока

8 коммутации, пятый вход первого блока 22 формирования задержки сигнала управления подсоединен к выходу второго нуль-органа 20, пятый вход второго блока 23 формирования задержки сигнала управления подсоединен к выходу первого нуль-органа 19, выход первого блока 22 формирования задержки сигнала управления подсоединен к одному из входов первого блока 7 коммутации, выход второго блока 23 формирования задержки сигнала управления подсоединен к одному из входов второго блока 8 коммутации.

Блок 22 (23) формирования задержки сигнала управления содержит последовательно соединенные первый логический элемент 2И-НЕ 24 (25), второй логический элемент НЕ 26 (27), логическую память 28 (29), третий логический элемент НЕ 30 (31), второй логический элемент 2И-НЕ 32 (33), четвертый логический элемент НЕ 34 (35), третий логический элемент 2И-НЕ

36 (37), пятый логический элемент НЕ

38 (39). Кроме того, второй блок 23 формирования задержки сигнала управления содержит дополнительно узел 40 гальванической развязки, выполненный, например, на оптронных резисторах, вход которого подсоединен к выходу четвертого логического элемента НЕ

35, а выход — к первому входу третьего логического элемента 2И-НЕ 37, причем выход пятого логического элемента HE 38 (39) блока 22 (23) формирования задержки сигнала управления подсоединен к одному из входов соответствующего блока 7 и 8 коммутации, первый вход первого логического элемента 2И-НЕ 24 (25) подсоединен к выходу первого или второго нуль-органа 19 и 20 соответственно, а второй вход — к выходу первого логического элемента НЕ 21, вход которого и один из входов второго логического элемента 2И-HE 32 (33) подсоединены к одному из выходов блока развязки каналов управления, второй вход третьего логического элемента 2И-НЕ 36 (37) блока 22 (23) формирования задержки сигнала управления подсоединен к одному из выходов соответствующего блока 7 или 8 коммутации, один из входов логической памяти 28 первого блока 22 формирования задержки сигнала управления подсоединен к выходу второго нуль-органа 20, а один из входов логической памяти 29 второго блока 23 формирования задержки сигнала управ1339819 ления подсоединен к выходу первого нуль-органа 19.

Каждый из блоков коммутации 7 и 8 содержит триггер образованный логи1

5 ческими элементами 41-44, выход которого подсоединен к четвертому входу блока 22 формирования задержки сигнала управления, и два логических элемента 2И-HE 45 и 46, один из входов которых подсоединен к выходу блока 22 формирования задержки сигнала управления. Предлагаемое устройство может быть реализовано, например, на элементах серии 511.

Устройство работает следующим образом.

Пока сигналы управления отсутствуют, сигнал на выходе блока 4 равен нулю, все тиристоры групп встречно20 параллельно включенных тиристоров 14 закрыты, и ток нагрузки 15 равен О, Логический элемент НЕ 21 формирует на выходе сигнал логической " 1", а нуль-органы 19 и 20 формируют логический "0". При отсутствии сигнала управления на выходе блока 4 сигнал на выходе блоков 7 и 8 равен 0 и логические элементы обоих блоков 22 и

23 формируют на выходе логических

30 элементов НЕ 38 и 39 сигнал, соответствующий логическому "0", При подаче сигнала задания с задатчика 2 в момент t< (фиг. 3) блок

4 Аормирует сигнал логической "1", который воздействует на логический элемент HE 21 и логические элементы

2И-НЕ 32 и 33. Так как в момент t, подачи сигнала управления тиристоры закрыты, нуль-органы 19 и 20 формируют на выходе сигнал "0". На входы логических элементов 2И-НЕ 24 и 25 блоков 22 и 23 Аормирования задержки сигнала управления воздействуют

40 сигналы 0, Логический элемент 2И-НЕ 45

24, логические элементы НЕ 26 и 30, логическая память 28 и логический элемент 2И-НЕ 25, логические элементы

НЕ 27 и 31, логическая память 29 Аормируют на выходе элементов НЕ 30 и 31 50 сигнал логической "1", который воздействует на логические элементы 2ИНЕ 32 и 33 соответственно. На второй вход каждого из логических элементов 2И-НЕ 32 и 33 в момент времени воздействует сигнал " 1" с выхода блока 4. Сигнал "0" с выхода логического элемента 2И-HE 32 через логический элемент НЕ 34 воздействует на логический элемент 2И-НЕ 36. На второй вход логического элемента 2И-HE

36 воздействует сигнал с выхода блока 7 коммутации, синхронизированный передним фронтом с моментом прохождения через 0 напряжения сети (момент t ). Логический элемент 2И-НЕ

36 и логический элемент НЕ 38 формируют в момент с сигнал логической

"1", который воздействует на блок 7 коммутации, разрешая подачу управляющих импульсов на тиристоры первой группы групп встречно-параллельно включенных тиристоров 14. Сигнал "1" с выхода логического элемента 2И-НЕ

33 в момент г, через логический элемент НЕ 35 и узел 40 гальванической развязки воздействует на логический элемент 2И-НЕ 37, на второй вход которого воздействует сигнал с выхода блока 8 коммутации, синхронизированный с моментом прохождения через нуль напряжения сети. В момент t логический элемент 2И вЂ” НЕ 37 и логический элемент НЕ 38 формируют логическую

"i" которая воздействует на блок 8 коммутации, разрешая подачу управляющих импульсов на тиристоры второй группы групп встречно-параллельно включенных тирнсторов 14, Таким обра= зом, при первоначальном включении устройства оба канала управления полу. чают разрешение на включение тиристоров в момент с прохождения напряжения сети через нуль. Блоки 9 и 10 воздействуют на тиристоры групп встречно-параллельно включенных тиристоров 14, осуществляя их поочередную коммутацию.

В момент t> окончания сигнала управления сигнал логического "0" с выхода блока 4 воздействует на логический элемент НЕ 21 и логические элементы 2И-НЕ 32 и 33, Пусть момент с окончания сигнала управления с выхода блока 4 совпадает с интервалом проводимости первой группы тиристоров групп встречно-параллельно включенных тиристоров 14.

В этом случае в момент t> на входы логического элемента 2И-НЕ 24 воздействуют две логические "1", логический элемент НЕ 26 формирует логическую

"1", которая воздействует на логическую память 28 ° Последняя формирует на выходе сигнал "1", который через логический элемент НЕ 30 воздействует на один из входов логического эле1339819 мента 2И-НЕ 32. На второй вход логического элемента 2И-НЕ 32 воздействует сигнал логического "О" с выхода блока 4i

Сигнал "1" с выхода логического элемента 2И-НЕ 32 воздействует через логический элемент НЕ 34 на один из входов логического элемента 2И-НЕ 36, на второй вход которого воздействует 10 сигнал логического "О" с выхода блока

7. Логический элемент 2И-НЕ 36 воздействует через логический элемент

38 на вход блока 7, запрещая подачу управляющих импульсов на тиристоры 15 первой группы бивентиля.

Одновременно в момент t на один вход логического элемента 2И-НЕ 25. воздействует логическая "1" с выхода логического элемента НЕ 2 1, а на вто- 20 рой вход — логический "0" с выхода нуль-органа 20. Логический элемент

2И-НЕ 25, логические элементы 27 и

31 и логическая память 29 формируют на выходе логического элемента НЕ 3 1 логическую "1", которая воздействует на один вход логического элемента

2И-НЕ 33, на второй вход которого воздействует сигнал "О" с выхода блока 4. Сигнал "1" с выхода логического элемента 2И-НЕ через логический элемент НЕ 35, узел 40 воздействует на один из входов логического элемента

2И-HE 37, на второй вход которого воздействует сигнал "О" с выхода бло- 35 ка 8 коммутации, Логический элемент

2И-HE 37 через логический элемент

НЕ 39 воздействует на вход блока коммутации, запрещая подачу управляющих импульсов на тиристоры второй группы 40 групп встречно-параллельно включенных тиристоров 14, В момент t< подачи очередного сиг нала управления с выхода блока 4 сигнал логической "1" через логический элемент НЕ 21 воздействует на один из входов логического элемента 2И-HE

24 первого блока 22, на второй вход которого воздействует сигнал "0" с выхода нуль-органа 19. Так как в мо- ВО мент t сигнал на втором входе логической памяти 28 равен О, логический элемент 2И-НЕ 24, логические элементы

HE 26 и 30 и логическая память 28 своего состояния и логический элемент

HE 30 на выходе формируют сигнал "О".

Этот сигнал воздействует на один вход логического элемента 2И-НЕ 32, на второй вход которого воздействует сигнал логической "1" с выхода блока 4.

Логический элемент 2И-НЕ 32 формирует сигнал " 1", который через логический элемент HE 34 воздействует на один из входов логического элемента

2И-НЕ 36, на второй вход которого воздействует сигнал логической "1" с выхода блока 7, логический элемент

2И-НЕ 36 формирует сигнал " 1", который через логический элемент НЕ 38 воздействует на блок 7, запрещая подачу управляющих импульсов на тиристоры первой группы групп встречнопараллельно включенных тиристоров 14.

Одновременно в момент t логический элемент ?И-НЕ 25, логические элементы HE 27 и 31 и логическая память

29 формируют на выходе логического элемента HE 3 1 сигнал логической " 1", который воздействует на один вход логического элемента 2И-НЕ 33, на второй вход которого воздействует сигнал "1" с выхода блока 4. Выходной .сигнал "0" логического элемента

2И-HE 33 через логический элемент

НЕ 35 и узел 40 воздействует на один вход логического элемента 2И-НЕ 37, на второй вход которого воздействует сигнал "О" с выхода блока 8. Выходной сигнал " 1" с выхода логического элемента 2И-НЕ 37 через логический элемент НЕ 39 воздействует на вход блока 8, запрещая подачу управляющих импульсов на тиристоры второй группы групп встречно-параллельно включенных тиристоров 14 до момента с . В момент времени t блок 8 коммутации формирует на выходе синхронизированный с нулем питающего напряжения сигнал логической "1", который воздействует на второй вход логического элемента

2И-HE 37. Последний формирует на выходе сигнал логического "О", который через логический элемент НЕ 39 воздействует на блок 8, разрешая подачу управляющих импульсов на тиристоры второй группы групп встречно-параллельно включенных тиристоров, B момент t6 формирования первого импульса тока нагрузки 15 нуль-орган

20 формирует сигнал "I", который воздействует на второй вход логической памяти 28 первого блока 22. Логическая память 28 формирует сигнал "О", который через логические элементы

HE 30, 34 и 38 и логические элементы

2И-НЕ 32 и 36 воздействует на вход блока 7, разрешая подачу управляющих

1339819

Формула изобретения

40 задержки сигнала управления подсое5 динен к выходу первого нуль-органа, а вторые входы вторых логических элементов 2И-НЕ первого и второго блоков формирования задержки сигналов управ50 ления подсоединены K выходу блока развязки каналов управления. импульсов на тиристоры первой группы групп встречно-параллельно включенных тиристоров 14.

Регулируемый преобразователь переменного напряжения в переменное, содержащий две группы встречно-параллельно включенных тиристоров и схему управления, состояшую из последовательно включенных задатчика, генератора пилообразного напряжения, блока развязки каналов управления, двух блоков формирования сигналов управления, двух блоков коммутации, двух бло ков формирования синхронизирующих импульсов, отличающийся . тем, что, с целью повышения надежности и исключения высших гармоник в кривой питающего напряжения, введены блок логики, содержащий трансформатор тока, два диода, два нуль-органа, логический элемент НЕ, первый и второй блоки формирования задержки сигналов управления, каждый из которых содержи последовательно соединенные первый логический элемент 2И-НЕ, второй логический элемент НЕ, логическую память, третий логический элемент НЕ, второй логический элемент 2И-НЕ, четвертый логический элемент НЕ, третий логический элемент 2И-НЕ, пятый логический элемент НЕ, кроме того, второй блок формирования задержки сигналов управления содержит узел гальванической развязки, причем вход трансформатора тока включен в цепь нагрузки, один выход через диод и первый нульорган подсоединен к первому входу пер вого логического элемента 2И-НЕ первого блока формирования задержки сигналов управления, второй выход трансформатора тока через второй диод и второй нуль-орган подсоединен к первому входу первого логического элемента 2И-НЕ второго блока формирования задержки сигналов управления, выход первого логического элемента 2ИНЕ первого блока формирования задерж10

25 т

35 ки сигналов управления подсоединен к первому входу логической памяти, выход которой подсоединен через третий логический элемент НЕ к первому входу второго логического элемента

2И-НЕ, выход которого подсоединен через четвертый логический элемент

НЕ к третьему логическому элементу

2И-НЕ, выход которого через пятый логический элемент НЕ подсоединен к входам логических элементов 2И-НЕ первого блока коммутации, а выход первого блока коммутации подсоединен к второму входу третьего логического элемента 2И-НЕ первого блока формирования задержки сигналов управления, выход первого логического элемента

2И-НЕ второго блока формирования задержки сигналов управления подсоединен к первому входу логической памяти, выход которой подсоединен через третий логический элемент НЕ к первому входу второго логического элемента 2И-НЕ, выход которого подсоединен через четвертый логический элемент НЕ к входу узла гальванической развязки, выход которого подсоединен к первому входу третьего логического элемента 2И-НЕ, второй вход которого подсоединен к выходу второго блока коммутации, а выход через пятый логический элемент НЕ к входу второго блока коммутации, вторые входы первых логических элементов 2И-НЕ первого и второго блоков формирования задержки сигнала управления подсоединены через логический элемент НЕ к выходу блока развязки каналов управления, второй вход логической памяти первого блока формирования задержки сигнала управления подсоединен к выходу второго нуль-органа, второй вход логической памяти второго блока формирования

1339819

Фиг. 2

Редактор H.Òóïèöà

Заказ 4241!52

Тираж 659 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, R-35, Раушская наб,, д, 4/5

Производственно-полиграфическое предприятие, r.Óæãîðîä, ул.Проектная, 4

ЬИмент

Элемент

2лемент

Элемент чеФмтп

Ъмменнт лемент

Зле мент

Элемент чччч) Элемент

Ялемент

Зле мент

Яммент

На3

Составитель И,Головинова

Техред М,Дидьк Корректор С,Шекмар