Сумматор по модулю два

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в импульсных логических схемах различного назначения. Цель изобретения - повышение достоверности работы сумматора. Входные сигналы поступают на входы второго 8 и третьего 9 узлов дифференцирования, положительные сигналы с выходов которых поступают соответственно на входы второго 10 и третьего 11 формирователей импульсов. Сигналы с выходов формирователей 10 и 11 импульсов поступают соответственно на первый и второй входы элементов ИЛИ-НЕ 1 и И-НЕ 2. На выходе элемента ИЛИ-НЕ 1 формируется импульс, длительность которого равна логической .сумме длительностей входных сигналов, на выходе элемента И-НЕ 2 формируется сигнал , длительность которого равна логическому произведению длительностей входных сигналов. Сигнал с выхода элемента ИЛИ-НЕ 1 через первый узел 5 дифференцирования поступает на третий вход элемента И 6, выход которого через первый формирователь 7 импульсов соединен с выходом сумматора. Выход элемента И-НЕ 2 через расширитель 3 импульсов соединен с вторым входом элемента И 6 и входом элемента 4 задержки, выход которого соединен с первым входом элемента И 6. 2 ил. с tS (Л 00 СО N О 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (gg4 G06 F 7 38

ОЙИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOIVlV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (6i) 1117633 (21) 4058720/24-24 (22) 21.04.86 (46) 07. 10. 87. Бюл. У 37 (72) А.Н.Барыленко, В.П.Мочалов, С.В.Руденко и В.И.Селезнев (53) 681.3(088.8) (56) Авторское свидетельство СССР

Р 1117633, кл. G 06 F 7/38, 1983. (54) СУММАТОР ПО МОДУЛЮ ДВА (57) Изобретение относится к вычислительной технике и может быть использовано в импульсных логических схемах различного назначения. Цель изобретения — повышение достоверности работы сумматора. Входные сигналы поступают на входы второго 8 и третьего 9 узлов дифференцирования, положительные сигналы с выходов которых поступают соответственно на входы второго 10 и третьего 11 формирователей импульсов . Сигналы с выходов

„„SU„„1343408 А 2 формирователей 10 и 11 импульсов поступают соответственно на первый и второй входы элементов ИЛИ-HE 1 и

И-HE 2. На выходе элемента ИЛИ-HE 1 формируется импульс, длительность которого равна логической .сумме длительностей входных сигналов, на выходе элемента И-НЕ 2 формируется сигнал, длительность которого равна логическому произведению длительностей входных сигналов. Сигнал с выхода элемента ИЛИ-НЕ 1 через первый узел

5 дифференцирования поступает на третий вход элемента И 6, выход которого через первый формирователь 7 импульсов соединен с выходом сумматора. Выход элемента И-НЕ 2 через расширитель 3 импульсов соединен с вторым входом элемента И 6 и входом элемента 4 задержки, выход которого соединен с первым входом элемента И 6.

2 ил.

f 343408

Изобретение относится к вычислительной технике, может быть использовано в импульсных логических схемах различного назначения и является усовершенствованием устройства по авт.св. 9 1117633.

Цель изобретения — повышение достоверности работы сумматора.

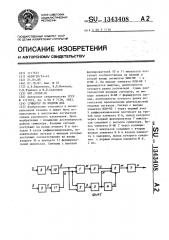

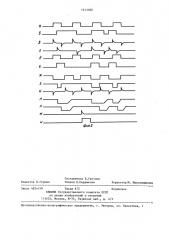

На фиг.1 приведена функциональная схема сумматора; на фиг.2 — временная диаграмма работы сумматора.

Сумматор по модулю два содержит элементы ИЛИ-НЕ 1 и И-НК 2, расширитель 3 импульсов, элемент 4 задержки, первый узел 5 дифференцирования, элемент И 6, первый формирователь 7 импульсов, второй 8 и третий 9 узлы дифференцирования, второй 10 и третий

11 формирователи импульсов, Сумматор по модулю два работает следующим образом.

Входные последовательности импульсов поступают на второй 8 и третий 9 узлы дифференцирования, дифференциру-: ются и своими передними фронтами запускают формирователи 10 и 11 импульсов. С выходов формирователей 10 и 11 импульсов последовательности импульсов поступают на элемент ИЛИ-НЕ 1.

Длительность сигнала, поступающего с выхода элемента ИЛИ-НЕ 1 на вход первого узла 5 дифференцирования, равна суммарной длительности информационных сигналов д и е. Запрещающий сигнал з, поступающий с выхода элемента И-НЕ 2 на вход расширителя 3 импульсов, имеет длительность совпадающих частей информационных сигналов.

Благодаря задержанному сигналу з, проходящему через элемент 4 задержки . на первый вход элемента И 6, сигналу И, проходящему на третий вход элемента И 6, устраняются ложные сигналы, вызываемые рассогласованием задних и передних фронтов информационных сигналов. Расширитель 3 импульсов и элемент 4 задержки построены таким образом, что суммарная длительность сигналов с их выходов равна сумме

10 максимальных длительностей входных информационных сигналов. Выход элемента И 6 подключен к входу первого формирователя 7 импульсов, выход которого является выходом сумматора.

Из временной диаграммы (фиг.2) видно, что достоверная. работа предла-. гаемого сумматора сохраняется при рассогласовании во времени входных

20 сигналов на величину, равную длитель.ности входного сигнала, и при искажениях длительностей сигналов практически на любую величину.

Формула изобретения

Сумматор по модулю два по авт. св.

11 1117633, о тлич aþùèé ñÿ тем, что, с целью повышения достовер30 ности работы, в него введены вторсй и третий узлы дифференцирования, второй и третий формирователи импульсов, причем входы второго и третьего узлов дифференцирования являются соот 5 ветственно первым и вторым входами сумматора, выходы второго и третьего узлов дифференцирования соединены с входами соответственно второго и третьего формирователей импульсов, выЕО ходы второго и третьего формирователей импульсов соединены соответственно с первыми и вторыми входами элементов ИЛИ-НE и И-HE.

1343408 фиа 2

Составитель В.Гречнев

Техред Л. Сердюкова

Редактор П.Гереши

Корректор М. Иаксимишинец

Заказ 4824/49

Тираж 672

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4