Усилитель считывания

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в полупроводниковых запоминающих устройствах на основе МДП-транзисторов. Целью изобретения является повьшение надежности усилителя считывания за счет уменьшения чувствительности к разбросу параметров транзисторов. Усилитель считывания содержит транзисторы 1,2 обратной свя зи, транзисторы 3-5 управления режимом, транзистор 6 пода1 I чи напряжения питания, информационные транзисторы 7,8, входы и выходы устройства. Усилитель работает в двух режимах: предзаряда и считывания . Чувствительность усилителя определяется минимальной величиной изменения потенциала JU на входахвыходах усилителя, при которой он надежно усиливает сигнал. Граничным условием срабатывания усилителя является условие U(.,-+411-11 2 Uc-2.-UTi , при котором открьшается один из транзисторов 1 или 2, где V и U. -напряжения стоков транзисторов 1 и 2 в начале цикла усиления сигнала. В данном усилителе в цикле предзаряда , , Up, Un-UT-2, где U - напряжение питанияj UT-, - пороговое напряжение транзистора 1 Иг ч пороговое напряжение транзистора 2 -и, следовательно , ли 0. Таким образом , разброс пороговых напряжений о транзисторов 1 и 2 не сказьшается на чувствительности усилителя,- минимальный сигнал считывания ли не зависит от параметров транзисторов. 2 ил. (Л СО 4 СО 4 4 ND 2

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (50 4 С 11 С 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ

3

1 15

Ри1.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4012657/24-24 (22) 13.12.85 (46) 07.10.87. Бюл. М- 37 (71) Московский институт электронной техники (72) В.В. Баринов и О.А. Титов (53) 681.327.6(088.8) (56) Караханян Э.P., Шилин В.А. Динамические интегральные схемы памяти с МДП-структурой. — 1984, с, 42, Авторское свидетельство СССР

9 769617, кл. G 11 С 7/60, 1980. (54) УСИЛИТЕЛЪ СЧИТЫВАНИЯ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано в полупроводниковых запоминающих устройствах на основе МДП-транзисторов. Целью изобретения является повышение надежности усилителя считывания за счет уменьшения чувствительности к разбросу параметров транзисторов. Усилитель считывания содержит транзисторы 1,2 обратной связи, транзисторы 3-5 управления режимом, транзистор 6 пода„„ И„„1343442 А 1 чи напряжения питания, информационные транзисторы 7,8, входы и выходы устройства. Усилитель работает в двух режимах: предзаряда и считывания. Чувствительность усилителя определяется минимальной величиной изменения потенциала 3U на входахвыходах усилителя, при которой он надежно усиливает сигнал. Граничным условием срабатывания усилителя является условие Uñ, +dU-Пт2=UÑ2-UT1 э при котором открьвается один из транзисторов 1 или 2, где U, и U — напряжения стоков транзисторов 1 и 2 в начале цикла усиления сигнала. В данном усилителе в цикле предэаряда

U7 Uc g Ul1 Н где Нд пряжение питания; U „— пороговое напряжение транзистора 1; UT —. пороговое напряжение транзистора 2 и, следовательно, дН = О. Таким образом, разброс пороговых напряжений транзисторов 1 и 2 не сказьвается на чувствительности усилителя,-минимальный сигнал считывания дП не зависит. от параметров транзисторов. 2 ил.

1343442 г < г

1 lg

25 .".<.<

Изобретение относится к цифровой вычислительной технике и может быть использовано в полупроводниковых запоминающих устройствах на основе

МДП-транзисторов.

Целью изобретения является повышение надежности усилителя считывания за счет уменьшения чувствительности к разбросу параметров транзисторов „

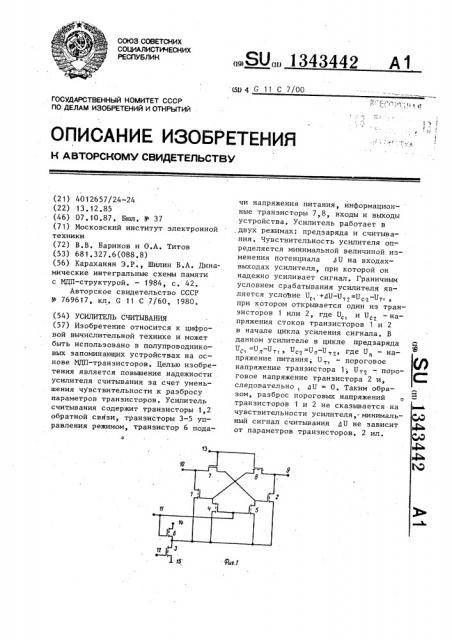

На фиг, 1 приведена схема усилителя считывания; на фиг, 2 — временная диаграмма напряжений в узлах усилителя во время работы, Усилитель считывания содержит первый 1 и второй 2 транзисторы обратной связи, первый 3, второй 4 и третий 5 транзисторы управления режимом, транзистор 6 подачи напряжения питания, первый 7 и второй 8 информационные транзисторы, информационные входы-выходы 9 и 10 соответственно л.огического "0" и логической 1, вход

11 управления предзаряда, первый 12 и второй 13 управляющие входы, шину

14 питания и шину 15 нуля.

Усилитель считывания работает в двух режимах: предзаряда и считывания (фиг. 2). Б режимс прецзаряд-. транзистор 3 управления режимом закрыт, а транзисторы 4 и 5 управления ре>г<имом открыты„ информационные тран-зисторы 7 и 8 закрыты, транзистор б подачи напряжения питания открыг,, емкости разрядных шин (не показаны), подключенные к информационным входам-выходам усилителя считывания, заряжаются через открытые транзи<.торы 1 и 2 обратг1ой связи (.àïðèìåð,, для разрядной шины логической п1 : информационный вход-выход 10 — тран-. зистор 1 — транзистор б -- шина 14 питания) до напряжения U -U„., где U — напряжение питания на шине гг

14, U. — пороговое напря><ение тран-г< зистора 1„ Соответственно напряжение на другом входе-вь;ходе усилителя считывания в режиме предз;гряда у< та=навливается П„-U,, где U...> - пороговое напряжение транзистора 2...;,ля нормальной работы усилителя считывания необходимо поддерживать потенциал управляющих сигналов в режиме предзаряда больше,, чем U„ U..

В режиме считывания информации на информационных входах-выходах 9 и 10 формируется небольшой сигнал считывания. После установления потенциалов на входе 11 управления предзаряда и на первом 12 и втором 13 управляющих входах (фиг. 2), соответствующих режиму считывания, транзисторы

4 и 5 управления режимом и транзисгор 6 подачи напряжения питания закрываются, а информационные транзисторы 7 и 8 и транзистор 3 управления режимом открываются и начинается процесс усиления сигнала считывания. При этом происходит перезаряд емкостей разрядных шин через одно из плеч -усилителя. либо по цепи транзистор 1 обратной связи — транзистор 3 управления режимом, либо по цепи транзистор 2 обратной связи— транзистор 3 управления режимом.

Чувствительность усилителя определяется минимальной величиной изменения потенциала dU на входах-выходах усилителя, при которой он надежно усиливает сигнал, Граничным условием срабатывания усилителя является условие Бс, +Л -Б,. =ггс †, при котором открывается один из транзисторов 1 или 2, где гг„ и П, напряжения стоков транзисторов 1 и 2 в начале цикла усиления сигнала.

В данном усилителе в цикле предзаряда гг „= U„-U„, Uc> = Бп и, слецовательно, <10 >

Усилитель считывания, содержащий первый и второй транзисторы обратной связи стоки которых являются сост ветственно информационными входамивыходами логической единицы и логического нуля усилителя, первый транзистор управления режимом, сток и исток которого подключены соответственно к истокам первого и второго транзисторов обратной связи и к шине нуля усилителя, затвор первого транзистора управления регглмом является первым управляющим входом усилителя, отличающийся тем, что, с целью повышения надежности усилителя за счет уменьшения чувствительности к разбросу параметров транзисторов, он содержит второй и третий

13434

Составитель В.Гордонова

Техред М.Дидык Корректор А.Обручар

Редактор И.Николайчук

Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4828/51

Производственно-.полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 транзисторы управления режимом, транзистор подачи напряжения питания, первый и. второй информационные транзисторы, истоки которых подключены соответственно к стокам первого и второго транзисторов обратной связи,, а стоки подключены к стоку третьего транзистора управления режимом и затвору второго транзистора обратной связи и соответственно к стоку второго транзистора управления режимом и затвору первого транзистора обратной связи, истоки второго и третьего транзисторов управления режимом и

42

lj транзистора подачи напряжения пита= ния объединены и соединены со стоком первого транзистора управления режимом, затворы второго и третьего транзисторов управления режимом и транзистора подачи напряжения питания объединены и являются входом управления предэаряда усилителя, затворы первого и второго информационных транзисторов объединены и являются вторым управляющим входом усилителя, а сток транзистора подачи напряжения питания подключен к шине питания.