Устройство для преобразования последовательного кода в параллельный

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может найти применение в системах передачи данных по цифровым каналам для преобразования последовательного кода в параллельный. Цель изобретения - повышение надежности устройства для преобразования последовательного кода в параллельный. Устройство содержит регистр 1 сдвига, элемент 2 И, генератор 3 тактовых импульсов , информационный вход 4, стробирующий вход 5, выход 6 опшбки.1 ил. 6 а (Л л+/ А 00 4 со ел ел NU

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 Н 03 М 9/00 с 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3961125/24-24 (22) 04.10.85 (46) 07.10.87. Бюл. М - 37 (72) Ю.Д.Кунев (53) 681.325(088.8) (56) Авторское свидетельство СССР

М 809160, кл. Н 03 M 9/00, )979.

80, 1 4 54 A 1 (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ (57) Изобретение относится к автоматике и вычислительной технике и может найти применение в системах передачи данных по цифровым каналам для преобразования последовательного кода в параллельный. Цель изобретения — повышение надежности устройства для преобразования последовательного кода в параллельный. Устройство содержит регистр 1 сдвига, элемент 2 И, генератор 3 тактовых импульсов, информационныи вход 4, стробируюший вход 5, выход б ошибки.1 ил. д

Составитель А,Авдеев

Редактор П.Гереши Техред М.Дидык Корректор M.Иароши

Тираж 901 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Заказ 4836/56

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

1 13

Изобретение относится к автоматике и вычислительной технике и может найти применение в системах передачи данных по цифровым каналам для преобразования последовательного кода в параллельный.

Цель изобретения — повышение надежности устройства для преобразования последовательного кода в параллельный.

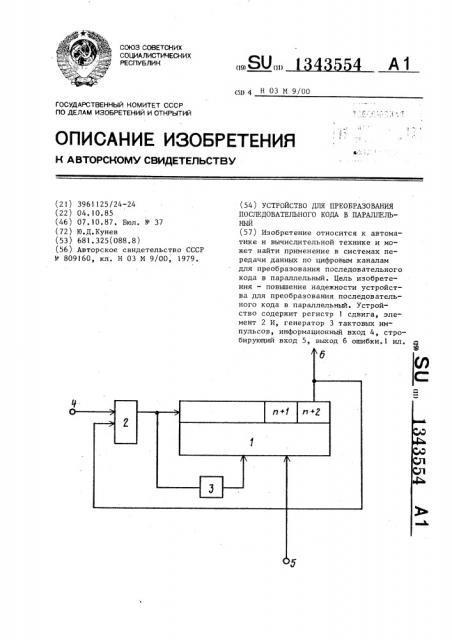

На чертеже представлена функциональная схема устройства.

Устройство для преобразования последовательного кода в параллельный содержит регистр l сдвига, элемент И 2, генератор 3 тактовых импульсов, информационный 4 и стробирующий 5 входы, выход 6 ошибки.

Устройство для преобразования последовательного кода в параллельный работает следующим образом, На вход 5 поступает сигнал, который записывает "1" в первый разряд регистра 1, а в остальные разряды

"0". Установка (n+2)-го разряда в исходное состояние открывает элемент И 2. По мере поступления кодовых импульсов на вход 4 регистр 1 осуществляет прием поступающей информации. Б случае приема ожидаемых и разрядов последовательного кода без сбоя в (n+1)-м и (n+2)-м разрядах регистра 1 окажется записанным код "10". Появление укаэанной комбинации свидетельствует об окончании преобразования последовательного кода в параллельный и сопровождается

43554 2 выдачей сигнала "Конец кодовой комбинации" с (и+!)-го разряда регистра.

Если в процессе сдвига "1", предварительно записанной в первый разIj ряд регистра 1, в послепнем происходит сбой, комбинация "!О" в (и+1)-м и (и+2)-м разрядах регистра появляется преждевременно и формирует ложный сигнал Конец кодовой комбинации . При этом генератор 3 продолжает вырабатывать тактовые импульсы, которые осуществляют сдвиг информации в регистре 1, "11 появляется в (n+2)-м разряде регистра 1 и формируется сигнал "Брак", который поступает на выход 6 и закрывает элемент

И 2,. запрещая прием информации с входа 4, 20

Формула изобретения

Устройство для преобразования последовательного кода в параллельный, содержащее элемент И, первый вход которого является информационным входом устройства, а выход соединен с информационным входом регистра сдвига и входом генератора тактовых импульсов, выход которого соединен с тактовым входом регистра сдвига, вход установки которого является стробирующим входом устройства, отличающееся тем, что, с целью повышения надежности устройства, в регистр сдвига введен дополнительный старший разряд, выход которого соединен с вторым входом элемента И и является выходом ошибки устройства.