Устройство для контроля многовыходных логических элементов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля многовыходных логических элементов, БИС и печатных плат с элементами. Целью изобретения является повышение производительности устройства. Устройство для контроля многовыходных логических элементов содержит генератор 1 тактовых импульсов, генератор 7 тестов, многоканальный сигнатурньш анализатор 9, блок 5 памяти эталонных сигнатур, блок 6 сравнения, коммутационные поля 4 и 10, элементы ИЛИ 12 и 14, счетчики 3 и 11, триггер 13, блок 15 индикации и блок 2 управления. 6 ил. с (О

СОЕЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (I9) «->11 <и (51)4 С 06 F 1/26

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ (21) 4016330/24-24 (22) 29.11.85 (46) 15,10.87. Бюл. N - 38 (71) Ленинградский электротехнический институт им. В.И.Ульянова (Ленина) (72) А.С.Календарев, В.П.Крюков, И.E.Íîâèêîâ, А.П.Смирнов и Л.А.Шумилов (53) 681.3 (088.8) (56) Авторское свидетельство СССР

Р 1016786, кл, G 06 F 11/26, 1981, Авторское свидетельство СССР

Ф 991430, кл, С 06 Г 11/26, 1980. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МНОГОВ61ХОЦНЫХ ЛОГИЧЕСКИХ ЗЛЕИЕНТОВ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля многовыходных логических элементов, БИС и печатных плат с элементами, Целью изобретения является повьппение производительности устройства. Устройство для контроля многовыходных логических элементов содержит генератор 1 тактовых импульсов, генератор 7 тестов, многоканальный сигнатурный анализатор

9, блок 5 памяти эталонных сигнатур, блок 6 сравнения, коммутационные поля

4 и 10, элементы ИЛИ 12 и 14, счетчики 3 и 11, триггер 13, блок 15 индикации и блок 2 управления. 6 ил, 1 3451

Изобретение относитс.я к ав ",îì;IòèE« и вычислительной технике и может быть использовано для контрстля многoEIbIxofl,"ных логических элементов и цифровых ч блоков.

Целью изобретения является повьппека ции, Ç0

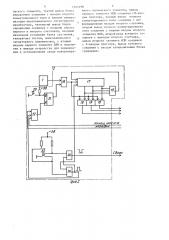

Блок 2 управ тения (фиг.?) содержит элемент И 16„ регистр 17 сдвига, 11ервый элемент ИЛИ-HE 18, группу элементов И 19, кнопку "Пуск" 20, триггер

21, второй элемент ИЛИ-НЕ 22, кнопку

"Сброс" 23, 24.1 и 24,2 — <.оотнетственно первый и второй элементы И-НЕ (образующие триггер).

Блок 6 сравнения (фиг.3) содержит схему 25 совпадения, D-триггер 26.

Второе коммутацттонное поле 10 (фиг.4) является многопозиционным переключателем, Второй счетчик 11 (фиг.5) содержит

Т-триггеры 27, элементы ИЛИ 28.

Первое коммутационное поле 4 (фиг,б) является многопозиционным переключателем на несколько направлений.

Устройство работает следующим образом.

Сигналом "Сброс" блока 2 управления, которьп вырабатывается при нажатии кнопки 23 "Сб<рос" и срабатывании триггера на элементах 24.1 и 24.2, устанавливается в начальное состояние первый счетчик 3, блок 6 сравнения„ генератор 7 тестов, контролируемый ние производительности контроля.

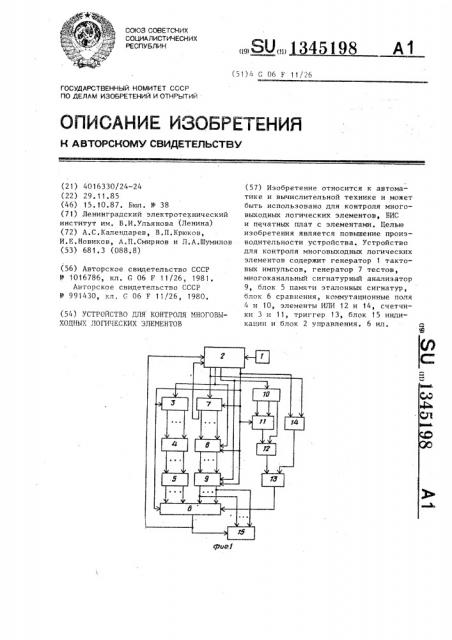

На фиг.1 приведена схема устройства для контроля многовыходных логических элементов; на фиг,2 — то же., блока управления; нл фиг.3 — то же,, блока сравнения; на фиг.4 — второе коммутационное поле; на фиг,5 — схема второго счетчика; на фиг.б — первое коммутационное поле.

Схема устройства для кочтроля многовыходных логических элементов (фиг.1) содержит генератор 1 тактовых импульсов, блок 2 управления, первьпт

20 счетчик 3, первое коммутационное поле

4, блок 5 памяти эталонных сигнатур, блок 6 сравнения, генератор 7 тестов, контролируемый логический элемент (КЛЭ) 8, многоканальный сигнатурньпт анализатор (MCA) 9, второе коммутационное поле 10, второй счетчик 11, второй элемент ИЛИ 12, RS "ð:èããåð 13, первый элемент ИЛИ 14, блок 15 индиI

98 7

11 О I И I С С К И и Э "1 Р М Р I i Т: ..„„ 111<1 ?? и терс 3 тсI< ме HT ИЛИ-H1 22 триггер 21. Нос<те этого схема Лото< а к началу рлб0111, Пртт нажатии тт этпусклнии кнопки

"Пуск" 20 триггер: 21 устанавливается

11 11 в 1, обеспечтсв".FI прохождентте тактовых импульс<о» с EI.-.IxojIл генератора че— реэ элемент И 16 „,.I c"инхровход реги-стра 17 сдвитя и первые входы элементов И 19. Если в начальный момент содержимое регистра ",7 сдвига 000 (после начальной устлновкк), то на выходе элемента ЖП1-НГ 18 появляется

II 11

1, которая .т а и и с ы в а е т с я в iJ p p B bIA разряд регистра 17 сдттттгя через сдвкговый вход по синхроимпульсу из ге:-:ерлторя 1, На pтором и последующих

1! II тактах 1 сд в и г а ет с я в регистре 1 7 сдвига д о е г о оч е р е д н о г о обнуления .

Т я ккм О б р я -.- ом, обеспечивается ф о рми р о в л н и е фя з Ф <П „ .« Ф . н а и е р в ом ,т ь втором и третьем pb;:

7 тестов по с.! I-FIafl< b< <, ГP:IåpFIðóåò тестовые наборы Ia «:-:оды контролируеМОГО лОГич<:ст 01 О элс .мс.нтя 8 которьпт синхро;и-.èpópòñE,. фазой ", Ф . должна быть задержат л отттссительно Ф, на время, необхсдимое для срабатывания контролируемого элемстта 8, а фаза

Ф,„ должна быть задержана относительно

Ф ня время, необходимое для ср баты-. г влния многокянальнсго скгнатурного анализатора 9„

По сигналам Ф pBtàòûâPñò cr eò÷èê

3, обеспечивая через коммутатор 4 Ieребор адресов блс:кя. 5 чяттятк. Пере— ключ енкя коммутат ог. я - об есле-Листают различный период перебора ядт есов блока 5. Ф:-1зой Ф. <е1 ез комм -адис н ное поле 10 11 элсметт ИЛИ 12 об: спечиваетсч cpàб :PbIPлнке "риггерл 13.

Ь этом слу.яс ср, вненке сигнл .-.р в блоке о срлвн=:ни, полученньв< KA олгт<= 5 ттл, "ятк, Ос уществт яе . ся па каждом л., ге с HIiõpoFIèçàFIèè Ф .. Одн я 1с 0 r! е р е к <1 ю ч е н и с! м к О и: 1 у т л I „ и О н н О Г О

1Iàflÿ 10 обесп=-чивлются FI !Iprrr.ие режимы работы блока 6 свяннения,. з этом случае период ср:-.внения задяе.:ся коэ<1т<Ъициентом " .лени <:чет така 11 „ко

40 з 134 1 тарый также через элемент %!И 12 обеспечивает срабатывание триггера 13 и блока 6 сравнения.

Сигнатура с выходов MCA 9 выдаетсся в блок 15 индикации, результат сравнения сигнатур также вьдается в блок 15.

Если на каком-то такте, например при контроле наиболее короткого кана- 10 ла КЛЭ 8, произошло несравнение сигнатур, то блок индикации высвечивает сигнал "Не годен", а блок 6 сравнения посредством элемента ИЛИ-HE 22 блока

2 управления останавливает процесс контроля.

Кроме того, контроль останавливается посредством элемента ИЛИ-kIE 22 при появлении "1" на последнем выходе генератора 7 тестов (например, в ста- 20 ршем разряде счетчика).

Елок 6 сравнения на фиг,3 обеспечивает сравнение эталонной сигнатуры из блока 5 памяти и МСА 9 посредством схемы 25 совпадения, а выдача сигнала 2 на выход блока 6 осуществляется по синхроимпульсам, поступающим на синхровход триггера 26, имеющего также вход "Сброс", управляемый сигналами

"Сброс" блока ? управления.

ЗО

Коммутационное поле 10 (фиг.4) содержит переключатель, обеспечивающий подключение фазы Ф к одному из своих выходов. В это время на остальные выходы 10 0000. Цепи каммута35 ции нулей не показаны.

Счетчик 11 (фиг.5) состоит из последовательно соединенных Т-триггеров

27 и элементов ИЛИ 28, вторые входы элементов HJIVi 28 и вход первого Ттриггера 27 используются для приема информации ат коммутатора 10. Счетчик 11 используется как делитель частоты, выходом его является выход последнего Т-триггера, Вход начальной установки счетчика 11 работает по сигналам "Сброс" блока 2 управления.

Коммутационное поле 4 (фиг.б) обеспечивает переключение выходов счетчика 3 и входов блока 5 памяти.

Таким образом, предложенное устройство обеспечивает увеличение производительности контроля за счет регулирования периода формирования эталонной сигнатуры и периода сравнения сигнатур посредством первого счетчика, первоГо коммутационного поля и блока памяти, а также второго коммутационного поля, второго счетчика, 98 первого и второго элементов ИЛ11, триггера и блока сравнения. Эти периоды подстраиваются пад наиболее короткие каналы контролируемой схемы и, если длины каналов отличаются в

2-3 раза, та возможна 2-3-кратное увеличение производительности контроля формула и з а б р е т е и и я

Устройство для контроля мнаговыхадных логических элементов, содержащее генератор тактовых импульсов, блок управления, первый счетчик, генератор тестов, блок памяти эталонных сигнатур, многоканальный сигнатурный анализатор и блок сравнения, причем выход генератора тактовых импульсов соединен с входом синхронизации блока управления, группа выходов генератора тестов образует выход устройства для подключения к информационному входу контролируемого логического элемента, группа информационных входов многоканальнага сигнатурнаго анализатора образует вход устройства для подключения к информационному выходу контралируемого логического элемента, выход блока памяти эталонных сигнатур соединен с первым инфармяцианным входам блока сравнения, выход мналоканальнага сигнатурнага анализатора соединен с вторым информационным входом блока сравнения и является информационным выходам устройства, а т л и ч а ю щ е е с я тем, чта, с целью повышения производительности контроля, устройство содержит первое и второе коммутационные поля, второй счетчик, два элемента ИЛИ и триггер, причем первый и второй входы астанова блока управления соединены соответственно с выходом блока сравнения и выходом конца теста генератора тестов, выход блока сравнения является выходом годности устройства группа выходов первого счетчика соединена с группой входов первого коммутационного поля, выход которого соединен с адресным входом блока памяти эталонных сигнатур, первый выход блока управления соединен с первым входом первого элемента ИЛИ и входом пуска генератора тестов, второй выход блока управления соединен са счетным входом первого счетчика и подключен к выходу устройства для подключения к входу синхронизации контролируемого логи5

13lg5 ческого элемента, третий выход блока управления соединен с входом второго коммутационного поля и входом синхронизации многоканапьного сигнатурного

5 анализатора, четвертый выход блока управления соединен с входами сброса первого и второго счетчиков, входами начальной установки блока cp;li Håíèÿ, генератора тестов, многоканального сигнатурного анализатора, с вторым входом первого элемента ИЛИ и подключен к выходу устройства для подключения к установочному входу контролиру198 емого логического элемента, выход первого эпемента ИЛИ соединен с R-входом триггера, первый выход второго коммутационного поля соединен с информационным входом второго счетчика, второй выход второго коммутационного поля соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго счетчика, выход второго элемента ИЛИ соединен с S — входом триггера, выход которого соединен с входом синхронизации блока сравнения.

134519S

Кс/ uI5

1345198

&кcv югера

Редактор M.Êåëåìåø

Заказ 4922/48 Тираж б70 Подписное

ВНИИПИ Государственного ком;.тета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауьгкая наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород., ул„ Проектная. 4

Аи люм аммтора

Составитель Д.Ванюхин

Техред Л.Сердюкова Корректор;I.Ìóñêà