Процессорный модуль однородной вычислительной структуры

Иллюстрации

Показать всеРеферат

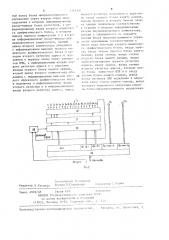

Изобретение относится к вычислительной технике и может быть использовано при разработке специализированных и универсальных вычислительных устройств, предназначенных для обработки цифровой информации. Целью . изобретения является повьшение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит арифметико-логический блок 1, блок 2 умножения, блок 3 деления, двунаправленный коммутатор 4, первый и второй блоки 5 и 6 памяти данных, блок 7 регистров, первьй и второй регистры 8 и 9, первый и второй индексные арифметические блоки 10 и 11, первый и второй регистры 12 и 13 адреса , блок 14 памяти команд, элемент ИЛИ 15, первый коммутатор 16, блок 17 микропрограммного управления, второй коммутатор 18. Увеличение быстродействия обеспечивается за счет сокращения числа последовательных обращений к памяти. 2 ил. (Л -огг

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 G 06 F 15/00

ГОСУДАРСТНЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3893634/24-24 (22) 05,05,85 (46) 15,10,87. Вюл, 1Ф 38 (71) Таганрогский радиотехническии институт им, В,Д.Калмыкова (72) В.Е.Золотовский, Р,B,Êîðîáêîâ, Л.Ф,Карпенко и А,К,Степанян (53) 681,32(088,8) (56) Авторское свидетельство СССР

У 438015, кл, G 06 F 15/00, 1973.

Авторское свидетельство СССР

Ф 608160, кл, G 06 F 15/00, 1976. (54) ПРОЦЕССОРНЫЙ ЭЛЕМЕНТ ОДНОРОДНОЙ

ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ (57) Изобретение относится к вычислительной технике и может быть использовано при разработке специализиро" ванных и универсальных вычислительных устройств, предназначенных для обраЛ0„ 1345207 А 1 ботки цифровой информации, Целью изобретения является повьппение быстродействия устройства ° Поставленная цель достигается тем, что устройство содержит арифметико-логический блок

1, блок 2 умножения, блок 3 деления, двунаправленный коммутатор 4, первый и второй блоки 5 и 6 памяти данных, блок 7 регистров, первый и второй регистры 8 и 9, первый и второй индексные арифметические блоки 10 и 11, первый и второй регистры 12 и 13 адреса, блок 14 памяти команд, элемент

ИЛИ 15, первый коммутатор 16, блок 17 микропрограммного управления, второй коммутатор 18 Увеличение быстродей" а ствия обеспечивается за счет сокращения числа последовательных обращений

С: к памяти, 2 ил, Изобретение OTiio. ванньгх и универсаль)пtx вычисi>è сль::,Гх устройств, предназнта< е(! !»ьгх д))я обр 3 ботки цифровой )и»фа)3маци-i, Цель изобретения - -;0!3»title Hс бы" стродействия уcTpGAclF>F(, На фиг, 1 пРеДставлена стР уч<тУ >El .и схема процессорного элемента; 1!а фиг, 2 — структурная <:хема б)л3ка уп равления процесс Орг(31 о элеме (.а, Процессорный эл с;(е нт Одна 3адной вычислитечьной стру.ктуры содержит арифметика-логический блок 1 блок 2 умножения, блок Э де.»ения, д вунаг) р", --ленный коммутатор -, 1(pp(31 Ii"-.. и л сарой блоки 5 H 6 памяти па (FIIIK,, 3 )ак 7 регистров, первый и второй -, гистрь:

8 и 9, первый и второй индах снь(с

1ариметические блоки 10 H 1) 1, »-ервьп - и второй регистры 12 -i 13 -;,ä ;ðåñà, блок 1г< памяти команд,. Эле:"(ент 1)П13!

15, первый комму га rc р 16, блок микропрограммного угtpa :J!PH л,, ВТОрай коммутатор 18, вход 1i9 адр -сс в устрой ства, вход 20 данных ;còpà (cTva,. Вхаii

21 программы устройств;.., пс:;:вык вх<>д

22, второй вход 23„ ;р --::ий -:õo! 2< режима уcTporrc Теа. Бпа; у.-:)>а)331".1: л

coдсржит регистр 2 ка iа (д(::, c(ñ: Т;НК

26, блок 27 постоянной памя"и,, )егистр 28 микрокоманд, генер; тор ? тактовых импульсов.

11pОцес сорньп1 элема нт раб(3 т с<е т < . I е дующим образом.

На первом этапе происходит з -и сь программы и данных coÎò;=, т; "Fp.. )IG В

ПаМЯтЬ КОМаНД И Памзть Даи «1-)Х с 1ЛЛ этого ком(утлтар - ; TtåpeKJIK-ь»с те л состояние Прием с !)(инь),. 11 (()с)))ма)(и".

С ПЕРВОЙ ШИНЫ Па Стт>>()aeÒ На ЛОК 3 а с ВтОрОИ шины — на блок 6 Г..гмл(и да)3" ных. Пpя этОм Ic()MN J" aTО() 1 ". !(aходi»Tc i

Б coстоянии ))к!3!Вч(з(3,. itr(1)o>)1!д (()(Я с

ii тт >

Входа 20 одновремеRHG посту -ает Iia первую и вторую )111«-(11 Г(а: ных, Синхаон"но с этим включает.-.н комму -;"op 18.

АдРес с входа 19 па<:ту.†.ает «а рег:— стры 12 и 13. Таки.; обр,.ç: î.ì,. . В .бт-..к=",::;

5 и 6 в одноименных адресах GK;iз»t;аются записанными оп):.Наковь)е (анны,:

После записи данных ка)л"ту: =; гор "6

ОТКЛН)Чав Т В 1!ó TpСННИ<> 11Hiil>i О т В Нсэtii . (=.! l

ПраисхОдит зепи с. ь I!i) .). paMI )ь В б:! О .

14 памяти команд „С .-. нап ia вх" г(е коммутатор". 8 с ахг„1))>(е t )(Ä .>г»ррс,:-, пОступают 13 с>()ок 1) l и l мл тl«к )м(3. -:;1!

iC,>Hi3M С Л

;< С -: (3 >3 (3 Е (Ва втор

) > .. i (0!3,, 1: сэ

HHCJ1C) (> е..-, и но< (I С>13 В ПР (! )

Гc! >,=? 7

> < P H ô1i С:

-ит» рс ° >1, е

C () >Г>ЛЬ! П, <Б т i) 1»Л(HT!F ЗГ с "»т ПРОЦЕССОР паки адресации адреса и опре.кк р<)прогparl)(лзг;;а G;",à адесa.,t ю. " аг а л и= —.o; åé! (:

»» .лтс!l т . Г1(1 пс ;; i!»лv <. Rõo,,а 2< ()д:!o;-;ðå".»P)гнл <. ад)л i- l!)! KOF!;31:ды с !

3K<3!(a 21 Ост".Лают - Вхо;(бпака

I!11 с»11 1 и К. > Iсс Нд . 10 С П Е 3 аl!ИСИ Про Грс>ММЫ.() «П ПОД >TO!3KH »а BC >Нас .:,,СЯ, ;)та1)О)! ЭТНГ) )3 »)Г. >Пн(яке Ilpo) и "м (ы, .0Н .»а:Jl:<:;ëe !ca .-. (Ослгдават-ель - .Ом

:-т;!»тыван)3!)» кс))мапд из блаха (- Г!амят13

«а:-:;..1)д и -»ь(псал)! анки tx . 1 .ðî!)е с с ар).ый

"! I С М(..t T 3 () >1 а,lа С т 1) О Г!1»Ь!» 1»с) ба рО> КО

С) 3;») <- - „((е< l В>)ле-,<я " cKe,, -и-, аж .и>, F. -,v c,"!t r„130!Tie-.-Иri =.-,. (..-! а на

3eJ .". (п) у ? При cnF>tli 13 с.тс рану .;-.i;.Л.пкх Олзрл",013 результат берется

" (.: р()! >:< разрядов -" пс рвал шина, 1р)1 < T()3H; "-.Г)е»»а ;:e 3 3epeTc>> (. ь(лапшг»х ра.»рядoa — вторая шина (в у »ас. 11 -- чксг о разрядов, на ес,б)<>Г»к). СГ(),кьу ° ь числО, Ом — попал ение числа разкст(;рае нсобхадимо сдвкнуть l(> !>lн (>I Pa aPЯДНОИ C PTKH T . Е ходимо ci i!.íóòü на 5 разря-. о, тс !.=",, а если влево, ти (ес.<ие и логическиe операств(плютc>! . блоках»-<. Ko"

<а)»дь» II(:pecüL,G к асущестьляк)тся с па >!;,iI>>t) блока регистров и индексных

>и((>метl .";e OK!»x алакай 1 0 и 1 . Гсаман.:ере::одаг, и операции:- ад адресам-.->ь!Г(слня!)Тся с СT!GJl »зава:-(ием индексньгх

-.-«рк(()ь»етtolecKHK )-,:toKOВ : 0 и 11.

0Iiep;1;,кя Вы:- алия тся следующим оо13 а 3 а М, Кома:-»,.ta и= б-:;к» памяти команд пас:тупает В б:I K у).равления E регистр

25 ксма«ды„КОЛ операции и признаки

j ecaп-;и "-:: . ТуIlа г:- на вход счет-(кка

2 .. как laча,(-.:-:; ь;й адрес микропрограммы

3 lПО т)НЛ Е iай О:!ЕР31(ИИ . СИНХРОНИЗИP у 1<3

))3- е имп у:-.I>cы с гане ра TG<3à 2.9 посту-!

:Ю На С с(ЕТ)!Ы)1:. ХОГ«СЧЕТЧИК а, Са>ДЕР нимле к.зтора) с: и >с -упает н i пастоян))с,е ваго)у!Ина < ще-; ";строй-.твс: 27 как (3;(РЕС, а,тЕР; ПМО . ЛЧЕйКК ЗВГ(КСЫВаЕтСЯ

Н рЕ ГИС т;> 2 8 I "H "«pel(амя НП т)ЫХОДЫ КО сс-poão,;,cрмк; >уст С-.о-.ветствуюг(ие си""Код 01!Cраlси i- —..i. э

-) 3СЯ" В Е >1 л

a(!J IC>3;->(i, . У:.ВИ,, к(:;ia;« "»,—,);,;Jt-1 (>Ос. упа>, т В (::локк

И 1 031.:О. Г р! Риlтi> ПЕГ(1<31 Я И 9

1345207 сбрасываются в начальное состояние

00 ... 00 и 000 ... 00 подачей сигналов 8, и 9,, Нулевой регистр системньп» и используется для хранения базы, 5

Во втором такте подачей сигналов

7, H 7 регистра (база) передается в блоки

10 и 11, где складывается со смещениями. 10

В третьем -,àêòå сформированные адреса поступают в регистры 12 и 13 и записываются туда па сигналам 12, и 13„, Одновременно па сигналу 14„ происходит увеличение адреса на едини?ЕУ о

В четвертом такте включается коммутатор 4, подаются сигналы 5„ и б

1 и сигнал приема на один из операционных узлов. Считывание из памяти дан20 ных операнды заносятся в регистры

„операционного узла, Запуск операции производится па заднему фронту сигнала приема данньгх.

В пятом так-е адрес из регистра 2В

13 переписьгвается в регистр 12.

В шестом такте результат из апера— ционного узла записывается в память данных, причем коммутатор настраивается так, что одна из шин, первая дб или вторая, подключается одновременна к входам блоков 5 и б. Подачей сигналов 5, и 6. результат по адре-у А2 записывается как в блок 5, так и в блок 6. Одновременно с записью результата счить»вается новая команда и записывается в регистр команды блока

i7 микропрограммного управления.

Таким образом, предлагаемое устройство позволяет совместить выборку команды и запись результата. Работа аналогична, если выборка происходит из регистров или из регистра и памяти, или регистра памяти и одного из устройств, т.е. если один операнд бе- 4 рется из ячейки регистровой или общей памяти, а второй, как результат выполнения предьЕ»Еущей операции, из регистра операционного узла.

5О формула изобретения

Процессорный моцуль однородной вычислительной структуры, содержащий блок умножения, блок деления, арифме55 тико-логический блок, блок регистров, два регистра, первый индексный арифметический блок, двунаправленный коммутатор, блок микропрограммного управлепил, первьп»»»нфармационный входвыхад арифметика — логического блока через первую общую шину подключен к первым информационным входам-вьгходам блоков умножения и деления, второй информационньп» вход-выход арифметикологического блока через вторую общую шину подключен к вторым информационным входам-выходам блоков умножения и деления, выходы первого и второго регистров подключены соответственно к первому и второму информационным входам блока регистров, информационный выход первого индексного арифметического блока подключен к информационному входу первого регистра, выходы с первого по десятый блока микропрограммного управления подключены соответственно к входу кода операции арифметика-логического блока и синхровходу блока умножения, к синхровходу блока деления, к первому и второму управляющим входам двунаправленного коммутатора, к входу кода операции первого индексного арифметического блока, к входу записи-считывания первого регистра, к входу записи-считывания второго регистра, к первому управляющему и к второму управляющему входам блока регистров, о т л и ч а— ю шийся тем, что, с целью повышения быстродействия, он дополнительно содержит второй индексный арифметический блок, два коммутатора, блок памяти команд, два блока памяти данных. два регистра адреса, блок элементов ИЛИ, первый, второй и третий входы задания режима модуля подключены соответственно к управляющему вхоЪ ду первого коммутатора, к управляющему входу второго коммутатора и к входу записи блока памяти команд, вход задания программы модуля подключен к информационному входу блока памяти команд, вход адреса модуля подключен к информационному входу второ— о коммутатора, информационный вход модуля подключен к информационному входу первого коммутатора, одиннадцатый вь»ход блока микропрограммного управления через первую общую шину подключен к первому информационному входу-выходу блока регистров, к информационному входу первого индексного арифметического блока, к первому выходу первого коммутатора и к первому информационному входу-выходу двунаправленного коммутатора, двенадца1 34 : g!) i! ф,:ф

" о :ада Д» !Я". f„

Составитель P.С !ирнзв

Редактор И.Касарда Техред П.Сердюкова! орректор .. ерн

Заказ 4922!48 Тираж б70 (од" и! ое

ВНИЛГЯ Государственно-. u .",Oмн тета C,",СР по делам изсбретекий и огкрытий

113035, Москва, Е-35,, Рау:!1ская !аб... и. - /5

Производственно-полиграфическое п;;.:eëïi:i:.". iòè! .„., Ужгород ул, П вЂ,.оектная, 4 тый выход блока микропрс грамм.:ого управления через вторую общую пину подключен к второму информапионному входу-выходу блока регистров, к информационному входу второго индексного арифметического блока, к второму выходу первого коммутатора и к второму информационному входу-вьг<оцу двунаправленного коммутатора, первый выход второго коммутатора объединен с информационным выходом пе!рвого индексного арифметического блок:а и выходом второго регистра адреса и подключен к первому входу блока элемен-. тов ИЛИ, к информационным входам пер. вого регистра адреса и к адресным входам первого блока памяти данных,, второй выход второго коммутатора об!единен с информационным выхопом вто-. 2 рого индексного арифыетическ;сго блска и подключен к информационному входу второго регистра и к информационному входу второго регистра адреса, выход первого регистра. подключен к адресному входу зторого блока памят данных, выходы первого и второго блоков памяти данных подключены соответственно к первому и второму информационным входам двунаправленного коммутатора

9 выходы с тринадцатогс по двадцать первый блока микропрс граммного управ-б ле:- ия подключены соответственно к входу кода операции второго индексного арифметического бг:ока., входу записи, входу чтения первого блока памяти даь!ных, входу записи, входу чтения вЂ,òîð0ã0 блока памяти данных,. входу запуск-считывания первого регистра адреса, входу записи, входу чтения второго регистра адреса, второму входу (370KB, злементов ИЛИ и х входу б чтения блока памяти команд, выход блока злемента ЧПК подключен к адрес-. ному входу блока гамяти команд, выход которого лодк !юченк входукода команды блскамикропрограммного управления.