Устройство для вывода графической информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в системах автоматизации процессов обучения, при создании операторских и диспетчерских пультов // 73 автоматизированных систем управления , в информационных и справочных графических системах, в качестве выходного уст ройства универсальных и специализированных ЭВМ. Целью изобретения является повышение быстродействия и упрощение устройства. Устройство содержит блок памяти 1, первый 2 и второй 9 дешифраторы, модуляционный блок 3, распределитель импульсов 4, синхронизатор 5, коммутатор адреса 6, телевизионный индикатор 7, регистр 8. Устройство позволяет выполнять в 2 раза меньше команд для выдачи точек из ЭВМ, что соответствует повышению в 2 раза .эффективной производительности ЭВМ. 1 ил. с (Л со f СП ГчЭ 4 О А Хд

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51)4 С 09 С 1 08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Ю

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

RO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 3967375/24-24 (22) 17, 10 ° 85 (46) 15. 10.87, Бюл. N- 38 (71) Московский инженерно-физический институт (72) О.Н.Цапко (53) 681,327 (088.8) (56) Авторское свидетельство СССР

Х - 930355, кл. G 09 G 1/08, !977. (54) УСТРОЙСТВО ДЛЯ ВЫВОДА ГРАФИЧЕСКОЙ ИНФОРМАЦИИ (57) Изобретение относится к области вычислительной техники и может быть использовано в системах автоматиза— ции процессов обучения, при создании операторских и диспетчерских пультов

80 1345240 А 1 автоматизированных систем управления, в информационных и справочных графических системах, в качестве выходного устройства универсальных и специализированных 3ВМ. Целью изобретения является повышение быстродействия и упрощение устройства. Устройство содержит блок памяти 1, первый

2 и второй 9 дешифраторы, модуляционный блок 3, распределитель импульсов 4, синхронизатор 5, коммутатор адреса 6, телевизионный индикатор

7, регистр 8, Устройство позволяет выполнять в 2 раза меньше команд для выдачи точек иэ ЭВМ, что соответствует повышению в 2 раза,эффективной производительности 3BM ил °

1345240

Изобретение относится к вычислительной технике и предназначено для вывода информации из ЭВМ, может использоваться в системах автоматизации проектирования и конструирования, при автоматизированной обработке данных, в диалоговых системах.

Цель изобретения — повышение быстродействия и упрощение устройства.

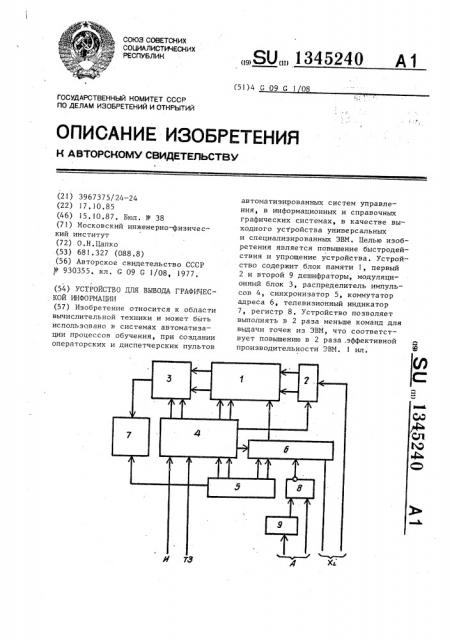

На чертеже представлена блок-схе— ма устройства.

Устройство содержит блок памяти

1, первый дешифратор 2, модуляционный блок 3, распределитель импульсов 4, блок синхронизации 5, коммутатор адреса 6, телевизионный индикатор 7, регистр 8, второй дешифратор 9, Устройство работает следующим образом, Блок синхронизации 5 вырабатывает импульсы, соответствующие требуемой дискретизации экрана телевизионного индикатора 7 и управляет раз— верткой последнего. Эти импульсы поступают на распределитель импульсов 4, осуществляя его временную привязку к телевизионному синхросигналу, В блоке памяти 1 каждой точке изображения соответствует один бит, кодирующий ее яркость. Информационная емкость экрана составляет 2 тоб чек по горизонтали на 2 точек по

m вертикали. Начало координат коорди— натной сетки экрана находится в нижнем левом углу. При этом, математические координаты (Х, Y) точек экрана лежат н пределах: О (Х (2" — 1, О Y 2 -1, Разрядность слова блока памяти 1 составляет ? бит„

В режиме считывания информации из блока памяти 1, преобразования ее в видеосигнал 4 и отображения на экране телевизионного индикатора 7 устройство работает идентично известному устройству °

Запись информации в блок памяти

1 из ЭВМ производится следующим образом.

В адресном поле ЭВМ для работы с устройством отводится 2 адресов, М по которым производит я обращение к устройству. Например, для ЭВМ типа

". Электроника-60" с каналом "Общая шина", при m=8 обращение к устройству может осуществляться по адресам

177400 9 — 1777779 куба памяти, вы .)

55 деленного для подключения внешних устройств, В этом случае к устройству относятся младшие восемь разрядов адреса, а старшие восемь разрядов определяют зону, где находятся эти адреса. Каждый адрес обращения соответствует строке изображения, хранящегося в блоке памяти 1.

На первые входы регистра 8 подают— ся m младших разрядов адреса, а на входы дешифратора 9 подаются старшие разряды адреса из ЭВМ, На вход дешифратора 2 подаются р младших, а на первый вход коммутатора адреса 6 старшие информационные разряды из

ЭВМ.

При записи информации в блок памяти 1 из ЭВМ на входы дешифратора

9 подается адрес зоны адресов обра— щения, а на первый вход регистра 8 адрес обращения, соответствующий строке изображения„ в которую производится запись, Адрес обращения записывается в регистре 8 сигналом с выхода дешифратора 9. По информационным шинам из ЭВМ выдается значение

Х координаты записываемой точки,причем младшие р разрядов поступают на вход дешифратора 2. На первый вход распределителя импульсов 4 подается значение информационного бита ("О" или "1"), кодирующего яркость точки и по сигналу "Требование записи", поступающему на второй вход распределителя импульсов„ производится подключение ацреса записи через коммутатор адреса 6 к блоку памяти 1 и запись в бит выбранного слова,опре— деляемый дешифратором 2.

Таким образом, запись точки про- изводится за один машинный цикл выдачи, за счет того, что координата

Y точки задается в ацресном поле, а координата Х точки — в информационном. При разрядности канала ЭВМ,равном 16 бит, что соответствует таким мини- и микро вЂ Э как СМ-3, СМ вЂ” 4, Электроника †и др., экономится время выполнения по крайней мере одной команды выдачи в расчете на одну точку. Так, при перегенерации на экране всех точек, при времени команды выдачи, равном 7 мкс, и при п =

= m=8 выигрыш в быстродействии по сравнению с известным устройством составляет 448 мс (в 2 раза). При этом, для выдачи точек из ЭВМ требуется выполнить в 2 раза меньше ко! 345240

Составитель О..Кулаков

Техред A.Êðàâ÷óê

Корректор А Зимокосов

Редактор И, Сегляник.

Заказ 4925/50

Тираж 432 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий !!3035, Москва, Ж-35, Раушская наб., д..4/5

Производственно-полиграфическое предприятие, г,ужгород, ул.Проектная, 4 манд выдачи, что соответственно в

2 раза повышает его эффективную про— изводительность. Кроме этого, в предлагаемом изобретении достигается су5 щественное сокращение объема оборудования, так как из известного устройства исключаются третий регистр, второй регистр, первый и второй сумматоры, узел сравнения, счетчик,триг- 10 гер и вентиль.

Формула изобретения

Устройство для вывода графической 15 информации, содержащее блок памяти, первый дешифратор, модуляционный блок, распределитель импульсов, блок синхронизации, коммутатор адреса и телевизионный индикатор, тактовый 20 вход которого соединен с первым выходом блока синхронизации, первая группа выходов которого подключена к входам группы распределителя импульсов, выходы первой группы которого соединены с тактовыми входами модуляционного блока, выход которого подключен к информационному входу телевизионного индикатора, информацион— ные входы модуляционного блока соеди- 30 иены с выходами блока памяти, входы обращения которого подключены к вы— ходам второй группы распределителя импульсов, первый выход которого подключен к управляющему входу первого дешифратора, выходы которого подключены к инфбрмационным входам блока памяти, адресный вход которого соеди- нен с выходом коммутатора адреса, управляющие входы которого соединены с вторым выходом распределителя импульсов и выходами второй группы блока синхронизации, первый и второй входы распределителя импульсов являются соответственно входом задания яркости и входом разрешения записи устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и упрощения устройства, в него введены регистр и второй дешифратор, причем выход регистра соединен с первым информационным входом коммутатора адреса, второй информационный вход которого является информационными входами старших разрядов устройства, информационный, вход первого дешифратора является информационными входами младших разрядов устройства, адресными входами младших разрядов которого является информационный вход регистра, вход разрешения записи которого соединен с выходом второго дешифратора, вход которого является адресными входа— ми старших разрядов устройства.