Регистр с контролем и коррекцией

Иллюстрации

Показать всеРеферат

Изобретение относится к электронной цифровой технике и может быть использовано при разработке новых интегральных микросхем среднего уровня интеграции. Цель изобретения - повьшение надежности устройства. Поставленная цель осуществляется за счет того, что сигнал коррекции подается на установочные входы всех триггеров . В любой неалгоритмической комбинации обнаруживаемая пачка 1 или О в результате сдвига рано или поздно попадет в пределы контролируемых разрядов, что приведет к установке в регистре алгоритмической комбинации 000....О. Устройство содержит D-триггеры, сумматоры по модулю два, элемент ИЛИ, элемент И. 1 ил. со СП tsj сг о

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1345260

А1 (51) 4 G 11 С 19/00 G 06 F 11/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCH0MY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР пО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4078050/24-24 (22) 21.04.86 (46) 15.10.87. Бюл. Ф 38 (72) А.М.Сидоров и Ю.А.Носов (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

N - 1076950, кл. С 11 С 19/00, 1977.

Ланцов А.А. и др. Цифровые устройства на комплементарных МДП интег-. ральных микросхемах. M.: Радио и связь, 1983, с. 57, рис. 2.28. (54) РЕГИСТР С КОНТРОЛЕМ И КОРРЕКЦИЕЙ (57) Изобретение относится к электронной цифровой технике и может быть использовано при разработке новых интегральных микросхем среднего уровня интеграции. Цель изобретения— повышение надежности устройства. Поставленная цель осуществляется за счет того, что сигнал коррекции подается на установочные входы всех триггеров. В любой неалгоритмической комбинации обнаруживаемая "пачка 1 или 0" в результате сдвига рано или поздно попадет в пределы контролируемых разрядов, что приведет к установке в регистре алгоритмической комбинации 000....0. Устройство содержит

D-триггеры, сумматоры по модулю два, элемент ИЛИ, элемент И. 1 ил.

1 134526

Изобретение относится к электронной цифровой технике и может быть использовано при разработке новых интегральных микросхем среднего уровс, ня интеграции.

Цель изобретения — повышение надежности устройства.

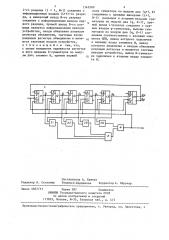

На чертеже представлен регистр с контролем и коррекцией.

Устройство содержит D-триггеры

1-1.N, сумматоры 2-2п по модулю два, элемент ИЛИ 3, элемент И 4.

Устройство работает следующим образом.

В качестве примера используется

10-разрядный сдвигающий регистр на триггерах К 155 TM 2.

Если все N триггеров установить в состояние "0", то при подаче такто- 0 вых импульсов (ТИ) в регистре будут последовательно появляться 20 состояний и при правильной работе они будут повторяться.

В регистре возможны 2 о =- 1024 сос- 25 тояний, и если в результате сбоя он перейдет в одно из 1004 неалгоритмических состояний, то самостоятельно в,алгоритмическое состояние он не войдет . 30

Алгоритмические состояния следующие: во всех разрядах О; во всех разрядах 1; остальные 18 состояний представляют собой две пачки — одна из единиц, другая из нулей, причем

35 длина пачки может бь1ть от 1 до 9 и в сумме они всегда составляют 10.

Таким образом, между разрядами существует не более одного перехода из

1 в О либо из О в 1. Любая из 1004-х неалгоритмических комбинаций содержит

3 или больше пачек и поэтому будет 2 или больше переходов из 1 в О, либо из О в 1, между соседними разрядами.

Равнозначность или неравнозначность состояний двух соседних триггеров после очередного сдвига легко определяется с помощью двухвходового сумматора по модулю 2.

В 10-разрядном регистре необходи50 мо контролировать 5 разрядов.

На входы сумматора 2.1 подаются выходные сигналы Q и Q,, на входы

1 сумматора 2.2 — выходные сигналы Q и Q, на входы сумматора 2.3 — выход 3 э 55 ные сигналы Q > и Q и на входы сумматора 2 ° 4 — выходные сигналы Q и

Если в регистре неалгоритмическая комбинация, т.е. если существуют, например, две пары соседних разрядов с неравнозначными состояниями, то в результате сдвига эти две пары обязательно попадут в пределы контролируемых разрядов Т, — Т .

Когда триггеры Т и Т> примут неравнозначные состояния (01 или 10), на выходе сумматора 2.4 появится 1.

Но от другой пары разрядов с неравнозначными состояниями появится 1 и на выходе сумматора 2.1,или 2.2, или

2.3.

Следовательно, на выходе элемента

3 будет 1, а на выходе элемента 4 появится корректирующий сигнал О.

Этот сигнал, поступая на установочные входы R всех 10-ти триггеров, установит их в О, т.е. в регистре будет алгоритмическая комбинация ° В этом и состоит коррекция.

Корректирующий сигнал будет иметь форму отрицательного импульса, длительность которого определяется временной задержкой срабатывания триггера по входу R, а также задержкой в схеме контроля и коррекции.

Очевидно, что при всех алгоритмических комбинациях сигнал 1 может появиться одновременно только на выходе одного сумматора, поэтому на выходе элемента 4 (на входах R всех триггеров) удерживается потенциальный сигнал "1", который на триггеры не воздейСтвует, ибо входы S u R у этих

I триггеров инверсные.

В отличие от известного в предлагаемом устройстве регистр может иметь любую длину. От этого зависит только число сумматоров в схеме контроля и коррекции и, следовательно, число входов логического элемента 3.

Достоинством предлагаемой схемы является и то, что количество корректирующих импульсов в заданное время, которое показывает интенсивность сбоев, можно подсчитать, например, с помощью особого счетчика. По зт ой величине можно судить о приближении аппаратуры к состоянию отказа или о появлении мощной внешней помехи и т.д.

Формула из обретения

Регистр с контролем и коррекцией, содержащий N разрядов (N> 2), каждый из которых выполнен на двухступенчатом D-триггере, элемент ИЛИ, выход

Составитель А. Ершова

Редактор И. Сегляник Техред Л.Сердюкова Корректор А. Обручар

Заказ 4927/51

Тираж 587 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 13452

i-го разряда (i = 1., N-1) соединен с информационным входом (i+1)-го разряда, а инверсный выход N-го разряда соединен с информационным входом пер5 вого разряда, прямой выход N-ro разряда является информационным выходом устройства, входы обнуления разрядов регистра объединены, тактовые входы разрядов регистра объединены и являются тактовым входом устройства, отличающийся тем, что, с целью повышения надежности регистра в него введены К-сумматоров по модулю два, элемент И, причем первый

60 4 вход сумматора по модулю два (q+1, K) соединены с прямыми выходами (i+1

N-I) разрядов и вторыми входами сумматоров по модулю два (q, К-1), прямой выход i-разряда соединен с первым входом q-сумматора, выходы сумматоров по модулю два (q, К-1} соединены соответственно с входами элемента ИЛИ, выход которого подключен к первому входу элемента И, выход которого подключен к входам обнуления разрядов регистра и является счетным выходом устройства, выход К-сумматора подключен к второму входу элемента И.