Устройство для синхронизации системы управления @ -фазного вентильного преобразователя

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ -;-,:

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4092072/24-07 (22) 20.06.86 (46) 23.10.87. Бюл. М 39 (71) Научно-исследовательский электротехнический институт Производств венного объединения„ХЭМЗ (72) Л.Е.Бахнов, Г.Г.Жемеров, И.Л.Коляндр, И.И.Левитан, Н.Э.Ле,итус и Е.Б.Петрик (53) 621.316,727(088.8) (56) Авторское свидетельство СССР

М 989741, кл. Н 02 М 1/08, 1981.

Авторское свидетельство СССР

М 904194, кл. Н 02 М 5/257, 1980.

Авторское свидетельство СССР

М 425296, кл. Н 02 М 7/00, 1969. (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ

CHCTEMbI УПРАВЛЕНИЯ ш-ФАЗНОГО i;HTHJIbНОГО ПРЕОБРАЗОВАТЕЛЯ.„ЯО„, 1347128 А1 (51)4 Н 02 М 1/08

° (57) Изобретение относится к элект- ротехнике и может быть илспользовано в цифровых системах управления вентильными преобразователями. Целью изобретения является повышение точности синхронизации за счет компенсации внутренних задержек узлов схемы.

Введение связей выхода запоминающего регистра 2 с вторым входом сумматора

3, выхода последнего с входом запоминающего регистра 2 позволяет корректировать число, соответствующее

Tñ временному интервалу t -= - --- -, где ш

T — период сети, а ш — пульсность преобразователя, на величину, равную асимметрии выходных импульсов aТ, устремляя последнюю к минимально возможному значению sa счет компенсации влияния внутренних задержек устройства. 2 ил.

1347128

55

Изобретение относится к электротехнике и может быть использовано в цифровых системах управления вентильными преобразователями.

Целью изобретения является повышение точности синхронизации за счет компенсации внутренних задержек узлов схемы.

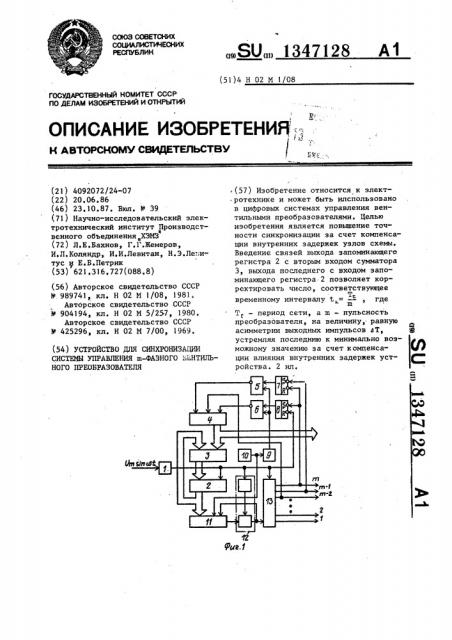

На фиг. 1 приведена функциональная схема устройства; на фиг. 2— временные диаграммы.

Устройство для синхронизации системы управления m-фазного вентильного преобразователя содержит формирователь 1 импульсов, следующих с периодом сети, выход которого подключен к входу записи запоминающего регистра 2, вход которого подключен к информационному выходу а выход—

Э

20 к первому входу сумматора 3, второй вход которого подключен к выходу первого счетчика 4, вычитающий вход которого подключен к выходу первого 5, а суммирующий вход — к выходу второ25 го 6 элементов И-НЕ, первые входы которых подключены к выходам первого

7 и второго 8 RS-триггеров соответственно, а вторые — к выходу делителя

9 частоты, вход которого подключен к выходу генератора 10 тактовых им30 пульсов вместе с вычитающим входом второго счетчика ll информационный вход которого подключен к выходу регистра 2, а вход записи — к выходу узла 12 сдвига импульсов, первый вход которого подключен к выходу счетчика 11, а второй — к выходу формирователя 1 вместе с R-входом второго триггера 8 и входом установки распределителя 13, вход которого под- 40 ключен к выходу узла 12, (m--2)-й выход — к входу установки счетчика

4, (m-1)-й выход — S-входу триггера

7, а m-й выход — к R-входу триггера

7 и S-входу триггера 8. 45

Формирователь 1 импульсов выполняет функцию нуль-органа с укорачиванием длительности импульсов и представляет собой, например, компаратор и одновибратор на Э-триггере (не по- 50 казаны), причем входом формирователя является инверсный вход компаратора, а выхоцом - выход одновибратора, соединенного входом с выходом компа." ратора.

Узел 12 сдвига импульсов может быть выполнен, например, на двухвходовом элементе ИЛИ, к входам которого подключены выходы элементов задержки на такт, реализованные каждый на

D-триггере с входами асинхронной установки (не показаны), которые являются входами узла 12, выходом которого является выход элемента ИЛИ.

Распределитель 13 импульсов реализован, например, на последовательно соединенных счетчике и дешифраторе (не показаны), причем входом установки распределителя 13 является вход установки счетчика, входом распределителя — счетный вход счетчика, а выходами распределителя — выходы дешифратора, соединенного входами с выходами счетчика.

Принцип работы устройства поясняется диаграммами на фиг, 2, на которой обозначены: Б, — напряжение одной из фаз сети, например фазы А;

U, — выходные импульсы формирователя

1 импульсов; U — выходные импульсы

10 генератора тактовых импульсов; U,— диаграмма состояний выхода счетчика

ll ; U — импульсы на выходе узла 12 сдвига импульсов; U выходные импульсы первого RS-триггера 7; U< — выходные импульсы первого элемента И-НЕ !1; U — диаграмма сосф таяний выхода первого счетчика 4 импульсов; U — выходные импульсы второго триггера 8; .U< — выходные импульсы второго элемента И-HE 6.

Устройство для синхронизации системы управления m-фазного вентильного преобразователя работает следующим образом.

На вход формирователя 1 импульсов поступает отфильтрованное напряжение одной из фаз сети, например фазы

А, Ы моменты начала формирования положительной полуволны напряжения на выходе формирователя 1 импульсов появляются импульсы U следующие с

1 периодом У. сети, При этом длитель1 ность импульсов U, равна периоду Т импульсов Ut, генератора 10 тактовых импульсов. В начале i-ão периода Т. .! сети импульс U, поступает на второй вход узла 1 2, где о суще ствля ет ся з адержка на период У . С выхода узла

12 импульс, задержанныи на такт, поступает на вход распределителя 13 импульсов на период Т „ Импульсом с выхода формирователя 1 импульсов распределитель 13 импульсов устанавливается в исходное состояние, поэтому первый импульс U» поступающий на вход распределителя 13 импульсов,, проходит на его первый вы1347128

t ra

m.Т, 20

25 (4) 3T=crl ш.T,=t -1 (6) ЕЕ,=Б;, +/1.

55 с

m.Т г ход. Одновременно с этим срезом импульса U во второй счетчик 11 импульсов записывается число N;„ с выхода запоминающего регистра 2, полученное на предыдущем периоде Т;„ сети, равном

1.„=N ..m.T ° (1)

Импульсы U„- с выхода генератора

10 тактовых импульсов поступают на вычитающий вход второго счетчика 11 импульсов, уменьшая число N. íà его выходе (фиг ° 2, U„). 1Ери равенстве нулю выходного кода второго счетчика

11 импульсов íà его выходе заема появляется импульс, поступающий на первый вход узла 12 импульсов. Второй импульс U поступает на второй

11 выход распределителя 13 импульсов.

Одновременно срезом этого импульса

U осуществляется перезапись числа

N. с выхода запоминающего регистра

i-1

2 во второй счетчик 11. Сформированный временной интервал 1 равен интервалу дискретности преобразователя

Ь„=И; . T,= =— - (2) Процесс циклически повторяется.

Фронтом импульса с (m-2)-го выхода распределителя 13 импульсов первый счетчик 4 импульсов обнуляется. Фронтом с (m-1)-го выхода распределителя 13 импульсов на выходе первого

RS-триггера 7 устанавливается логи- З5 ческая единица, определяя начало временного интервала t

На вход делителя 9 частоты импульсов с коэффициентом деления m поступают импульсы U« с выхода гене-, 40 ратора 10 тактовых импульсов. С выхода делителя 9 частоты импульсы с периодом ш Т подаются на вторые входы элементов И-НЕ 5 и 6. Импульс U c выхода первого RS-триггера 7 поступа- 45 ет на первый вход первого элемента

И-НЕ 5, разрешая прохождение импульсов U с периодом m.T на вычитающий вход йервого счетчика 4 импульсов.

На его выходе U формируется отрица- 50 тельное число, представленное в дополнительном коде. К концу временного интервала t,число на выходе первого счетчика 4 импульсов равно

Фронтом импульса с m-ro выхода распределителя 13 импульсов первый

RS-триггер 7 обнуляется, а второй

RS-триггер 8 формирует на своем выходе импульс ЕЕ, поступающий на первый вход второго элемента И-НЕ 6.

Таким образом, заканчивается временной интервал t„, и начинается временной интервал t„.

При этом импульсы с периодом

m T с выхода второго элемента И-НЕ

6 поступают на суммирующий вход первого счетчика 4 импульсов. В течение временного интервала С на вход первого счетчика 2 импульсов поступает число импульсов, равное

Таким образом, к концу временного интервала t на выходе первого счетчика 4 (фиг. 2, U ).èìïóëüñoâ сформируется число, равное алгебраической сумме чисел, соответствующих временным интервалам t m, и 1„,. г1=1 -1,= - — -(т -,). (3) .Г с учетом того, что t „=t „+a T.

Отсюда

Фронтом импульса ЕЕ, с выхода формирователя 1 импульсов, следующих с периодом сети, второй триггер 8 обнуляется, при этом импульсы ЕЕ прекращают поступать на суммирующий вход первого счетчика 4 импульсов.

Ha i-м периоде сети справедливо выражение, аналогичное выражению (1) T,-=N„.m -T,.

Учитывая выражение (4) и равенство временных интервалов t =t „„„, имеем (N,.-й,,) -Т - 1. (5)

Скорректированный код периода сети равен

На первый вход сумматора 3 поступает число Ю с выхода первого счетчика 4 импульсов, а на второй вход— число ЕЕ;»„ с выхода запоминающего регистра 2. Операция суммирования осуществляется с учетом знака числа col, Скорректированное число N, записы1 вается с выхода сумматора 3 в запоминающий регистр 2 срезом импульса U с выхода формирователя 1 импульсов, 1347128 чем исключается запись переходных процессов с выхода первого счетчика

4 импульсов. Запись числа N, с выхода запоминающего регистра 2 во второй счетчик 1 импульсов осуществля" ется срезом импульса U, отстающего

f2э на период Т, от импульса U, . .Этим обеспечивается запись достоверной информации. При этом в счетчик 11 импульсов записываются (n-1) младших разрядов кода N;, à и-й разряд является знаковым. Сумматор 3 и запоминающий регистр 2 имеют разрядность, равную и. Счетчик 4 импульсов также выполняется п-разрядным, что необходимо в начале работы устройства для записи числа и в запоминающий регистр 2 и далее.

Возможны 3 случая.

Число 2=0. При этом период сети не изменяется и корректировка кода

N, не производится.

Число 42 D. Период напряжения сети Т;> l;, и скорректированное число N равно N;=N;„+d2 (фиг. 2) . В блок фазосмещения системы управления

m -фазíîro преобразователя (не показан) поступают импульсы с m выходов распределителя 13 импульсов, а импульсы с (ш+1) выхода не используются.

Число d2 < 0. Период сети Т; меньше предыдущего и корректировка числа N,. „ осуществляется в сторону уменьшения. N;=И „-сд..

Таким образом, в предлагаемом устройстве синхронизации отслеживается изменение периода питающей сети с учетом внутренних задержек, что повышает точность синхрониза— ции.

Формула изобретения

Устройство для синхронизации системы управления m-фазного вентильного преобразователя, содержащее формирователь импульсов, следующих с периодом сети, выход которого подключен к входу записи запоминающего регистра, выход которого подключен к одному входу сумматора, первый и второй счетчики импульсов, генератор тактовых импульсов, выход которого подключен к входу делителя частоты и вычитающему входу второго счетчика импульсов, вход записи которого соединен с выходом узла сдвига импульсов, о т л и ч а ю щ е е с я тем, что, с целью повышения точности синхронизации, оно снабжено двумя

20 элементами И-НЕ двумя RS-.òðèããåðàь ми и распределителем импульсов, вход которого подключен к выходу узла сдвига импульсов, первый вход которого подключен к выходу второго счетчика импульсов, а второй подключен к выходу формирователя импульсов вместе с R-входом второго триггера и входом установки распределителя т-й выход

7 которого подключен к R-входу первого и S-входу второго триггеров, (m-1)-й выход — к S-входу первого триггера, а (m-2)-й выход — к входу установки первого счетчика импульсов, вычитающий вход которого подключен к входу первого, а суммирующий вход к

З5 выходу второго элементов -HE первые входы которых подключены к выходам первого и второго триггеров соответственно, а вторые входы — к выходу делителя частоты, причем вы40 ход первого счетчика подключен к другому входу сумматора, информационный выход которого подключен к входу запоминающего регистра, выход которого подключен к информационному входу

45 второго счетчика импульсов.

1347128

g> = U sin&t

Uc

Ur фиг. 1

Составитель В.Жмуров

Редактор Н.Лазаренко Техред Л.Олийнык Корректор М.Максимишинец

Тираж 658 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5124/49

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4