Д-триггер на полевых транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в качестве D-триггера в интегральных логических цифровых устройствах. Цель изобретения - повышение помехот устойчивости D-триггера на полевых транзисторах. Устройство содержит подкпюченну к тактирующему входу цепь из четырех последовательно соединенных полевых транзисторов с чередующимися типами проводимости каналов , образующих два последовательно соединенных лямбда-диода. При эуом параллельно крайнему, подключенному стоком к общей шине транзистору подключена шунтиру5рщая цепь из двух соединенных последовательно транзисторов с тем же типом проводимости канала. Затвор первого дополнительного транзистора, подсоединенного истоком к общей шине, подключен к D-входу триггера, а затвор второго дополнительного транзистора, подсоединенного стоком к стоку шунтируемого крайнего транзистора, соединен с выходом устройства. 2 ил. i (Л .00 сл со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУ6ЛИН д) 4 Н 03 К 3/286, 3/353

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ с

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗО6РЕТЕНИЙ И ОТКРЫТИЙ (21) 3791897/24-21 (22) 20.09,84 (46) 23.)0.87. Бюл. 9 39 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) Е.Б.Механцев, А.Г.Краснопольский, Г.В.Рысухин и В.И.Гаврилюк (53) 621.374.5(088.8) (56) Авторское свидетельство СССР

)) 453785, кл. H 03 К 3/286, 1973. (54) 0-ТРИГГЕР НА ПОЛЕВЫХ ТРАНЗИСТОРАХ (57) Изобретение относится к импульсной технике и может быть использовано в качестве D-триггера в интегральных логических цифровых устройствах.

Цель изобретения - повышение помехо . устойчивости D-триггера на полевых транзисторах. Устройство содержит

„„SU„„1347153 А1 подключенную к тактирующему входу цепь .из четырех последовательно соединенных полевых транзисторов с чередующимися типами проводимости каналов, образующих два последовательно соединенных лямбда-диода. При этом параллельно крайнему, подключенному стоком к общей шине транзистору подключена шунтирующая цепь иэ двух соединенных последовательно транзисторов с тем же типом проводимости канала. Затвор первого дополнительного транзистора, подсоединенного истоком к общей шине, подключен к

D-входу триггера, а затвор второго дополнительного транзистора, подсоединенного стоком к стоку шунтируемого крайнего транзистора, соединен с выходом устройства. 2 ил.

1347153

Изобретение относится к импульсной технике и может быть использовано в качестве D-триггера в интегральных логических цифровых устройствах.

Цель изобретения — повышение помехоустойчивости D-триггера на полевых транзисторах.

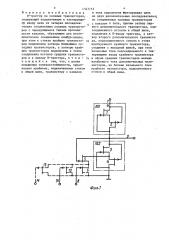

На фиг.l изображена принципиальная электрическая схема D-триггера; на фиг.2 — вольт-амперная характеристика (ВАХ), Устройство содержит полевые транзисторы 1-4, образующие два последовательно соединенных лямбда-диода (ЛД1 и ЛД2), два дополнительных полевых. транзис" îðà 5 и 6, образующие цепь управления по D-входу, при этом транзистор 1 подсоединен стоком к тактирующему входу 7, стоки транзисторов 4 и 6 подсоединены к общей шине, транзистор 6 подсоединен затвором к D-входу 8 устройства, а транзистор 5 подсоединен затвором к выходу 9 устройства.

Устройство работает следующим образом.

В режиме хранения информации на тактирующем входе 7 поддерживается потенциал логической "1", превышающей напряжения отсечек ЛД 1, ЛД 2 и транзистора 6. Лямбда-диоды ЛД1 и

ЛД2, ВАХ которых изображены на фиг.2, кривые 10 и 11 соответственно выбраны таким образом, что lм, lм где lм„ и 1м — максимальные токи

ЛД1 и ЛД2.

Если в триггере хранится код "0", то ЛД1 закрыт, а ЛД 2 открыт. При этом ток в цепи триггера равен току утечки закрытого ЛД1, т.е. потребляемая мощность практически равна нулю, На выходе 9 устройства — логический ."нуль".

Если в триггере хранится код "1", то ЛД1 открыт, а ЛД2 находится в состоянии отсечки. При этом ток в цепи триггера равен току утечки закрытого

ЛД2 и потребляемая мощность также практически равна нулю. На выходе 9 устройства действует напряжение, соответствующее логической "1

Примем для определенности, что в исходный момент на выходе триггера логический "нуль", à íà D-входе 8 действует, напряжение логической "1".

Тогда транзистор 6 закрыт, ЛД1 и ЛД2 имеют ВАХ, изображенную в виде кривых 10 и 11 (фиг.2) соответственно.

Для записи кода "1" необходимо нь тактирующий вход 7 подать логический

"нуль", а затем восстановить потен— циал логической "1" ° Тогда при переходе сигнала на тактирующем входе 7 от "0" к "1" откроется лямбда-диод, имеющий большее значение максимального тока, в данном случае откроется

Ip ЛД1, так как 1м ) 1 м . Изменение

50 l5

ЭО

40 во время действия на тактирующем входе 7 "единичного" потенциала хранения сигнала на D-входе 8 не приво-: дит к изменению состояния триггера, поскольку появление нулевого потенциала íà D-входе 8 не изменяет формы

ВАХ ЛД2.

При записи кода "0" на D-входе 8 действует нулевой потенциал, транзистор 6 открыт и подключен параллельно транзистору 4 лямбда-диода ЛД2, ВАХ которого принимает вид кривой 12 (фиг,2). При нулевом напряжении на

D-входе 8 соотношение максимальных токов лямбда-диодов обратное:

1 м 1M„. Перевод триггера в состояние с нулевым выходным напряжением происходит в момент появления очередного тактового импульса: появление на тактирующем входе 7 "нулевого" потенциала и последующее восстановление "единичного" потенциала хранения приводит к открыванию ЛД2 и запиранию ЛД1. Таким образом, произведена запись кода "0", Если после этого на D-входе 8 появляется сигнал логической "1", то транзистор 6 закрывается и ВАХ ЛД2 принимает исходную форму (кривая 10, фиг ° 2). Однако при этом только изменяется дифференциальное сопротивление открытого ЛД2, а состояние триггера не изменяется.

Рассмотренный алгоритм функциони рования и особенность выполнения управляемого лямбда-диода ЛД2, обеспечивают высокую помехоустойчивость устройства, сохраняющего возможность выполнения функции D-триггера в режиме хранения независимо от колебаний уровня управляющего напряжения на D-входе.

Подключение параллельно транзистору 6 дополнительных полевых транзисторов 13, затворами подключенных к соответствующим шинам 14 управления„ позволяет расширить функциональные возможности устройства за счет реализации функции тактируемого много входового логического элемента И. з

1347

Формула изобретения

D-триггер на полевых транзисторах, содержащий подключенную к тактирующему входу цепь из четырех последова. 5, тельно соединенных полевых транзисторов с чередующимися типами проводимости каналов, образующих два последовательно соединенные лямбда-диода, при этом к стокам крайних транзисто- 1О ров подключены затворы ближайших соседних транзисторов, а затворы крайних транзисторов подключены к точке соединения истоков средних транзисторов и к выходу D-триггера, о т л и— ч а ю шийся тем, что, с целью повышения помехоустойчивости, параллельно крайнему, подключенному стоком к общей шине, транзистору с каналом

153 4 и типа подключена йунтирующая .цепь из двух дополнительных последователь но соединенных полевых транзисторов с каналом и типа, причем затвор первого дополнительного транзистора, подсоединенного истоком к общей шине, подключен к D-входу триггера, а затвор второго дополнительного транэисто ра, подсоединенного стоком к стоку шунтируемого крайнего транзистора, соединен с выходной шиной, при этом начальные токи подсоединенного к так" тирующему входу крайнего транзистора и обоих средних транзисторов меньше .начаЛьного тока дополнительных транзисторов, но больше начального тока . крайнего транзистора, подключенного стоком к общей шине.

Фиг.7

1347153

Составитель Э..Сапежко

Техред И.Верес Корректор В.Бутяга

Редактор Г.Волкова

Заказ 5126/50

Тираж 899 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г ° Ужгород, кл. Проектная, 4