Генератор псевдослучайных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использова- НО в радиотехнике. Цель изобретения - расширение функциональных возможностей за счет увеличения объема ансамбля формируемых сигналов и повьшение быстродействия. Для этого в устройство дополнительно введены счетчик 4 импульсов, блок 5 вычитания, оперативное запоминающее устройство 7, первый 8 и второй 12 триггеры,элемент И 9, блок 15 начальной установки , формирователь 10 импульсов и таймер 11. Кроме того, устройство содержит генератор 1 тактовых импульсов, регистр 2 сдвига, сумматор 3 по модулю два, коммутатор 6,шину 13 кода сдвига, шину 14 разрешения-сдвига, элементы 16,17 и 18 задержки и сумматор 19, входящие в состав формирователя 10 импульсов. Сдвинутый сигнал на выходе устройства формируется , начиная с ближайшего тактового импульса, следующего за командой разрешения сдвига по шине 14, что обеспечивает высокое быстродействие. 1 з.п. ф-лы, 1 ил. I (Л FT Bwx. со 4 а 05 11

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1347166 А 1

Н 03- К 3/84

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ г

Га !

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4017639/24-21 (22) 05.02.86 (46) 23.10.87. Вюл. Ф 39 (72). B.Н. Осьмак, А.Н. Ступин, С.Н. Смирнов и Н.И. Козленко (53) 621.374.2(088.8) (56) Авторское свидетельство СССР

N- 1069139, кл. Н 03 К 3/84, 1982.

Авторское свидетельство СССР

N - 843193, кл. Н 03 К 3/84, 1979. (54) ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ СИГ-

НАЛОВ (57) Изобретение относится к импульсной технике и может быть использовано в радиотехнике. Цель изобретения— расширение функциональных возможностей за счет увеличения объема ансамбля формируемых сигналов и повышение быстродействия. Для этого в устройство дополнительно введены счетчик

4 импульсов, блок 5 вычитания, опе-, ративное запоминающее устройство 7, первый 8 и второй 12 триггеры,элемент И 9, блок 15 начальной установки, формирователь 10 импульсов и таймер 11. Кроме того, устройство содержит генератор 1 тактовых импульсов, регистр 2 сдвига, сумматор 3 по модулю два, коммутатор б,шину 13 кода сдвига, шину 14 разрешения. сдвига, элементы 16,17 и 18 задержки и сумматор 19, входящие в состав формирователя 10 импульсов. Сдвинутый сигнал на выходе устройства формируется, начиная с ближайшего тактового импульса, следующего за командой разрешения сдвига по шине 14, что обес- печивает высокое быстродействие.

1 э.п ф-JIbl 1 С:

1 134716

Изобретение относится к импульсной технике и может быть использовано в радиотехнике.

Целью изобретения является расширение функциональных возможностей за счет увеличения объема ансамбля формируемых сигналов и повышение быстродействия устройства.

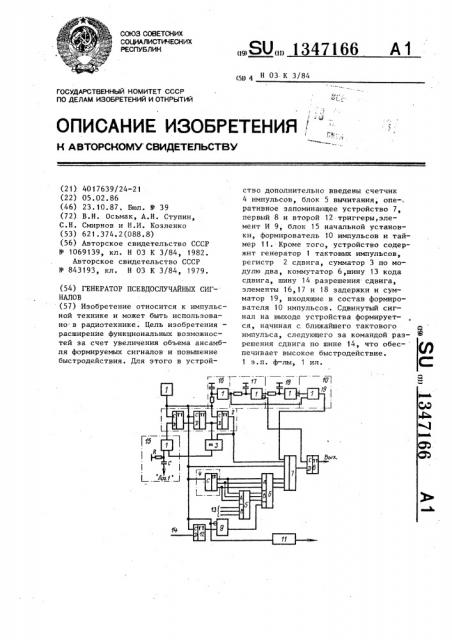

На чертеже представлена функцио- )p нальная схема генератора псевдослучайных сигналов.

Генератор псевдослучайных сигналов содержит генератор 1 тактовых импульсов, выход которого соединен l5 с входом синхронизации регистра 2 сдвига, выходы соответствующих разрядов которого соединены с входами сумматора 3 по модулю два, счетчик

4 импульсов, выходы которого соеди- 2р нены с соответствующими входами первой группы входов блока 5 вычитания и с соответствующими входами первой группы входов коммутатора 6, выходы которого соединены с соответствующи- 25 ми адресными входами оперативного запоминающего устройства (ОЗУ) 7, выход которого соединен с информацион-. ным входом первого триггера 8, элемент И 9, формирователь 10 импульсов, дб таймер 11, второй триггер 12, шину

13 кода сдвига, шину 14 разрешения сдвига, блок 15 начальной установки, вьгход которого соединен с информационным входом регистра 2 сдвига, выход которого соединен с информационным входом ОЗУ 7, вход управления которого соединен с вторым выходом формирователя 10 импульсов, первый выход которого соединен с входом син- 4п хронизации первого триггера 8. Выход генератора 1 тактовых импульсов соединен с входом формирователя 10 импульсов, входом синхронизации ОЗУ 7, входом синхронизации счетчика 4 импульсов, входом таймера 11, входом синхронизации второго триггера 12 и вторым входом элемента И 9, выход которого соединен с входом управления коммутатора 6. Выход сумматора

3 по модулю два соединен с входом блока 15 начальной установки. Шина

14 разрешения сдвига соединена с информационным входом второго триггера 12 выход которого соединен с перУ

-55 вым входом элемента И 9. Шина 13 кода сдвига соединена с соответствующими входами втброй группы входов блока

5 вычитания.

6 2

Формирователь 10 импульсов содержит последовательно соединенные первый 16, второй 17 и "третий 18 элементы задержки и сумматор 19 по модулю два, выход которого является вто-. рым выходом формирователя 10 импульсов, первый выход которого сое-, динен с инверсныя выходом второго элемента 17 задержки. Второй вход сумматора 19 по модулю два соединен с выходом первого элемента 16 задержки, вход которого является входом формирователя 10 импульсов.

Блок 15 начальной установки конструктивно выполнен в виде RC-цепи формирования импульса начальной установки при включении питания и элемента ИЛИ, через который на информационный вход регистра 2 сдвига проходит также сигнал логической обратной связи.

Генератор псевдослучайных сигналов работает следующим образом.

После включения питания регистр

2 сдвига с сумматором 3 по модулю два в цепи обратной связи начинает генерировать исходную псевдослучай-, ную последовательность импульсов, причем блок 15 начальной установки обеспечивает исключение начального

I состояния "Все нули" регистра 2 сдвига.

С выхода регистра 2 сдвига псевдослучайный сигнал поступает на информационный вход ОЗУ 7, которое работает в режиме записи и считывания.

Сигнал, определяющий режим работы

ОЗУ 7, поступает на его вход синхронизации с выхода генератора 1 тактовых импульсов. В первую половину пе-..риода тактовых импульсов в ОЗУ 7 осуществляется запись сигнала с выхода регистра 2 сдвига, а во вторую половину периода тактовых импульсов иэ

ОЗУ 7 — считывание информации. Считываемая из ОЗУ 7 информация поступает после стробирования на первом триггере 8 на выход устройства. Для тактирования работы ОЗУ 7 и первого триггера 8 служат сигналы соответственно с второго и первого выходов формирователя 10 импульсов.

Адресные входы ОЗУ 7 подключены к выходам коммутатора 6, на вход управления которого поступает через второй триггер 12 и элемент И 9. сигнал разрешения сдви-:.à с шины 14 ра.зрешения сдвига. Триггер 12 обеспечи1347166

55 вает привязку команды на сдвиг псевдослучайного сигнала к тактовым импульсам, а элемент И 9 — запрет прохождения команды на коммутатор 6 в первую половину тактового импульса, т.е. в режиме записи ОЗУ 7. На выходе элемента И 9 в первую половину тактового импульса значение сигнала соответствует уровню логического нуля независимо от команды на шине

14 разрешения сдвига. Во вторую половину тактового импульса на выходе элемента И 9 значение сигнала соответствует уровню логического нуля при отсутствии команды на сдвиг и логической единице при-наличии команды на сдвиг по шине 14 разрешения сдвига.

Коммутатор 6 подключает при этом к адресному входу ОЗУ 7 либо выходы счетчика 4, либо выходы блока 5 вычитания ° Таким образом, адресация

ОЗУ 7 в первую половину тактового импульса осуществляется счетчиком

4 импульсов, а во вторую половину— счетчиком 4 импульсов или блоком 5 вычитания соответственно при отсутствии или наличии команды разрешения сдвига по шине 14 разрешения сдвига.

На шине 13 кода сдвига установлен код требуемого сдвига, поэтому на выходе блока 5 вычитания код меньше кода на выходе счетчика 4 импульсов на величину кода на шине 13 кода сдвига.

При отсутствии команды на сдвиг по шине 14 разрешения сдвига в первую половину тактового импульса текущее значение исходной последовательности с выхода регистра 2 сдвига записывается в ячейку памяти ОЗУ 7, адрес которой соответствует значению кода на выходе счетчика 4 импульсов, а во вторую половину тактового импульса осуществляется считывание информации из этой же ячейки памяти.

После стробирования на триггере 8 информация с ОЗУ 7 поступает на .выход устройства с фазой выходного сигнала, соответствующей фазе исходного сигнала с выхода регистра 2 сдвига с учетом привязки сигнала на триггере 8.

При наличии команды ча сдвиг по шине 14 разрешения сдвига в первую половину тактового импульса текущее значение исходной последовательйости с выхода регистра 2 сдвига записыва5

35 ется в ячейку памяти ОЗУ 7, адрес которой соответствует значению кода на выходе счетчика 4 импульсов, а во вторую половину тактового импульса осуществляется считывание информации из ячейки памяти, адрес которой меньше кода на выходе счетчика 4 импульсов на величину кода сдвига по шине

13 кода сдвига. Считываемая при этом с выхода устройства последовательность импульсов задерживается на требуемую величину.

В начале работы устройства после включения питания начинает работать таймер 11, который отсчитывает время, равное или большее периода счета счетчика 4 импульсов, после чего на выходе таймера 11 формируется команда готовности устройства к сдвигу.

В течение времени этой предварительной подготовки, необходимой только при включении питания, осуществляется запись исходной последовательности в ОЗУ 7.

Генератор псевдослучайных сигналов обеспечивает на выходе требуемый сдвиг сигнала при формировании, например, составных, а также укороченных последовательностей и др. Сдвинутый сигнал на выходе устройства формируется, начиная с ближайшего тактового импульса, следующего за командой разрешения сдвига по шине 14 разрешения сдвига, что обеспечивает высокое быстродействие перестройки. формула изобретения

1. Генератор псевдослучайных сигналов, содержащий генератор тактовых импульсов, выход которого соединен с входом синхронизации регистра сдвига, выходы соответствующих разрядов которого соединены с входами сумматора по модулю два, коммутатор, о т л и— ч а ю шийся тем, что, с целью расширения функциональных возможностей за счет увеличения объема ансамбля формируемых сигналов и повышения быстродействия, в него введены-счетчик импульсов, блок вычитания, оперативное запоминающее устройство, первый и второй триггеры, элемент И, блок начальной установки,формирователь импульсов и таймер, причем выходы счетчика импульсов соединены с соответствующими входами первой группы входов коммутатора и с соответствуб е мутатора, выход генератора тактовых импульсов соединен с входом формирователя импульсов, второй выкод которого соединен с входом управления оперативного запоминающего устройст-. ва, информационный вход которого соединен с выходом регистра сдвига,информационный вход которого соединен с выходом блока начальной установки, вход которого соединен с выходом сумматора по модулю два.

134716 ющими входами первой группы входов блока вычитания, выход оперативного запоминающего устройства соединен с информационным входом первого триггера, вход синхронизации которого со5 единен с первым выходом формирователя импульсов, шина разрешения сдвига соединена с информационным входом второго триггера, выход которого соединен с первым входом элемента И, шина кода сдвига соединена с соответствующими входами второй группы входов блока вычитания, выходы которого соединены с соответствующими входами второй группы входов коммутатора, выходы которого соединены с соответствующими адресными входами оперативного запоминающего устройства, вход синхронизации которого соединен с выходом генератора тактовых импульсов, входом синхронизации счетчика импульсов, входом синхронизации второго триггера, входом таймера и вторым входом элемента И, выход которого соединен с входом управления ком2. Генератор по п, 1, о т л и— ч а ю шийся тем, что формирователь импульсов содержит последова" тельно соединенные первый, второй, третий элементы задержки и сумматор

rio модулю два,второй вход которого соединен с выходом первого элемента задержки, вход которого является входом формирователя импульсов, первый и второй выходы которого соединены соответственно с инверсным выходом второго элемента задержки и выходом сумматора по модулю два..Составитель Ю. Бурмистров

Техред И.Попович Корректор М, Демчик

Редактор И. Шулла

Тираж 899

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5127/51

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4