Устройство для формирования цифровых синхроимпульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике, к устройствам для генерирования синхронизирующих сигналов. Отличительной особенностью устройства является возможность оперативного изменения выходных сигналов. Целью изобретения является расширение функциональных возможностей за счет оперативного изменения выходных сигналов. Поставленная цель достигается за счет введения коммутатора 2 и блока 4 сравнения. 4 ил. J2 13 С в f}« со 4 00 00 о 00 Фиг. /

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСОУБЛИН (50 4 G 06 F 1/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИ4ЕТЕЛЬСТВУ

TO

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

00 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3941042/24-24 (22) 01.08.85 (46) 30.10.87. Бюл. У 40 (72) А.M.Òêà÷åíêo, В.M.Óëüÿíîâ и А.Г.Юрочкин (53) 681.3(088.8) (56) Приборы и техника эксперимента, М 2, 1984. М.:Наука, с. 67-69.

Патент США М 4404644, кл. С 06 F 1/02, 1983. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

ЦИФРОВЫХ СИНХРОИМПУЛЬСОВ

„„SU„„1348808 A 1 (57) Изобретение относится к цифровой вычислительной технике, к устройствам для генерирования синхронизирующих сигналов. Отличительной особенностью устройства является воэможность оперативного изменения выходных сигналов. Целью изобретения является расширение функциональных возможностей эа счет оперативного изменения выходных сигналов. Поставленная цель достигается за счет введения коммутатора 2 и блока 4 сравнения.

4 ил.

1348808

Л5

Изобретение от»о«»тся к цифровой вычислительной технике, к устройствам для генер»рова»ия г»нхронизируюших сигналов.

Целью изобретен»я является расширение функциональных возможностей за счет оперативного изменения выходных импульсов.

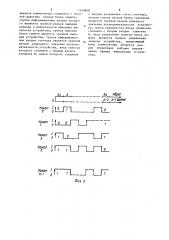

На фиг. t приведена структурная схема устройства; на фиг. 2 — временная диаграмма примера формирования импульсов для К каналов;на фиг. 3 временная диаграмма управления записью информац»» в блок памяти; на фиг. 4 — временная диаграмма считывания информации »э блока памяти.

Устрой>-тво содержит блок 1 памяти, коммутатор 2, счетчик 3, блок 4 сравнения, элемент И 5, задающий генератор 6, группу 7 входов начального значения, вход 8 запуска, вход 9 управления выбором направления приема информации, вход 10 у»равления записью, группу входов 11 конечного значения, группу вхо;к»» 12 задания вы— ходного к;»нала, груп»у входов !3 задания периода и длит«:tl;Hoc TH Bl,txo, IIII tx импульсов, t-pyI»ty выходов 14.

Устройство раб«тая г следующим разом.

Работа начинается с его программ»в рования для формир»»»а»»ия необходимых серий цифроны::, с»гttcl I

Рассмотрим пример записи в блок 1 памяти информации об одной из серий цифровых сиг»алев, отражающей изменение во времени каждого иэ формируемых по с»эот»»етст»»yt»»ùpìó каналу формирователя »ифроных сигналов, » последующего форм»р(на»ия из нее серии цифровых гиг»а »ов, »о К каналам в соответствии г временной диаграммой приведенной на фи:. . . Изменения во времени (фиг. 2) »ифровых сигна»»ов равны периоду тактовых импульсов, гp нерируемь»х эадакщ»м <енератором 6.

Состояние ц»фрон.,tx г»1»алов по кана— лам О, 1,..., 11 — I t» течение лк»бо— го указанного »»ыше интeðâà Ià времени выражается двоич»ь»м числом, в котором его ну.» »ому разряду соответствует сост«»я»»»»е и:»ф1»»»о» о сигнала Elo каналу О, »с р.«.му разряду — состоя— ние цифр но»г! г»г»;»л;» по каналу 1, К-1. 1:1»t т, ."-1 ч»г.to 1 ... 1100, 5

55 соответствующее состоянию цифровых сигналов в течение интервала времени

0-г, записывается н ячейку блока 1 памяти с адресом А, число 1

1001, соответствующее состоянию цифровых сигналов в течение интервала времени t -t,, — в ячейку памяти с адресом А,, наконец, число 1 ...0110, соответствук»щее состоянию цифровых сигналов в течение интервала времени в ячейку памяти с адресом A

Ра«смотрим процесс записи информации в блок 1 памяти.

Перед записью на входах устройства установленьш на входе 8 запуска

"О", на входе 9 — "О", на входе 10

"1". При этом коммутатор 2 пропускает на адресные входы блока 1 памяти адрес,уст l»овлс нный на входах 12 устройства. При записи информации в указанные выше ячейки памяти блока 1 необходимо в соответствии с временной диаграммой, представленной на фиг. 3, установить на входах группы

12 адрес ячейки памяти, на входах гру»пы 13 — соответствующие значения разрядов двоичного числа, отражающ» го гостояние цифровых сигналов, » затем установить на входе 1О устройгтва "t)".Òàêèì образом, в области памяти блока 1, на »»»ая с адреса А

» I»

» хра»итгя »нформация о серии цифровых «»г»алов, изображе»ных на фиг. 2.

Лна It)l »чно в дру1 не области памяти блока 1 может быть записана информация о других сериях цифровых сигнало 1» .

Погле окончания программирования устр»1йство »одготавливается к формирован»ю одной из записанных в его блок 1 памяти серий цифровых сигналов. При этом на входе 10 устанавливаетгя "1", »а входах группы 7 устанавл»вается начальный адрес области памяти, хранящей информацию о выбранной для формирова»ия серии цифровых сигналов (1» нашем примере это А„), а на входах группы 11 устанавливается конечный адрес этой области памяти (» »»апем примере это А„ 1 ). Установленный ранее на входе 8 логический нуль погту»ает чере.» элемент И 5 на вход разрешения г»»«та счетчика 3, »ри этом счетчик 3 находится в режиI»p »а »альной загрузки,при котором поступакшие »а ггo счетный вход так1348808

?5 тоные импульсы (с выхода гене1>атора

6) устанавлинан>т и,> его выходах установленный на входах группы 7 входов начальный адрес Л р 5

Формирование выбранной серии цифровых сигналов осуществляется в ре— зультате поочередного считывания информации из ячеек блока 1 памяти,начиная с ячейки памяти с адресом Л, 10 и кончая ячейкой памяти с адресом

А р,, в соответствии с временной диаграммой, представлен ой на фиг. 4 (для большей наглядности на диаграм-ме не покаэаны временные задержки 15 при формировании и распространении сигналов).

Формирование серии цифровых сигнаI лон начинается с установки на входе

9 логической единицы (момент времени 20

О на диаграмме). При этом коммутатор

2 пропускает на адресные входы блока

1 памяти адрес Л „ с выходов двоичного счетчика 3 и на выходах О, 1, К-1 блока памяти появляется считываемая из ячейки памяти Л инс формация l ... 1 l00, которая соотнет— ствует состоянию цифровых сигналон в интервале времени О-г, (фиг. 2).

Затеи на входе 8 устанавливае гся 1! 30 которая через элемент И 5 поступает на вход разрешения счета счетчика 3 (на второй вход элемент И 5 и с выхода блока 4 сравнения поступает "1", соответствующая отсутствию сигнала 35 сравнения) и переводит его в режим счета. Под воздействием поступающих на счетный вход тактовых импульсон. в моменты времени t

» . p.rj на ныходах счетчика 3 поочередно фор- 40 мируются соответственно адреса ячеек памяти блока 1 памяти, поступающие через коммутатор на адресные входы блока 1 памяти, при этом на его выходах О, 1, ..., К-1 появляет- 45 ся поочередно считываемая из указанных ячеек памяти информация 1

1001 в интервале времени t -t 1 ... ° о

01100 в интервале времени

Р- 2. ср,, из которой на выходах О, 1, К-1 формирователя складывается формируемая серия цифровых сигналов, соответствующая временной диаграмме на фиг. 2. После формирования счетчиком 3 адреса, совпадающего с конечным адресом, установленным на входах

11,на выходе блока 4 сравнения поян>! (! ляется О соответствующий выра б о тк е логического сигнала с р а в н е ния, и ереводящий счетчик 3 через элемент

И 5 н режим начальной загрузки,при котором под ноздействием очередного тактового импульса, поступающего н момент времени t,,на счетный вход счетчика 3, на его выходах устанавливается начальный адрес,при этом на выходе блока 4 сравнения снимается логический сигнал сравнения (т.е. появляется "1") и счетчик 3 вновь переводится в режим счета. Таким образом, начинается повторное формирование заданной серии цифровых сигналов и т.д. Для прекращения формирования данной серии цифровых сигналов на входе 8 устанавливается "О",который переводит счетчик 3 через элемент И 5 из режима счета в режим наначальной загрузки.

Для формирования другой серии цифровых сигналов (информация о которой была ранее записана в блоке 1 памяти при его программировании) на входе 8 устанавливается "О", на входах группы 7 устанавливается начальный адрес области памяти, хранящей информацию о новой серии цифровых сигналов, на входах группы 11 устанавливается конечный адрес области памяти, хранящей информацию о новой серии цифровых сигналов, затем снова на входе 8 формирователя устананли>! >! н а е т с я 1 ., Далее в соответствии с описанной и о сл е д о н а т ел ь но с т ью происходит формирование новой серии цифр о вых сигналов .

Формул а изобретения

Устройство для формирования цифровых синхроимпульсов, содержащее задающий генератор, счетчик, блок памяти, причем выход задающего генератора соединен со счетным входом счетчика, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных воэможностей за счет оперативного изменения периода и длительности выходных импульсов, в устройство введен коммутатор, блок сравнения и элемент И, причем группа выходов разрядов счетчика соединена с первой группой информационных входов блока сравнения и с перной группой информационных входов коммутатора, вторая группа информационных входов которого является группой входов задания выходного канала устройства, группа

1348808

Каюл

1 0 выходов коммутатора соединена с группой адресных входов блока памяти, группа информационных входов которого является группой входов задания

5 периода и длительности выходных импульсов устройства, группа выходов блока памяти является группой выходов устройства, группа информационных входов счетчика является группой входов канального значения последовательности устройства, вход запуска которого соединен с первым входом элемента И, выход которого соединен с входом разрешения счета счетчика, вторая группа входов блока сравнения является группой входов конечного значения последовательности устройства, выход неравенства блока сравнения соединен с вторым входом элемента

И, вход управления записью блока памяти является входом управления записью устройства, управляющий вход коммутатора является входом управления выбором направ— ления приема информации устройства.

1348808

Время g

1 а

10 а

Див. г ея-е еяВрмя

I в

ВьчИы гаетаиа J пресные 1 ! пааы dpDhp l Ag Ау памяти D йчаВы r., Пса 1... iW

Рис Ф

Редактор Н.Слободяник

Заказ 5190/47 Тираж 670

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Сетныа Rod

cvrmvuxa3 1

Составитель Н.Торопова

Техред М.Ходанич Корректор B.Áóòÿãà