Устройство для формирования сигналов прерывания при отладке программ

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и предназначено для использования при отладке программ специализированных вычислительных систем реального времени. Цель изобретения - расши10 рение функциональных возможностей устройства. Цель достигается тем, что в устройство, содержащее первый 1, второй 4 регистры, счетчик 11 адреса , первую 2 и вторую 3 схемы срав нения, первый 5, второй 6 и третий 7 элементы И, введены блок 12 памяти, четвертый регистр 13, мультиплексор данных 14, первый 15, второй 16, третий 17 и четвертый 18 элементы НЕ, первый 19 и второй 20 элементы ИЛН-НЕ, четвертый 21 и пятый 22 элементы И, первый 23, второй 24, третий 25, четвертый 26, пятый 27 и шестой 28 элементы задержки, а также первый 29, второй 30, третий 31 и четвертый 32 формирователи длитель ности с соответствующими связями. 1 ил. - S (/ С е

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1

„„SU„„i 348841 (51)4 С 06 F 11 28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

35

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4073998/24-24 (22) 04.06.86 (46) 30.10.87. Бюл. М 40 (72) И.В.Бурковский, Я.M.Áóäîâñêèé, К,В.Богданова и И.В.Гольдберг (53) 681,3 (088 ° 8) (56) Авторское свидетельство СССР

Ф 962945, кл. G 06 F 11/28, 1980.

Авторское свидетельство СССР

У 1185343, кл. С 60 F 11/28, 1984. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

СИГНАЛОВ ПРЕРЫВАНИЯ ПРИ ОТЛАДКЕ

ПРОГРАММ (57) Изобретение относится к цифровой вычислительной технике и предназначено для использования при отладке программ специализированных вычислительных систем реального времени. Цель изобретения — расширение функциональных возможностей устройства. Цель достит ается тем, что в устройство, содержащее первый

1, второй 4 регистры, счетчик 11 адреса, первую 2 и вторую 3 схемы сравнения, первый 5, второй 6 и третий 7 элементы И, введены блок 12 памяти, четвертый регистр 13, мультиплексор данных 14, первый 15, второй 16, третий 17 и четвертый 18 элементы

НЕ, первый 19 и второй 20 элементы

ИЛИ-НЕ, четвертый 21 и пятый 22 элементы И, первый 23, второй 24, третий 25, четвертый 26, пятый 27 и шестой 28 элементы задержки, а также первый 29, второй 30, третий 31 и четвертый 32 формирователи длительности с соответствующими связями.

1 ил.

1 «RR- 1

Иэобретp»I!f относится к »ычислительной тс.хинке и может быть использовано при отллдке программ специализирован<.ых цифровых»1(числител1 гн(х систем (С!1!«С) pe H..lü»oão времени.

Целью и эоГретения являс тс я рлс— ширение фу»клиона (ьных »озможностс и устройства зл счет запоминания множества точек адресного по:(я Э!«!1, при обращении к h(тор1<м треГуется формирование сигнллл прерь(влния.

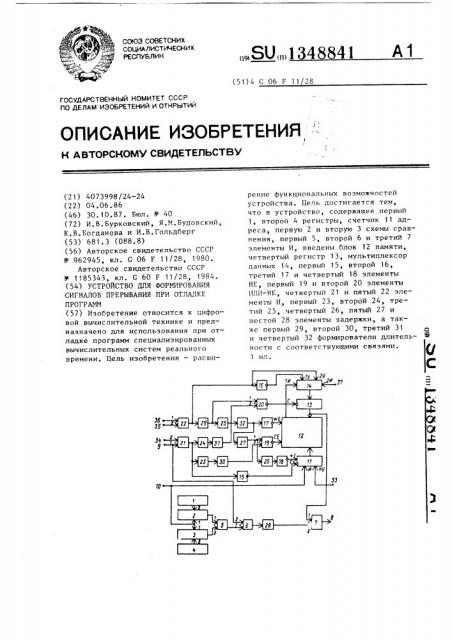

На чертеэ(е (хематично изобрлжеiio устройство д:(я формиро»лния гигнл1он! и! эО прерывания при отладке программ. 1с

Предлагаемое устройство содержит первый регистр 1, первую 2 и вторую 3 схемы с.равнения, второй регистр 4, первый 5, второй 6 и третий 7 элементы И, »Itxo;! 8 пре!эывлния у(<тройства, вход 9 стробл адреса, лдреси(<11 вход 10 устройства, счетчик !! лдр(— са, блок 12 памяти, третий регистр

13, мультиплексор 14 данных, ttpp»!,<й

15, второй 16, третий 17 и чет»ертый 18 элемснты НЕ, первый 19 и второй 20 э.!Pnie нты И Н«-НЕ, четвертый

21 и пятый 22 элементы И, и рьч lii 23 второй 24, третий 25, четвсрт ый 26, пятый 27 и шестой 28 элемс1нт<1 .<лдс ржки, первый 29, второй 30, Tðñ тt!H 31 и четвертый 32 формирователи д.(ит(льности, вход 3 «нлчл.-(ьной устлновки устройства, первый 34 и второи 35 входы устал(»<ки режима устроист»л, 36 вход 36 строГл данных, вход «7 длн—

Hых устрой(.т»л.

Рассмотрим рлботу устройства (o»местно с (этлл:кинешмой СЦВС, постро— енной нл базе Э1Р! типа Э.t(ктроника-60" . Лдрес((ые вхс ды 10 устроиствл подключены к магистрали микроЭ!Р1, через которую осуп:ествляется обмен информацие11 между (.е раз.((ич1iыми уст ройствами, I«Yo„ 9 стробл лдресл ус т— ,! г ройства подклю-(лется, например, к шине Обмен" мик!эо<Э!«. 1, Сигнлсп< нл входы начл:il.ной устлно»ки .««, Ilpp»i i;i

Зч и второи 5»ходы уc TBHo»tiи ре. Hnt» работы IIoLI(1ются, нлпример, с .1ицево11 панели упр.<»пения устройствл (не нов клзлнл) . B. iод .7 данных и »ход 36 строб а цл<1»и <х и дьлючены ь»II(шнему устроистну, на<1!»1«еp стендонои Э!«М, обеспечив лющ(й 3(I!It!ch информлции н блок 1 IIDn

Вых ад 3 преры»лния устройства подключаfi т с я i; си» T(м(Ilpе phl»;I и ия СIIР С .

Работа ус т! .1(. I<;I kiлчинл TPH с. рлз— метки блока 12 памяти и устлновки ис.хопных данных в регистрах 1 и 4 и г

В режиме загрузки исходных данных на первый вход 34 установки режима подается сигнал уровня 0, а нл второй вход 35 — "1", что соответствует режиму записи в блок 12 памяти.

Гигнллом с входа 33 устройства уста»а»с<и»лют в нлчл.-(ьное,нулевое) cocf тояние счетчик 11. На входы 37 и 36 устройства подают от внешнего устройства соответственно данные для записи в Глок памяти и сопровождающий их строГ данных. Строб данных через элемент И 22 проходит на второй установленнь|й вход мультиплексора 14,разрс.шля прохождение данных с входа 37 у тройства через Móëüòèïëåêñoð 14 на

» :оц регистра 13. Кроме того, сигнал с выхода элемента 22 после формировлния по длитеэ<ьности на формировате:(е 29 через первый вход элемента 20 поступает на тактовый вход С регистрл 13, осуществляя запись в него данных. Сигнал с выхода формирователя 29 после задержки на элементе 25 нл врсмя заноса данных в регистр 13 формируется 11о длительности на элеn1piiте 32 и через инвертор 17 поступает нл режимный вход записи блока 12 памяти. Одно»ременно сигнал с выхода фо!э< ирователя 32 после задержки на элементе 27 нл время, определяемое требонлниями временной диаграммы блока памяти, через элемент ИЛИ-HE 19 ни. ким уровнем поступает на вход опроса блока 12 памяти. В результате нл входах б.1ока 12 памяти формируют(я сигналы, обеспечивающие запись данных с вх(эдл 37 по адресу, установленному на счетчике 11. При этом сигнал с выходл .<лемента 27 после задержки на племен ге 26 на время записи информации чс рез инвертор 18 поступает на счетньп1 вход счетчика

11, увеличивая его содержимое на

« « !

, тем самым подготавливая устрой1348841 ствс к записи следующего слова данных. Обращаясь последовательно к ячейкам блока 12, помечаем, например, путем записи "1" адреса единого поля

ЭВМ, при обращении к которым необходимо осуществить прерывание отлаживаемой программы. При этом, если адресный» массив блока 12 меньше полного массива адресов микроЭВМ, то адрес памяти в адресном поле ЭВМ определяется регистрами 1 и 4, задающими положение массива блока 12 памяти в адресном поле ЭВМ, и составлением счетчика 11 регистра, в котором фиксируется некоторая младшая часть адреса, сформированного в магистрали 3BM °

После заноса исходных данных и разметки блока 12 на входе 34 устанавливается потенциал высокого уровя "1", а на входе 35 — низкого уровня 0", что соответствует режиму отладки программ. В результате разрешается прохождение строба адреса с выхода 9 через элемент 21. Формируется потенциал низкого уровня на втором установочном входе мультиплексора 14, запрещающий прохождение в устройство данных с входа 37.

Через инвертор 16 на первый установочный вход мультиплексора 14 поступает потенциал высокого уровня, разрешающий прохождение информации с выхода блока 12 на регистр 13. В режиме отладки при выполнении микроЭВМ некоторой программы строб адрес с входа 9 устройства через элемент 21 и инвертор 15 поступает на установочный вход С счетчика 11, занося в него состояние магистрали, т.е. код адреса, с адресного входа 10 устройства ° Потенциал низкого уровня с выхода элемента 22 через элементы

29, 25, 32 и 17 поступает сигналом высокого уровня на вход записи блока 12 памяти. Положительный сигнал с выхода элемента 21 задерживается на элементе 23 на время, необходимое для записи в счетчик 11 адреса с входа 10, и после формирования по длительности на формирователе 30 через элемент 19 отрицательным импульсом поступает на вход опроса блока 12 памяти. Сочетание потенциала высокого уровня на режимном входе и низкого уровня на входе опроса соответствует режиму считывания информации для блока 12 на вход муль45

Устройство для формирования сигналов прерывания при отладке программ, содержащее первый и второй регистры, счетчик адреса, первую и вто,рую схемы сравнения, первый, второй

50 и третий элементы И, причем адресный

5

»

?О

»О типлексора 14 и далее на вход регис ра 13. Сигнал с выхода элемента 21 задерживается с помощью элемента 24 на время, необходимое для считывания информации из блока 12, формируется по длительности на элементе 31 и через элемент 30 поступает на установочный вход С регистра 13, фиксируя в нем считанную из памяти информацию. При этом, если иэ памяти считана единичная информация, то на первом входе элемента 7 будет соответствующий логический сигнал. Уровень сигнала на втором входе определяется текущим опросом в магистрали и состоянием регистров 1 и 4. Текущий адрес с входов 10 устройс гва поступает на первые входы схем 2 и 3 сравнения. На выходе схемы 2 формируется положительнь»»» потенциал, если текущий адрес меньше адреса верхней границы, установленного на регистре 1, а на выходе схемы 3 — если больше адреса нижней границы, фиксированного на регистре 4. Па выходе элемента И 5 будет положительный потенциал, если текущий адрес находится в зоне, ограниченной содержимым регистров 1 и 4. В этом случае через элемент 6 проходит строб адреса с входа 9, задерживается на элементе 28 на время считывания информации из блока 12 памяти и поступает на второй вход элемента 7. В результате вырабатывается сигнал прерывания на выходе

8 устройства. Если текущий адрес не принадлежит массиву, заданному регистрами 1 и 4, или из блока 12 памяти считана нулевая информация, то сигнал прерывания на выходе 8 устройства не формируется.

Ф о р м у л а и э о б р е т е н и я вход устроиства соединен с входами первых сравниваемых чисел первой и второй схем сравнения, выходы первого и второго регистров соединены с входами вторых сравниваемых чисел соответственно первой и второй схем сравнения, выходы равенства которых соединены соответственно с первым и

1348841

Составитель И. Сигалов

Техред А.Кравчук Корректор N.Ïoæî

Редактор Е.Копча

Заказ 4803/49 Тираж 670 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 вторым входами первого элемента И, выход первого элемента И соединен с первым входом второго элемента И, вход строба адреса устройства сое5 динен с вторым входом второго элемента И, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет запоминания множества точек адресного поля ЭВМ, при обращении к которым требуется формирование сигнала прерывания, в устройство введены блок памяти, третий регистр, мультиплексор данных, первый, второй, третий и четвертый элементы НЕ, первый и второй элементы ИЛИ-НЕ, четвертый и пятый элементы И, шесть элементов задержки, четыре формирователя длительности, причем входы стро- 20 ба адреса и первый вход установки режима устройства соединены соответственно с первым и вторым входами третьего элемента И, выход которого соединен через последовательно сое- yr диненные первый элемент задержки и первый формирователь длительности с первым входом первого элемента ИЛИ-НЕ, через последовательно соединейные второй элемент задержки и второй формирователь длительности — с первым входом второго элемента ИЛИ-НЕ и через первый элемент НŠ— с тактовым входом счетчика адреса, адресный и установочный входы устройства соединены соответственно с информационным входом и входом начальной установки счетчика адреса, выход которого соединен с адресным входом блока памяти, вход строба данных и второй вход

40 установки режима устройства соединены соответственно с первым и вторыми входами четвертого элемента И, выход которого соединен с первым управляющим входом и через второй элемент

НŠ— со вторым управляющим входом мультиплексора данных, выход которого соединен с информационным входом третьего регистра, выход четвертого элемента И через третий формирователь длительности соединен с входом третьего элемента задержки и вторым входом второго элемента ИЛИ-НЕ, выход которого соединен с тактовым входом третьего регистра, выход третьего элемента задержки соединен через четвертый формирователь длительности с входом третьего элемента НЕ, через четвертый элемент задержки— с вторым входом первого элемента

ИЛИ-НЕ и через пятый элемент задержки — с входом четвертого элемента НЕ, выход которого соединен со счетным входом счетчика адреса, вход данных устройства соединен с первым информационным входом мультиплексора данных, группа разрядных выходов третьего регистра соединена с группой информационных входов блока памяти и с группой входов пятого элемента И, выход которого является выходом прерывания устройства, выход второго элемента И через шестой элемент задержки соединен со стробирующим входом пятого элемента И, выходы третьего элемента НЕ и первого элемента

ИЛИ-НЕ соединены соответственно с входами записи и обращения блока памяти, выход которого соединен с вторым информационным входом мультиплек. сора данных.