Запоминающее устройство с обнаружением ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и устройствах. Цель изобретения - повьппение надежности работи. Запоминающее устройство содержит блок 1 памяти, блок 2 кодирования, блок 3 управления режимом, регистр 4, блок 5 обнаружения ошибок, коммутатор 6, две группы элементов И 7, 8, селекторы 9, 10, блок 11 управления считьшаниеь:-записью. Устройство формирует контрольные коды для любого формата поступающей информации , причем производятся контроль вновь поступающей информации вместе с ранее записанной, что улучшает качество контроля 1П фор 5Лции в блоке памяти. Кроме того, обеспечена возможность работы как с полноразр5щными двухбайтовыми словами, так и с отдельными четйыми ч чгчетчычп байтами с автоматичес i (,...р,-;,-.рС оакием слов и контрольных ьолс. . в блоке памяти и распределением o. L/ oi но словам . 3 ИГ: . S 00 4 00 СО Выходное I ИРГИяЛ-:

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ЯРухЮпит

80С CJ7

Ч67иЫ

НВ067Н

УС/77. дОЛИ

НР0

Овт

Фие.!

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4020042/24-24 (22) 06,02,86 (46) 30 ° 10,87. Бюл, Ф 40 (72) Л,В.Алексеев, З.М.Демидова, А,Д,Жучков, В,И.Косов, О,В.Росницкий, А,И.Савельев и З,А,Чумакова (53) 681,327 (088.8) (56) Авторское свидетельство СССР

11- 483705, кл. С 11 С 7/00, 1974 °

Авторское свидетельство СССР

У 1014042 кл, G ll С 29/00, 1983, (54) ЗАП01 ИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК (57) 1!зобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и устройствах, Цель изобретения — повышение надежности работы.

Запоминающее устройство содержит

„„SU„„1348913 А 1 блок 1 памяти, блок 2 кодирования, блок 3 управления ре::имом, регистр

4, блок 5 обнаружения ошибок, коммутатор 6, две группы элементов И 7, 8, селекторы 9, 10, блок 11 управления считыванием-записью, Устройство формирует контрсльные коды для любого формата поступающей информации, причем производится контроль вновь поступающей информации вместе с ранее записанной, что улучшает качество контроля и. формации в блоке памяти, Кроме того,. обеспечена воз.можность работы как с полноразрядными двухбайтовыми словами, так и с отдельными четными « ча,eтчычн байтами с автоматичес ., -:,.:;,:р ., ни| м слов и контрольных е, . л, . в блоке н,1мяти и распределени.—; (.;;..ов о славам. 3 ил.

1348913

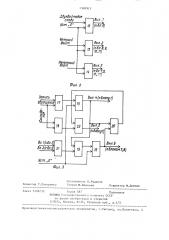

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и устройствах, Пель изобретения — повышение надежности устройства, На фиг,! представлена функциональная схема запоминающего устройства; на фиг, 2 и фиг ° 3 — примеры выпол- )p нения функциональных схем блока управления режимом и блока управления считыванием-записью соответственно.

Запоминающее устройство содержит (фиг.l) блок 1 памяти, блок 2 кодиро- 15 вания, блок 3 управления режимом,регистр 4, блок 5 обнаружения ошибок, коммутатор 6, первую группу элементов И 7, вторую группу элементов И 8, первый селектор 9, второй селектор 20

10, блок ll управления считываниемзаписью, Блок 3 содержит (фиг,2) первый триггер 12 второй триггер 13 и третий триггер 14, 25

Блок 1 1 содержит (фиг, 3) первый триггер 15, второй триггер 16, четыре элемента И 17-20 и два элемента

ИЛИ 21 и 22, Устройство работает следующим 30 образом.

Перед началом работы в устройство поступает сигнал "Установка 0, который устанавливает все элементы и блоки в исходное состояние, 35

В режиме записи и считывания полных двухбайтовых слов устройство работает следующим образом, В режиме записи на элемент И 17 блока 11 поступают сигналы "Запись" 4р и Обращение, которые устанавливают триггер 12 в состояние "1", На коммутатор 6 с информационных входов устройства подается код записываемого слова, который через селекторы 45

9 и 10 передается на запись в блок 1 и на блок 2 для формирования контрольных разрядов слова, С блока 2 контрольные разряды также передаются в блок 1 для записи вместе с пос- 50 тупившим словом. Управляет записью полного слова триггер 12 блока 3, на который при этом поступает управляющий сигнал, устанавливающий его в состояние "!" °

56

В режиме считывания информации на элемент И 18 блока 11 подается управляющий потенциал Считывание", и сигнал "Обращение" через элемент

И 18, элемент ИЛИ 22 запускает блок l, Из блока l в регистр 4 считывается полноразрядное слово вместе с контрольными разрядами, Это слово передается на информационные выходы устройства и вместе с контрольными разрядами на блок 5, где осуществляется контроль и коррекция считываемой информации, Прй обнаружении некорректируемой ошибки в блоке 5 формируется сигнал "Ошибка", сигналиэирующий процессору (не показан) о наличии неисправности в запоминающем устройстве. При обнаружении коррек- . тируемой ошибки блок 5 исправляет в необходимом порядке информацию, и на информационные выходы выдается правильный код.

Рассмотрим работу устройства при обработке неполных слов (отдельно четных и нвчетных байтов). При этом хранение информации в блоке 1 осуществляется все равно полными двухбайтовыми словами. При работе с четными байтами сигналом с входа

"Четный байт" устанавливается в состояние "1" триггер 13 блока 3. Сигнал разрешения с этого триггера открывает элементы И 8 и управляет работой селектора 9.

В режиме записи сигналами с входов "Запись" и "Обращение" через элемент И 17 устанавливается в состояние "1" триггер 15 блока 11, разрешая тем самым запись информации в блок 1. Сигналом с триггера 13 блока

3 через элемент ИЛИ 21 и элемент

И 19 блока 11 устанавливается в состояние "1" триггер 16, который открывает элементы И 8 и через элемент

И 20 и элемент ИЛИ 22 блока 11 производит считывание уже записанного в блок четного байта, который с регистра 4 подается через элементы

И 8 и селектор 10 на запись в блок одновременно с четным байтом, который передается на блок 1. с информа-. ционных входов устройства через коммутатор 6 и селектор 9 ° Одновременно в блоке 2 формируются контрольные разряды полного слова (вновь поступившего четного байта и записанного ранее нечетного байта, которые также записываются в блок 1), Аналогично производится запись нечетного байта и формирование контрольных разрядов для всего слова, 1348913

В устройстве имеется ноэможность подачи байтов только по информационным входам устройства. Попеременное срабатывание триггеров 13 и 14 блока 3 позволяет записывать через входы селекторов 9 и 10 четные и нечетные байты на требуемые места в полнораэрядной ячейке блока 1 с формированием контрольных разрядов в блоке 2 для всего полноразрядного слова.

Формула из обре тения

Запоминающее устройство с обнаружением ошибок, содержащее блок памяти, блок кодирования, регистр, блок обнаружения ошибок и коммутатор,причем входы контрольных разрядов блока памяти подключены к выходам кодирования, выходы блока памяти соединены с нходами регистра, выходы которого являются информационными выходами устройства и соединены с входами блока обнаружения ошибок, первый выход которого является вьмодом

It 1>

Ошибка устройства, второй выход блока обнаружения ошибок подключен к управляющему входу регистра, вход установки в "О" которого является установочным входом устройства, информационные входы коммутатора являются информационными входами устройства, адресный вход блока памяти является адресным входом устройства> отличающееся тем, что, с целью повышения надежности устройства, в него введены первый и второй селекторы, первая и вторая группы элементов И, блок управления режимом и блок управления считыванием-записью, причем входы установки в "О" блока управления режимом и блока управления считыванием-записью подключены к установочному входу устройства, входы разрешения считывания-записи четного байта, нечетного байта и двухбайтового слова блока управ5

45 ления режимом являются соотнетственно входом "Четный байт", входом "Нечетный байт" и входом "Днухбайтоное

1> слово устройства, входы разрешения записи, считывания и обращения блока управления считыванием-записью являются соответственно входом Запись >

"Считывание" и "Обращение" устройства, первый и второй выходы блока управления считыванием-эаписью соединены с входами считывания и записи блока памяти, входы информационных разрядов блока памяти и входы блока кодиронаиия поразрядно объединены и подключены к соответствующим выходам первого и нторого селекторов, перный информационный вход первого селектора и первый информационный вход второго селектора объединены и подключены к первому выходу коммутатора, второй информационный вход второго селектора соединен с вторым выходом коммутатора, третий выход блока управления считыванием-записью подключен к первым входам элементов

И первой и второй групп, вторые входы которых соединены с выходами регистра, первый выход блока управления режимом подключен к управляющему входу коммутатора, второй выход блока управления режимом соединен с третьими входами элементов И второй группы, управляющими входами Четный байт" первого и второго селекторов и входом "Обращение к четному байту" блока управления счи >, ванием-записью, третий выход блока управления режимом подключен к третьим входам элементов И первой группы, входам "Нечетный байт" первого и второго селекторов и входу "Обращение к нечетному байту" блока управления считыванием-записью, второй информационный вход первого селектора и третий информационный вход второго селектора подключены к выходам элементов И соответственно первой и второй групп, 1348913

Д/уИайпФю

С/7

germ.

Уела баит чет айт

Рие. 2

Фцг, Л,Составитель В. Рудаков

Техр ед М. Хода нич

Корректор М,Демчик

Редактор Т.Лазоренко

Заказ 5196/52

Тираж 587 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, iK-35, Раунская наб,, д.4/5

Производственно-полиграфическое предприятие, r,Óæãoðîä, ул,Проектная, 4