Усилитель считывания

Иллюстрации

Показать всеРеферат

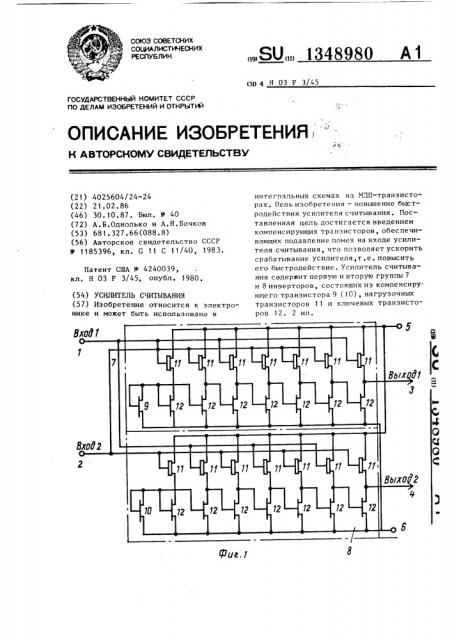

Изобретение относится к электронике и может быть использовано в интегральных схемах на ВДП-транзисторах. Цель изобретения - повьпиение быстродействия усилителя считывания. Поставленная цель достигается введением компенсирующих транзисторов, обеспечивающих подавление помех на входе усилителя считывания, что позволяет ускорить срабатывание усилителя,т.е. повысить его быстродействие. Усилитель считывания содержит первую и вторую группы 7 и 8 инверторов, состоящих из компенсирующего транзистора 9 (10) , нагрузочных транзисторов 1 1 и ключевых транзисторов 12. 2 ил. Bxodf о 7 У„ ы„ LJ,, ы„ ы, ы„ Ц ТО - 72 - 72 - ;2 - ;2 1 т 1 1 Bxoff2 о 2 Ц1 77Ц7/Ц1 //Ц;;Ы;;Ц;Ы;; 05 11 Вых, / с 72 Ч;2 ;Ы;; с 4 О с: о с //Ц;;Ы;;Ц;Ы;; -I п п п 12 L-Г;2Н-;2 1 1 т л Выхода i Фие.1 -I- 8

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (50 4 Н 03 F 3/45

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

0

0 ()

Ю фце.!

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4025604/24-24 (22) 21.02.86 (46) 30, 10. 87. Бюл. У 40 (72) А,Б ° Однолько и A.Н.Бочков (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

У 1185396, кл. С 11 С 11/40, 1983.

Патент США М 4240039, кл. Н 03 F 3/45, опубл. 1980. (54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ (57) Изобретение относится к электро" нике и может быть использовано в

„„SU„„1348980 А1 интегральных схемах на МЛП-транзисторах, Цель изобретения — повышение быстродействия усилителя считывания ° Поставленная цель достигается введением компенсирующих транзисторов, обеспечивающих подавление помех на входе усилителя считывания, что позволяет ускорить срабатывание усилителя,т.е. повысить его быстродействие. Усилитель считывания содержит первую и вторую группы 7 и 8 инэерторов, состоящих иэ компенсиру. ющего транзистора 9 (10), нагрузочных транзисторов 11 и ключевых транзисторов 12. 2 ил.

1348980

Изобретение относится к электро;-;нике и может быть использовано н

>!> 1Tcгральных схемах на МДП-транзисто1!ель изобретения — повышение быст:> дейетнпя усилителя считывания.

На фиг. 1 представлена схема предлагаемы.1 о усилителя считывания; на фиг. 2 — выходная характеристика усии:1теля считывания.

Уси;1итель считывания содержит первый и нторой информационные входы и 2, первый и нторой информационные выходы 3 и 4, шины 5 и 6 питания нулевого потенциала, первую и вторую группы 7 и 8 инверторов, первый

?и ?й компенсирующие элементы 9 и t0 Н1 транзисторах, нагрузочные

Tp1н111сторы 11, ключевые транзисторы 12.

Ирп нулевом выходном дифференциальном с11гн(1ле на первом и втором информационных выходах низкий уровень. Прп достижении некоторого уровня сигнала, определяемого величиной

»3 ift-;t нуля, н1пряжепие одного из

iiii 3>ормационных выходов, определяемое

11 ? !1(I Ðil(? СТЬЮ ВХОДНОГО CIIÃНаЛ<1 c!iii??<1.: ??? c:i??>f;Iå ве:и!чин;l ныходн Огo clfi 111:1а определяется коэффициентом ! 0»> f>ftftftett T усиления Опрелс чяеT(. .я количеством инверторов н ,ЦЕПОЧКЕ.

В пнтегральн1,1х схемах памяти у(.п..п1те11. считывания должен иметь и;iKcff>t 1.(ьпую чувствительность к вход!

О.fy с;11 tf,131у для улучшения основного параметра — времени выборки. Однако, 3T(? Tpo!>ot3<1hfte ???????????????????????? ??????????1 1i> НО, it;IC;1KO!!!ЕМУС11 ПОМЕХОУС Toit>litt>Oсти, и(?скол!,ку помехи на входе уси >- >!1<1 е ня 3:ltt!11!е Г р 16ОТ011 !пl Т(. Г ральной схемы, усиливаются и проходят и» I3ttK(?д усп и!те.1я. 10щные выходные

K 1 0 K <1 ITIgttOII C lf K II <1JI усилителя и создают тем самь1м дополнительные помехи. Т.е. интегральная схема памяти с высокочувствительным уcffJIIITC лем с 111111!3анпя может войти 13 режим генерации по выходу и только пр 1 достижеtilllt H i входе усилителя

>шформационного сигнала, превыша>ощегo, !"? . Гlii. 11? f0õ !f1 выходе интегральной схемы, получасi f истинное значен11е вы>Е" > If 11> (?P .i<11(flit. ПОЭТОМy С Ilt .!Ь!О предотвращения генерации по выходу

»,>1>пппент усltflc flfftf усилителя считы.:.1н>ш (огр1ничпв;пот так, чтобы усиливаемые помехи не проходили на ныход интегральной схемы.

Характерные точки: а — рабочий

5 уровень выходного сигнала усилителя; в — допустимый уровень помех на выходе усилителя, т.е. уровень сигнала, который не проходит на выход интегральной схемы; с — уровень помех на нходе усилителя (фиг. 2).

Из передаточной характеристики видно, что н случае линейного усилителя максимальная чувствительность ограничена отношением допустимого уровня помех на ныходе к уровню помех на входе. Б предлагаемом устройстве передаточная характеристика нелинейна, что создает возможность полностью исклю-пить усиление помех на

76 входе усилителя. Для рабочего входного сигнала, пренышающего уровень помех по входу, коэффициент усиления гораздо больше, чем в схеме прототипа. Таким образом, н предлагаемом

7(устройстве рабочий уровень выходного сигнала достигается при гораздо меньшем входном си! 13131е, т. е, коэффициент усиления увеличен. формула изобретения

Ус и пител ь c>lii T»tli<11t»H, соде ржащий первую группу иннерторон, каждый иэ которых состоит из нагруэочного и

KJIfo>IeI3oro t plfftaftc Topof3, причем стоки

35 нагрузочных транзисторов Объединены и подключены к шине питания усилителя, затворы нечет!!ых нагруз(эчн!1х

Tp<1h 3 11c???? ????!3 (?61>е;! 1111 с ltы H Н13ЛЯЮТC ß первым инф(эрмациoнным входом усили1(! те I>I с п(TI>113;! I!>fя затворы четных нагрузочных транзисторов объединены и янляются вторым информационшом входом усилителя c«1111ра пс рво!1 группы соед!шены, затвор и сток Këþ÷åâîãо транзистора первого инвертора первой группы Объе;пше «ы, затвор клк>чевого трап 3ifc Top;1 каждого 1шнертора первой

50 группы, кроме первого, соединен со стоком к:воченого транзистора предыду< щего ин13ертRp;1 lit. .pf3ой группы, сток по слепне гÎ клк? >1с н О г0 транзистора ян.>1яется инф(эрмапионным выходом усили55, теля счпт 1135ftfttt, истоки ключевых транзисторов oбъедиHåны и подкл3очены к шине нуленаг(э п(этенциала ус!3лителя, о т л и r cI io lt и с я тем, что, с

1 348980

/7P0/77gmun

Ыгих г6цг. Z

Сост- чите и 1< tycg

Гехрс;: 1I.Олийнык Корректор О. Кравцова

Редактор I. Ларфс нова Заказ 5199/56

1 и - -оt, 8 9 9 Корректор С.Черни

ВНИИПИ государстве сного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раупская наб., д. 4/5

Производственно-полиграфическос= предприятие, г. Ужгород, кл. Проектная, 4 целью повышения быстродействия усилителя считывания, в него введены вторая группа ипверторов, первый и второй компенсирующие элементы на с, транзисторах, причем каждьп1 иннертор второй группы состоит из нагрузочного и ключевого транзисторов, исток нагрузочного и сток ключевого транзисторов инверторов второй группы соедине- 1п ны, стоки нагрузочных транзисторов инверторов второй группы объединены и подключены к .пине питания усипителя, затворы нечетных и четных нагруэочных транзисторов инверторов второй группы подключены соответственно к второму и первому информационным входам усилителя считывания, затвор и исток ключевого транзистора первого инвертора второй группы объединены, сток и затвор соответствующего тран-, зистора компенсирующего элемента подключены к затвору первого ключевого транзистора, сток последнего ключевого транзистора инвертора второй группы является вторым информационным выходом усилителя считывания.