Транзисторный ключ с защитой от перегрузки

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в регуляторах напряжения, преобразователях частоты, инверторах тока и напряжения. Целью изобретения является повьпмение надежности. Транзисторный ключ содержит блок 1 управления , блок 2 сравнения, делители напряжения: первый на резисторах 3 и 4, второй на резисторах 6 и 7, третий на резисторах 8 и 9 элемент совпадения 10, выполненный на транзиса 21 торах 35 и 36, силовой составной транзистор 16, источник 17 питания, шины 18 и 19 питания, входные клеммы 20 и 21, входы 22 и 23, выход 24 и компаратор 34 блока сравнения, резисторы и конденсаторы, показанные на схеме. Блок управления (схема приводится в описании изобретения) обладает равными постоянными времени заряда и разряда конденсатора, что приводит к различным задержкам отпирания и запирания транзистора 16. Это позволяет при использовании устройства в мостовых и полумостовых схемах управлять ключом одним управляющим сигналом. Технико-экономические преимущества устройства, по сравнению с прототипом, заключаются в повышении надежности работы транзисторного ключа с защитой от перегрузки , что достигается за счет устранения ложных переключений транзистора 16 от действия импульсных помех на управляющем входе и по цепи коллектора транзистора. 2 з.п. ф-лы, 2 ил. i (Л со 00 со QO 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1348993 A 1 (50 4 Н 03 К 17/60

ОПИСАНИЕ ИЗОБРЕТЕНИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4046588/24-21 (22) 31.03.86 (46) 30.10.87. Бюл. Ф 40 (72) Н.A. Иванов, A.Н, Пискарев, В.А. Синицын и В.С. Томасов (53) 621.382(088,8) (56) Авторское свидетельство СССР

Ф 438144, кл. Н 03 К 17/60, 1974.

Авторское свидетельство СССР

У 1003344, кл. Н 03 К 17/60, 1981. (54) ТРАНЗИСТОРНЫЙ КЛЮЧ С ЗАЩИТОЙ

ОТ ПЕРЕГРУЗКИ (57) Изобретение относится к импульсной технике и может быть использовано в регуляторах напряжения, преобразователях частоты, инверторах тока и напряжения. Целью изобретения является повышение надежности. Транзисторный ключ содержит блок 1 управления, блок 2 сравнения, делители напряжения: первый на резисторах 3 и 4, второй на резисторах 6 и 7, третий на резисторах 8 и 9, элемент совпадения 10, выполненный на транэисторах 35 и 36, силовой составной транзистор 16, источник 17 питания, шины 18 и 19 питания, входные клеммы

20 и 21, входы 22 и 23, выход 24 и компаратор 34 блока сравнения, резисторы и конденсаторы, показанные на схеме. Блок управления (схема приводится в описании изобретения) обладает равными постоянными времени заряда и разряда конденсатора, что приводит к различным задержкам отпирания и эапирания транзистора 16. Это позволяет при использовании устройства в мостовых и полумостовых схемах управлять ключом одним управляющим сигналом. Технико-экономические преимущества устройства, по сравнению с прототипом, заключаются в повышении надежности работы транзисторного ключа с защитой от перегрузки, что достигается за счет устранения ложных переключений транзистора

16 от действия импульсных помех на управляющем входе и по цепи коллектора транзистора. 2 з.п, ф-лы, 2 ил.

1348993

Изобретение относится к импульсной технике, импользуется преимущественно> в регуляторах напряжения, преобразователях частоты, инверторах тока и напряжения в качестве импульсных усилителей.

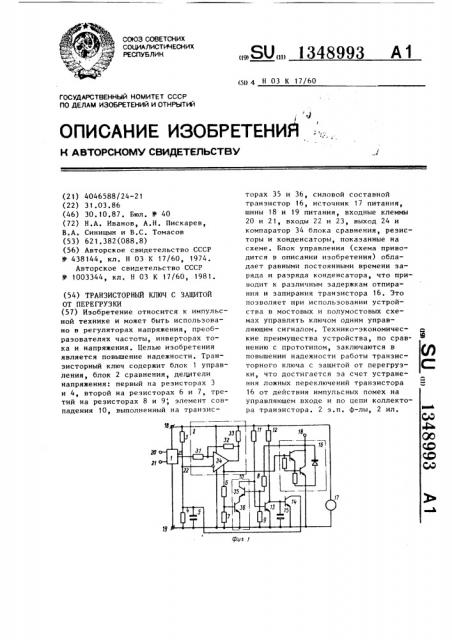

Цель изобретения — повышение надежности, На фиг. 1 представлена электричес- О

45 кая схема транзисторного ключа с защитой от перегрузки, на фиг, 2 — схема блока управления, Транзисторный ключ с защитой от перегрузки содержит блок 1 упрагления, блок 2 сравнения, первый делитель. напряжения на резисторах 3 и 4, выходной резистор 4 которого шунтирован первым конденсатором 5, второй делитель напряжения на резисторах ?0

6 и 7, третий делитель напряжения на резисторах 8 и 9, элемент 10 совпадения, выполненный на первом и втором транзисторах, первый 11 и второй

12 резисторы, третий 13 и четвертый

14 транзисторы, второй конденсатор

15, силовой составной транзистор 16, источник 17 питания, первую 18 и вторую 19 шины питания, первую 20 и вторую 21 входные клеммы устройства, а 30 также первый 22 и второй 23 входы и выход 24 блока 2 сравнения. Вход 23 одновременно является выходом блока

1 управления.

Первые выводы первого и третьего резисторных делителя напряжения подключены к первой шине 18 питания, вторые выводы которых подсоединены к второй шине 19 питания, средняя точка первого резисторного делителя напряжения через первый конденсатор

5 подключена к второй шине 19 питания, коллектору четвертого транзистора 14 и первому входу 22 блока 2 сравнения, второй вход 23 которого соединен с выходной клеммой блока 1 управления> выход 24 блока сравнения подключен к первому выводу второго резисторного делителя напряжения и к базе силового составного транзисто50 ра 16, эмиттер которого подсоединен к второй шине 19 питания> а коллектор — к первому выводу третьего резнсторпого делителя напряжения, эмиттеры третьего 13 и четвертого 14 транзисторов подключены к второй шине 19 питания, база третьего транзистора 13 через первый резистор

11 подключена к первой шине 18 питания, а коллектор через второй резистор 12 — к первой шине 18 питания, базе четвертого транзистора 14 и через второй конденсатор 15 к второй шине 19 питания, второй вывод второго реэисторного делителя напряжения подключен к второй шине 19 питания.

Блок 1 управления содержит оптрон

25, третий 26, четвертый 27 и пятый

28 резисторы, третий конденсатор 29 и пятый транзистор 30. Светодиод оптрона 25 подключен к входным клеммам 20 и 21 устройства, анод фотодиода оптрона 25 подключен к второй шине 19 питания, катод фотодиода оптрона 25 подключен через третий резистор 26 к первой шине 18 питания и непосредственно к базе пятого транзистора 30> эмиттер которого через четвертый реэистр 27, зашунтированный третьим конденсатором 29, подключен к второй шине 19 питания и через пятый резистор 28 к первой шине

18 питания ц непосредственно к выходу 23 блока 1, а коллектор подключен к первой шине 18 питания.

Блок 2 сравнения содержит шестой

31, седьмой 32 и восьмой 33 резисторы и компаратор 34 напряжения, который включен между шинами питания.

Неинвертирующий вход компаратора 34 через шестой резистор 31 подключен к второму входу блока 2 сравнения, инвертирующий вход компаратора 34 подключен к первому входу 22 блока 2 сравнения, первый выход компаратора

34 через седьмой резистор 32 соединен с неинвертирующим входом компаратора и через восьмой резистор 33 подключен к первой шине 18 питания, а второй выход компаратора 34 подключен к выходу 24 блока 2 сравнения.

Элемент 10 совпадения содержит первый 35 и второй 36 транзисторы.

База первого транзистора 35 подсоединена к средней точке третьего реэисторного делителя напряжения на резисторах 8 и 9, подключенного

I параллельно переходу эмиттер-коллектор силового составного транзистора

16. Коллектор первого транзистора

35 через первый резистор 11 подключен к первой шине 18 питания. Эмиттер первого транзистора 35 через коллекторно-эмиттерный переход второго транзистора 36 соединен с второй шиной 19 питания. База второго транэис1348993 тора 36 подключена к средней точке второго реэисторного делителя напряжения на резисторах 6 и 7.

Устройство работает следующим образом.

В нормальном режиме входной сигнал через блок управления подается на неиннертирующий вход компаратора

34 и далее, сформированный и усиленный по мощности последним, поступает на базу силового составного транзистора 16, управляя его работой.

При этом напряжение между коллектором и эмиттером силового составного транзистора 16 падает, первый транзистор 35 элемента 10 совпадения заперт, третий транзистор 13 открыт, четвертый транзистор 14 заперт и потенциал инвертирующего входа компаратора 34 определяется только соотношением плеч первого резисторного делителя напряжения на резисторах

3 и 4 °

Блок 1 управления обладает разными постоянными времени заряд« и ра 3 ряда конденсатора 29, что н конечном счете приводит к различным задержкам на отпирание, „„ и запирание

t д „ силового составного транзистора 16, причем задержка на отпирание превышает задержку нг его запиргние.

Зто позволяет при использовании устройства в мостовых в полумостовых схемах управлять ключами одним управляющим сигналом при встречно-п«раллельном включении светодиодов оптрона 25. При этом сначала происходит выключение ранее работавшего силового составного транзистора 16 одного ключа и только спустя время

t -t включение смежного о.д очи с д yon с ним второго ключа. Тем самым исключаются режимы скнозных токов через два последовательно включенных силовых составных транзистора. Кроме того, задержка на включении силового составного транзистора 16 делает схему выходного каскада более помехоустойчивой, поскольку кратковременные импульсы помехи с выхода оптрона 25 не приводят к отпиранию силового составного транзистора 16 °

Величина времени задержки определяется типом применяемых силовых транзисторов и может задаваться выбором величины емкости конденсатора 9.

5

При внешнем коротком замыкании н«пряжение между коллектором и эмиттером силового составного транзистора 16 остается высоким постоянно и не зависит от поданаемого на него сигнала управления. Зто обстоятельство при наличии отпирающего сигнала на базе силового составного транзистора 16 приводит к одновременному отпиранию первого второго транзисторов 35 и 36 элемента 10 совпадения, эгпиранию третьего транзистора 13, а спустя некоторое время, определяемое постоянной времени цепи;резистор

12 — конденсатор 15, и к отпиранию четнертого транзистора 14. При этом потенциал инвертирующего входа компар«тора 34 быстро уменьшается (эа время С ) до уровня, при котором компаратор отключается, и снимается отпирающий сигнал с базы силового составного транзистора 16, в результ«те чего последний запирается независимо от сигнала управления, В этот же момент времени второй 14 и четвертый 36 транзисторы также закрываются. Однако за счет гистерезиса компаратора 34 его включение и подача отпирающего сигнала на базу силового составного транзистора 16 возможны лишь спустя время t„, эа которое напряжение на первом конденсаторе 5 нарастает до уровня переключения компаратора 34.

Если срабатывание защиты было вызвано не одиночным импульсом помехи, а внешним к.з °, то после включения силового составного транзистора опис«нные процессы вновь повторяются, в схеме устанавливается автоколебателbный режим, при котором силовой составной транзистор 16 на коротком интервале (t„ - =1-3 мкс) находится в активной области, а остальное время (t = 0,5-2 мс) заперт. Зффективное значение тока коллектора из-за большой скнажности импульсон невелико, поэтому работа в таком режиме, хотя и тяжелом для силового прибора, к отказу силового составного транзистора

16 не приводит.

Времена t., и г„ могут задаваться практически независимо одно от другого соответствующим выбором емкостей конденсаторов 5 и 15.

Увеличение надежности работы транзисторного ключа с защитой от перегрузки достигается зг счет устранения на управляющем входе и по цепи коллектора силового транзистора. формула и э о б р е т е н и я

1. Транзисторый ключ с защитой от перегрузки, содержащий блок управления, блок сравнения, три реэисторных делителя напряжения, элемент совпадения на первом и втором транзисторах, первый конденсатор и силовой состанной транзистор, первые выводы первого и третьего реэисторных делителей напряжения подключены к первой шине питакия, вторые выводы второго и тоетьего резисторных делителей напряжекия подключены к второй шине питания, база первого транзистора подключена к средней точке третьего резисторного делителя напряжекия, а эмиттер через коллекторко-эмиттерный 25 переход второго тракзистора подключен к второй шине питания, база второго транзистора подключека к средней точке нторого реэисторного делителя напряжения, средняя точка первого резисторного делителя напряжения через первый конденсатор подключсна к второй ш11ке питания, эмиттер силового составного транзистора подключен к второй шине питания, а коллектор — к

35 второму выводу третьего резисторного делителя напряжения, блок управления включен между первой и второй шинами питания, вход блока управления подключен к входным клеммам устройства, 40 отличающийся тем, что, с целью повышения надежности, введены

ПЕР11Ый 11 В ГОРОЙ РЕвиетОРЫ, ВтОРОй конденсатор, гретпй и четвертый транзисторы, эмиттеры которых подключены

45 к второй шине питания, база третьего транзистора подк11юче11а к коллектору первого тракз1,ст,>ра 11 через первый резистор — к первой шине питания, коллектор третьего транзистора под50

5 134899 ложных переключений силового транзистора от действия импульсной помехи

6 ключен к базе четвертого транзистора, через второй резистор к первой шине питания и через второй конденсатор к второй шине питания, второй вывод первого резисторного делителя напряжения подключен к второй шине питания, а средняя точка подключена к коллектору четвертого транзистора и первому входу блока сравнения, второй вход которого подключен к выходу блока управления, а выход — к первому выводу второго резисторного делителя напряжения и к базе силового составного транзистора, 2. Транзисторный ключ по и. 1, отличающийся тем, что блок управления содержит оптрон, третий, четвертый и, пятый резисторы, третий конденсатор, пятый транзистор, светодиод оптрона подключен к входным клеммам устройства, анод фотодиода оптрона подключен к второй шине питания, а катод через третий резистор к перной шине питания и непосредственно к базе пятого транзистора, эмиттер которого через четнертый резистор, зашунтированный третьим конденсатором, подключен к второй шине питания, через пятый резистор к первой шине питания и непосредственно к выходу блока управления, а коллектор подключен к первой шине питания.

3. Транзисторный ключ по и. 1, отличающийся тем, что блок сравнения содержит шестой, седьмой и восьмой резисторы и компаратор напряжения, который включен между шинами питания, иннертирующий вход которого подключен к первому входу блока сравнения, кеинвертирующий вход компаратора через шестой резистор подключен к второму входу блока сравнения, первый выход компаратора через седьмой резистор соединен с его неиквертирующим входом и через восьмой резистор подключен к первой шине питания, а второй выход компаратора подключе н к выходной клемме блока сравнения.

1348993

21

Составитель Г.Терешина

Редактор Л.Пчолинская Техред Л.Олийнык Корректор Н.Король

Заказ 5199/56 Тираж 899 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4