Дискретный фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к области электротехники и может быть использовано в устройствах, обеспечивающих высокое быстродействие передачи сигнала обратной связи. Цель изобретения - улучшение эффективности путем повышения точности передачи входного сигнала. Сигнал с входного вывода 10 поступает на входы интеграторов 1, 2. Путем поочередного переключения ключей сброса 8, 9 происходит передача сигнала с выхода соответствующего интегратора 1,2 через ключи передачи 5-7 и запоминающие блоки 3, 4 на выходной вывод 11. В результате обеспечивается поступление на выходной вывод 11 сигнала о конечном значении интеграла от входного сигнала на заданном интервале интегрирования , а не текущее значение этого сигнала , приближающееся к конечному. Такой режим работы позволяет исключить пульсации выходного сигнала. 2 ил.. . с € (Л 6bfX. ОО сл о 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„135078

А1 (51) 4 Н 02 M 1/14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н Д BT0PCHOMV СВИДЕТЕЛЬСТВУ

»

".. »

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3965726/24-07 (22) 16.10.85 (46) 07..11.87. Бюл. ¹ 41 (71) Новосибирский электротехнический институт (72) M.À. Алейников, С.И. Гулевский, В.В. Климовицкая и С.Л, Рояк (53) 621. 314. 5 (088. 8) (56) Авторское свидетельство СССР № 490235, кл. Н 02 M 1/08, 1973.

Авторское свидетельство СССР № 955423, кл. H 02 М 1/14, 1982. (54) ДИСКРЕТНЫЙ ФИЛЬТР (57) Изобретение относится к области электротехники и может быть использовано в устройствах, обеспечивающих высокое быстродействие передачи сигнала обратной связи. Цель изобретения — улучшение эффективности путем повышения точности передачи входного сигнала. Сигнал с входного вывода 10 поступает на входы интеграторов 1, 2.

Путем поочередного переключения ключей сброса 8, 9 происходит передача сигнала с выхода соответствующего интегратора 1,2 через ключи передачи

5-7 и запоминающие блоки 3, 4 на выходной вывод 11. В результате обеспечивается поступление на выходной вывод 11 сигнала о конечном значении интеграла от входного сигнала на заданном интервале интегрирования, а не текущее значение этого сигнала, приближающееся к конечному.

Такой режим работы позволяет исключить пульсации выходного сигнала.

2 ип.!

3507

Изобретение относится к электротехнике и может быть использовано для сглаживания пульсаций выпрямленного напряжения в устройствах, обес5 печивающих высокое быстродействие передачи сигнала обратной связи в системе автоматического регулирования.

Цель изобретения — улучшение эффективности путем повышения точности передачи входного сигнала.

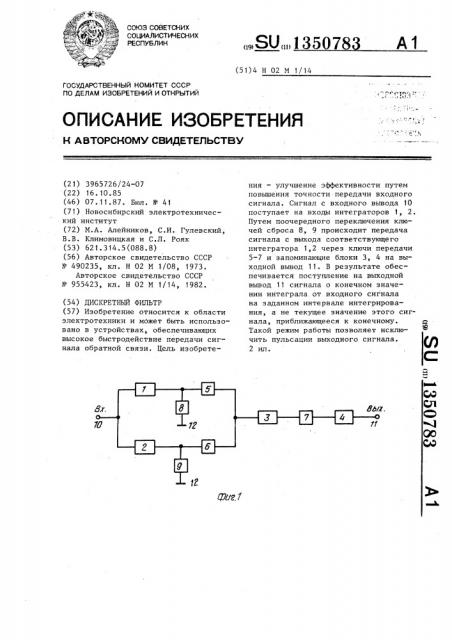

На фиг. 1 представлена функциональная схема устройства; на фиг.2 временные диаграммы напряжений 0 на соответствующих элементах устройства, поясняющие работу устройства (указанные цифровые обозначения соответствуют номерам используемых элементов в устройстве).

Дискретный фильтр (фиг.,1) содержит интеграторы 1 и 2, запоминающие блоки 3 и 4, ключи 5-7 передачи, ключи 8,, 9 сброса, а также входной

10, выходной 11 и общий t2 выводы.

Входной вывод 10 подключен к вхо- 2В дам интеграторов 1,2. Выход интегратора 1 подключен через ключ 8 сброса и ключ 5 передачи к общему выводу 12 и к входу запоминающего блока 3. Выход интегратора 2 поцключен через ключ 9 сброса и ключ б передачи к общему выводу 12 и к входу запоминающего блока 3, вь|ход которого через ключ 7 передачи подключен к входу запоминающего блока 4, выходом подключенным к выходному выводу 11.

Интеграторы 1, 2 с ключами 8, 9 сброса могут быть выполнены на операционных усилителях. Запоминающие блоки 3 и 4 и ключи 5-7 передачи могут быть выполнены на операционных усилителях и полевых транзисторах.

Устрсйство работает следующим образом.

Входной с.игнал поступает с вывода 10 на вхсды интеграторов 1 и 2.

В момент времени t (фиг. 2) закончены процесс интегрирования входного сигнала интегратором 2 и занесение сигнала с выхода интегратора 2 в заБО поминающий блок 3 через ключ б передачи. В интервале (t,-t ) замыкается ключ 9 сброса (логическое состояние "1" на диаграммах фиг. 2 соответствует замкнутому состоянию ключа), 55 приводя интегратор 2 к нулевым начальным условиям, и размыкается ключ

8 сброса, при этом сигнал с входа 10 воспринимается интегратором !. В ин83

2 тервале времени (t, — t ) замкнут ключ

? передачи и сигнал с выхода запоминающего блока 3 через ключ 7 передачи заносится в запоминающий блок 4, с выхода которого поступает на выходной вывод 11. В интервале времени (t — tz) замыкается ключ 5 передачи и информация о входном сигнале в процессе его интегрирования с выхода интегратора 1 заносится в запоминающий блок 3. Выходной сигнал запоминающего блока 3 имеет пульсации с периодом, равным половине периода работы устройства, так как выходной сигнал интегратора 1 достигает конечного значения в момент времени t a занесение его в эапоминаюший блок начинается в момент t . Затем в момент времени t размыкается ключ 5 передав чи, замыкаются ключ 8 сброса до приводя интегратор !к нулевым начальным условиям, и ключ 7 передачи до передающий занесенную в запоминающий блок 3 информацию о входном сигнале в запоминающий блок 4. Сигнал с выходного вывода 11 не содержит пульсации, так как в загоминающий блок 4 поступает конечное значение сигнала с выхода интегратора 1 через запоминающий блок 3, В тот же момент времени t, размыкается ключ 9 сброса до и интегратор 2 начинает воспри1 нимать сигнал с входного вывода 10.

В интервале (с -г. ) замыкается ключ б передачи и происходит занесение информации с вьгхода интегратора 2 в запоминающий блок 3. В момент времени замыкаются ключ 9 сброса, приводя интегратор 2 к нулевым начальным условиям, и ключ 7 передачи до t, через который происходит занесение информации с выхода запоминающего блока 3 в запоминающий блок 4 и с выхода запоминающего блока 4 на выходной вывод 11. В этот момент времени остальные. ключи разомкнуты. Далее описанный процесс повторяется.

Таким образом, на выходной вывод устройства поступает сигнал о конечном значении интеграла от входного сигнала на заданном интервале интег= рирования, а не текущее значение этого сигнала, приближающееся к конечному. Благодаря этому повьш ается точность передачи сигнала дискретным фильтром путем исключения пульсаций выходного сигнала.

783

8ы о r р j4, 5 Б 7

Щ/е 2

Составитель А. Кириллов

РедактоР Н. ГУнько ТехРеД М. оданич Корректор Л. Пилипенко

Заказ 5294/54 Тираж 659 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

3 1350

Формула и з о б р е т е н и я

Дискретный фильтр, содержащий входной, выходной и общий выводы для подключения соответственно ис-. точника входного напряжения и цепи

5 нагрузки, два интегратора, два ключа сброса, два ключа передачи и запоминающий блок, причем входы интеграторов объединены и соединены с

10 входным выводом, выход первого интегратора через первый ключ сброса и первый ключ передачи соединен соот ветственно с общим выводом и входом запоминающего блока, а выход второго интегратора через второй ключ сброса и второй ключ передачи соединен соответственно с общий выводом и входом запоминающего блока, о т л и ч а ю шийся тем, что, с целью улучшения эффективности путем повышения точности передачи входного сигнала, дополнительно введены третий ключ передачи и второй запоминающий блок, вход которого через указанный третий ключ передачи соединен с выходом основного запоминающего блока, а его выход соединен с выходным выводом.