Усилительное устройство

Иллюстрации

Показать всеРеферат

Изобретение может использовать-- ся при построении аналоговых и аналого-цифровых схем на МДП-транзисторах и обеспечивает компенсацию смещения нулевого уровня постоянного напряжения . Усилительное устр-во содержит дифференциальный каскад (ДК), вьшолненный на транзисторах (Т) 2, 3, отражатель тока, выполненный на Т 4, 5, резисторы 7, 8, конденсатор компенсации 9, выходной усилительный каскад 10, управляющие ключи. (УК ) 11-17, конденсатор 18, компаратор 19, инверторы 20, 21, эл-т И 22 и эл-т ИЛИ 23. Цикл измерения включает время компенсации и время измерения. УК открьшаются высоким уровнем напряжения . При подаче установочного импульса положит, полярности начинается компенсация. При этом открываются УК 12, 13, 15. Конденсатор 18 разряжается через УК 12, в результате чего в плечах ДК появляется разбаланс, переключающий выход компаратора 19 на уровень напряжения положит, полярности . При поступлении сигнала отриц. полярности УК 12 закрьшается, а УК 1I открьшается и через него заряжается конденсатор 18. Когда разбаланс в плечах ДК меняет знак, то на выходе компаратора 19 появляется сигнал отриц. полярности. При этом УК 12 закрыт, закрываются УК П, 13, 15 и через инвертор 21 открываются УК 14, 16, 17. Начин ается режим измерения , который по времени намного больше режима компенсации. 1 ил. (Л оо ел о оо го Ic Вых.

СОЮЗ СОВЕТСНИХ

СО!.1ИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (ц 4 Н 03 F 3/45

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABT0PCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4023962/24-09 (22) 17.02.86 (46) 07,11.87, Бюл. У 41 (72) В.Н.Богатырев и З.M.Ïîâàðíèöüiíà (53) 621.375.024(088.8) (56) Электроника, 198!, и 38. (54) УСИЛИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение может использоваться при построении аналоговых и аналого-цифровых схем на ИДП-транзисторах и обеспечивает компенсацию смещения нулевого уровня постоянного напряжения. Усилительное устр-во содержит дифференциальный каскад (ДК), выполненный на транзисторах (Т) 2, 3, отражатель тока, выполненный на Т 4, 5, резисторы 7, 8, конденсатор компенсации 9, выходной усилительный каскад

10, управляющие ключк (УК 1 11-17, конденсатор 18, компаратор 19, инверторы 20, 21, эл-т И 22 и эл-т

ИЛИ 23. Цикл измерения включает вре„„SU„„1350821 А1 мя компенсации и время измерения. УК открываются высоким уровнем напряжения. При подаче установочного импульса положит, полярности начинается компенсация. При этом открываются

УК 12, 13, 15. Конденсатор 18 разряжается через УК 12, в результате чего в плечах ДК появляется разбаланс, переключающий выход компаратора 19 на уровень напряжения положит, полярности. При поступлении сигнала отриц. полярности УК 12 закрывается, а УК 11 открывается и через него .заряжается конденсатор 18. Когда разбаланс в плечах ДК меняет знак, то на выходе компаратора 19 появляется сигнал отриц. полярности. При этом

УК 12 закрыт, закрываются УК 11, 13, l5 и через инвертор 21 открываются

УК 14, 16, 17. Начинается режим измерения, который по времени намного больше режима компенсации. 1 ил.

1350821

Изобретение относится к усилительным устройствам и может быть использовано при построении аналоговых и аналого-цифровых схем на МДП-транзисторах.

Цель изобретения — компенсация смещения нулевого уровня постоянного напряжения.

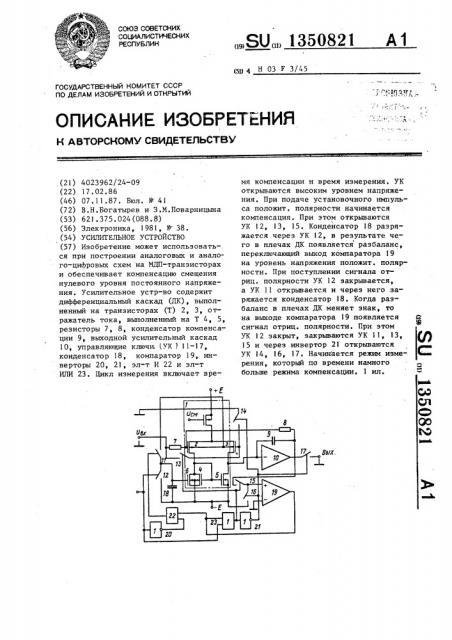

На чертеже представлена электрическая принципиальная схема предложенного усилительного устройства.

Усилительное устройство содержит дифференциальный каскад i первый, второй, третий, четвертый, пятый транзисторы 2 — 6 первый, второй резисторы 7, 8, конденсатор 9 компенсации, выходной усилительный каскад 10, первый, второй, третий, четвертьп1, пятый, шестой и-седьмой управляемые ключи 11 — 17, конденсатор

18, компаратор 19, первый и второй инверторы 20, 21, элемент И 22, элемент ИЛИ 23, третий и четвертый транзисторы образуют отражатель тока.

Усилительное устройство работает следующим образом °

Цикл измерения включает в себя время компенсации и время измерения.

Все ключи в схеме открываются высоким уровнем .напряжения. В исходном сос.тоянии на вход тактовых импульсов подается установочный импульс положительной полярности, начинающий время компенсации.При этом открывается второй управляемый ключ 12. Напряжение положительной полярности на выходе элемента ИЛИ 23 открывает третий и пятый управляемые ключи 13 и 15. При этом первый 11, шестой 16, четвертый

14, седьмой 17 управляемые ключи закрыты. Конденсатор 18 разряжается через открытый второй 12 управляемый ключ. Ширина канала третьего транзистора 4 выбирается меньшей ширины канала четвертого транзистора 5, проводимость соответственно меньше. Подключаемый параллельно резистор 7 позволяет менять напряжение смещения нуля изменением напряжения на его затворе с коэффициентом 1115 05

К=- — — — Ъ 15 0 Бы)

Ko.о.c для операционного усилителя в режиме повторителя при соотношении

4W,=15 М, K=4,6, rpe W — ширина канала. При увеличении отношения ,W /W < увеличивается коэффициент К.

4О

При разрядке конденсатора 18 уменьшается проводимость резистора 7, в плечах дифференциального каскада появляется разбаланс, переключающий выход компаратора 19 на уровень напряжения положительной полярности. При поступлении на вход тактовых импульсов сигнала отрицательной полярности закрывается второй ключ 12. Пятый 15, третий 13 остаются открытыми и уровнем напряжения положительной полярности на выходе элемента И 22 открывается первый ключ 11. Ключи четвертый 14, шестой 16, седьмой 17 закрыты. Конденсатор 18 заряжается через открытый первый ключ 11. Когда разбаланс в плечах дифференциального каскада меняет знак, то на выходе компаратора 19 появляется сигнал отрицательной полярности. При этом закрываются первый 11, третий 13, пятый

15 ключи. Ключ второй 12 остается закрытым, а сигнал положительной полярности на выходе второго инвертора

21 открывает четвертый 14, шестой 16, седьмой 17 ключи. Начинается режим измерения. На выходе компаратора 19 сигнал отрицательной полярности устанавливается да следующей компенсации. Чувствительность компаратора должна быть не хуже (t. с,..р,ц К0., ñ )

Скважность тактовых импульсов может быть порядка 15, поскольку утечки на конденсаторе 18 не критичны. В методах компенсации, основанных на запоминании напряжения смещения на емкости, скважность тактируемых импульсов выбирается в пределах от 2 до 5 из-за небольшого времени хранения за счет утечек.

Таким образом, в схеме обеспечивается время активной работы — вре .. мя измерения — намного большим времени компенсации.

Формулаизобретения

Усилительное устройства, выполненное на полевых транзисторах, содержащее последовательно соединенные дифференциальный каскад и усилительный каскад с конденсатором компенсации в цепи обратной связи, при этом дифференциальный каскад выполнен на первом и втором транзисторах, затвор первого транзистора является инвертирующим .входом дифференциального каскада и соединен с первым выводом пер50821

Составитель Н.Дубровская

Редактор С.Патрушева Техред И.Попович .Корректор Г,Решетник

Заказ 5297/56 Тираж 900 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4 з 13 вого. резистора, второй вывод которо-, го является входом усилительного устройства, а затвор второго транзисто-, ра является неинвертирующим входом дифференциального каскада, сток riepвого транзистора соединен с входом, а сток второго транзистора — с выходом отражателя тока, выполненного на третьем и четвертом транзисторах, причем первый, второй транзисторы имеют одну структуру, а третий и четвертый транзисторы — другую структуру, о т л и ч а ю щ е е с я тем, что, с целью компенсации смещения нулевого уровня постоянного напряжения, введены первый, второй, третий, четвертый, пятый, шестой и седьмой управляемые ключи, элемент И1П1, элемент И, первый и второй инверторы, компаратор, конденсатор, пятый транзистор, структура которого соответствует структуре четвертого транзистора, при этом вход первого и вход второго управляемых ключей соединены с .соответствующими шинами источника питания, а выходы объединены и подключены к одному выводу конденсатора и затвору пятого транзистора, сток-исток которого подключен к сток-истоку третьего транзистора, а другой вывод конденсатора подключен к истоку пятого транзистора, между вторым выводом второг о резистора и неинвертирующим входом дифференциального.кас5 када включен третий управляемый ключ

t между неинвертирующим входом дифференциального каскада и общей шиной включен четвертый ключ, выход выходного усилительного каскада через пятый управляемый ключ соединен с неинвертирующим входом компаратора, который через шестой управляемый ключ соединен с истоком че-.вертого транзистора, выход выходного усилительного каскада соединен с входом седьмого ключа, выход которого является выходом усилительного устройства, вход управления второго ключа соединен с входом тактовых импульсов и через

20 последовательно соединенные элемент

ИЛИ и второй инвертор — с входами управления четвертым, шестым и седьмым управляемыми ключами, выход компаратора соединен с другим входом

25 элемента ИЛИ и через элемент И вЂ” с входом управления первого ключа, другой вход элемента И соединен с выходом первого инвертора, вход которого соединен с входом тактовых импульсов, 30 выход элемента ИЛИ соединен с входами управления третьего и пятого управляемых ключей,