Устройство для формирования дискретных частотных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к радиосвязи и обеспечивает повышение точности формирования. Устр-во содержит генератор 1 тактовых импульсов, модулятор 2, RS-триггер 3, элементы ИЛИ- НЕ 4, 6, двоичный счетчик 5, параллельный регистр 7, сумматоры 8-10 по модулю два, элементы И 11-13, коммутатор 14 и линии задержки 15, Для повышения точности введены элемент ИЛИ- НЕ 6, ЛЗ 15 и коммутатор 14. 1 ил. /4 ft t-awr., . (Л с 00 ел о 00 4

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУ БЛИН

44 А1

„,SU(IiI (д!! 4 Н 04 Ь 27/l2

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4035642/24-09 (22) 11. 03. 86 (46) 07. 11.87. Бюл. У 41 (72) В. Е. Борисиков (53 ) 62! . 394. 14(088. 8) (56) Авторское свидетельство СССР !! 1177910, кл. Н 03 М 5/00, 1984. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ДИСКРЕТНЫХ ЧАСТОТНЫХ СИГНАЛОВ (57) Изобретение относится к радиосвязи и обеспечивает повышение точности формирования. Устр-во содержит генератор 1 тактовых импульсов, модулятор 2, RS-триггер 3, элементы ИЛИНЕ 4, 6, двоичный счетчик 5, параллельный регистр 7, сумматоры 8-10 по модулю два, элементы И 11-13, коммутатор 14 и линии задержки 15. Для повышения точности введены элемент ИЛИНЕ 6, ЛЗ 15 и коммутатор 14. 1 ил.

1350844

Изобретение относится к радиосвязи и может быть использовано в радиотехнических системах.

Цель изобретения — повышение точности формирования.

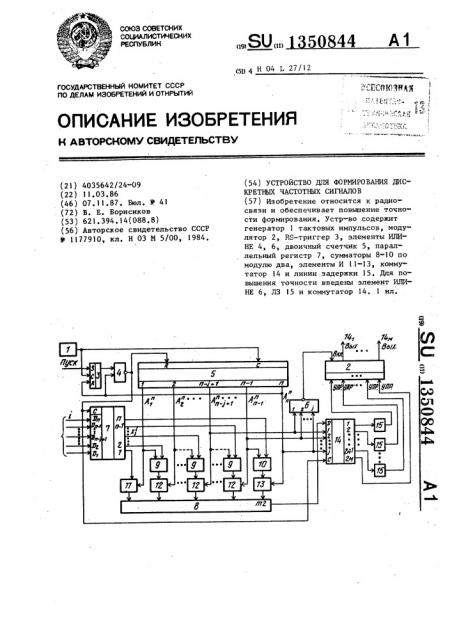

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство для формирования дискретных частотных сигналов содержит генератор 1 тактовых импульсов, модулятор 2, RS -триггер 3, первый элемент ИЛИ-НЕ 4, двоичный счетчик 5, второй элемент ИЛИ-НЕ 6, параллельный регистр 7, первый 8, второй 9 и третий 10 сумматоры по модулю два, первый 11, второй 12 и третий 13 элементы И, коммутатор 14, линии 15 задержки.

Устройство работает следующим образом.

В исходном состоянии RS-триггер 3 находится в нулевом состоянии, т.е. на выходе его потенциал логического нуля, Следовательно, на выходе элемента ИЛИ-НЕ 4 потенциал логической единицы, что обеспечивает исходное (нулевое) состояние двоичного счетчика 5 (т.е., на выходах всех его п разрядов потенциал логического нуля, несмотря на присутствие тактовых импульсов на счетном С-входе), запрет смены состояний разрядов параллельного регистра 7, так как на его тактовом С-входе потенциал логической единицы, выключенное состояние модулятора 2 и запрет на коммутацию информационного входа коммутатора 14 к любому из выходов и логический нуль на информационных, входах модулятора 2.

Так как на выходах двоичного счет1 чика 5 нулевые состояния, то на первом и втором входах управления коммутатора 14 также потенциалы логического нуля и на выходе сумматора 8 по модулю два — логический нуль.

При поступлении на пусковой вход устройства положительного импульса он стробируется генератором 1 тактовых импульсов и одновременно с фронтом тактового импульса RS-триггер 3. переходит в состояние логической единицы. Б этот момент времени на выходе элемента ИЛИ-НЕ 4 происходит смена состояния с логической единицы на логический нуль, что обеспечивает установку потенциала логического нуля с>

35 на R-вхоДе двоичного счетчика 5, запись в параллельный регистр 7 его входного состояния, подключение информационного входа коммутатора 14 к

его первому выходу и подключение через N-L тактов .модулятора 2.

Так как нулевой потенциал на Ввходе двоичного счетчика 5 является одновременно разрешающим счет, то с приходом очередного тактового импульса состояния двоичного счетчика 5 начинают меняться с частотой следования т- тактовых импульсов. Ровно через 2 тактов на третьем выходе двоичного счетчика 5 появляется потенциал логической единицы, который возвращает в исходное (нулевое) состояние RS-триггер 3. Но логический нуль на выходе элемента ИЛИ-НЕ 4 будет еще ровно

2 тактов. Таким образом, на выходе элемента ИЛИ-НЕ 4 нулевое состояние присутствует ровно 2 тактов от и момента стробирования пускового импульса. При появлении логического нуля на выходе и-го разряда двоичного счетчика 5 на входах элемента ИЛИ

НЕ 4 логические нули, что соответствует возврату устройства в исходное состояние.

Итак, от момента запуска устройст- ва, определяемого стробированием пускового импульса, двоичный счетчик

5 находится в динамическом (счетном) состоянии ровно 2 тактов работы reh нератора 1 тактовых импульсов, после чего автоматически устройство возвращается в исходное состояние.

Формула изобретения

Устройство для формирования дискретных частотных сигналов, содержащее модулятор, генератор тактовых импульсов, выход которого соединен с

С-входом двоичного счетчика и с Свходом RS-триггера, выход которого соединен с первым входом первого элемента ИЛИ-НЕ, выход которого соединен с С-входом параллельного регистра и с R-входом двоичного счетчика, первый, второй и третий выходы которого соединены с первыми входами соответственно первого, вторых и третьего элементов И, выходы которых соединены с входами первого сумматора по модулю два, второй вход первого. элемента И подключен к первому выходу параллельного регистра, вторые и треСоставитель О, Геллер, Редактор Н. Тупица Техред М. Ходанич Корректор Н. Король

Тираж 636 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Заказ 5299/57,Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 з 13508 тий выходы которого соединены с первыми входами соответственно вторых и третьего сумматоров по модулю два, выходы которых соединены с вторыми

5 входами соответственно вторых и третьего элементов И, третий выход двоичного счетчика подключен к R-входу

RS-триггера и к второму входу первого элемента ИЛИ-НЕ, при этом первый и вторые выходы двоичного счетчика соединены с вторыми входами соответствующих вторых и третьего сумматоров по модулю два, о т л и ч а ю щ е—, е с я тем, что, с целью повьппения точности формирования, введены второй элемент ИЛИ-НЕ, линии задержки и коммутатор, первые выходы которого через соответствующие линии задержки подключены к первым управляющим входам модулятора, вход включения которого подключен к выходу второго элемента И-НЕ, входы которого соединены с первыми входами коммутатора и с первыми входами соответствующих вторых и третьего элементов И, выход первого элемента ИЛИ-НЕ соединен с вторым входом коммутатора, третий вход которого подключен к выходу первого сумматора по модулю два, второй выход коммутатора соединен с вторым управляющим входом модулятора, выходы которого являются выходами устройства, входами которого являются сигнальные входы параллельного регистра,при этом S-вход RS-триггера является входом устройства.