Функциональный преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - расширение области применения за счет управления величиной шага аргумента и амплитудой сигнала. Функциональный преобразователь содержит блок -1 синхронизации, регистры сдвига 2, 5, 6 и 17, элементы ИЛИ 3, 4, 15 и 16, две группы элементов И 7. и 8, элемент 9 задержки, группу элементов ИЛИ 10, блок 1I счетчиков, мультиплексор 12, формирователь 13 адреса, преобразователь 14 напряже- : ние-частота и два элемента И 18, 19. Принцип действия преобразователя основан на использовании времяимпульсной процедуры формирования кодов функций с заданием ряда временных интервалов , пропорциональных приращениям ординат функций, заполнением этих временных интервалов потоком импульсов , определяющих амплитуду выходного сигнала, и накоплением кодов ординат в соответствзпощих счетчиках. Изменение шага задания аргумента и амплитуды сигнала позволяет использовать функциональный преобразователь как для формирования синусных и косинусных сигналов в системах диагностики , так и при синтезе ряда Фурье. 5 кп. 7 с S (Л со СП ю 4 а /7

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) ф G 06 F 1/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4087956/24-24 (22) 04.07.86 (46) 15.11.87. Бюл. № 42 (71) Всесоюзный научно-исследователь: ский институт электроизмерительных приборов (72) В.И.Якименко, А.Л.Лысенко, А.Ф.Бульбанюк и Ц.Б.Эпштейн (53) 681.325 (088.8) (56) Авторское свидетельство СССР

¹ 840858, кл. G 06 F 1/02, 1979.

Авторское свидетельство СССР

¹- 1149234, кл. G 06 F 1/02, 1983. (54) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к автоматике и вычислительной технике. Цель изобретения — расширение области применения за счет управления величиной шага аргумента и амплитудой сигнала.

Функциональный преобразователь содержит блок 1 синхронизации, регистры сдвига 2, 5, 6 и 17, элементы ИЛИ 3, „,SU, 1352476 А1

4, 15 и 16, две группы элементов И 7. и 8, элемент 9 задержки, группу элементов ИЛИ 1О, блок 11 счетчиков, мультиплексор 12, формирователь 13 адреса, преобразователь 14 напряже- . ние-частота и два элемента И 18, 19.

Принцип действия преобразователя основан на использовании времяимпульсной процедуры формирования кодов функций с заданием ряда временных интервалов, пропорциональных приращениям ординат функций, заполнением этих временных интервалов потоком импульсов, определяющих амплитуду выходного сигнала, и накоплением кодов ординат в соответствующих счетчиках. Изменение шага задания аргумента и амплитуды сигнала позволяет использовать функциональный преобразователь как для формирования синусных и косинусных сигналов в системах диагностики, так и при синтезе ряда Фурье.

5 ил.

2476

I

Изобретение относится к автоматике и вычиалительной технике и может быть использовано как в качестве автономного функционального преобразователя, так и .в качестве периферийного устройства систем автоматизации и контроля объектов, например в технике связи, технической диагностики судовых систем.

Целью изобретения является расширение области применения за счет управления величиной шага аргумента и амплитуды сигнала.

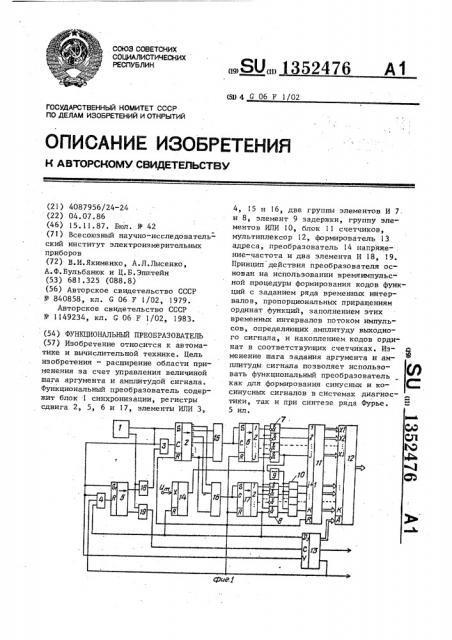

На фиг.1 представлена структурнофункциональная схема функционального преобразователя; на фиг ° 2 — формирование четверти периода синусной функции и возможности одновременного накапливания приращений, например в двух группах счетчиков блока счетчиков; на фиг.3 — разделение выходов регистра сдвига на две группы приращений функций, например на четверти ее периода; на фиг.4 - формирователь адреса; на фиг.5 — диаграммы, поясняющие работу формирователя.

Функциональный преобразователь (фиг ° 1) содержит блок 1 синхронизации, первый регистр 2 сдвига, первый и второй элементы ИЛИ 3 и 4, второй и третий регистры 5 и б сдвига, первую и вторую группы элементов И 7 и 8, элемент 9 задержки, группу элементов ИЛИ 10, блок 11 счетчиков, мультиплексор 12, формирователь 13 адреса, преобразователь 14 напряжение-частота, третий и четвертый элементы ИЛИ 15 и 16, четвертый регистр

17 сдвига и два элемента И 18, 19.

Формирователь 13 адреса (фиг.4) может быть выполнен, например, содержащим первый триггер 20, регистр 21, с первого по шестой элементы задержки 22-27, первый элемент 2И-ИЛИ 28, с первого по пятый сумматоры 29-34, первый и второй счетчики 35 и 36, два устройства сравнения 37 и 38,второй триггер 39, сумматоры 40 и 41 по модулю два, второй и третий элементы 2И-ИЛИ 42 и 43, ключ 44 и седьмой элемент задержки 45.

Работа функционального преобразователя происходит следующим образом.

Синусоидальная функция является монотонно возрастающей на первой четверти периода, поэтому можно определить значения аргумента п, при которых значения соответствующих ординат

8 синуснои функции меньше их максиN мального значения 8 (n c k = -—

4 где N — - количество отсчетов за период Функции), Эта закономерность иллюстрируется на фиг.2 а, где значения ординат от 9 до 6 удовлетворяо J ют условию

n = О, 1, 2...,, 8

В структуре заявляемого функционального преобразователя это учитывается следующим образом. Регистр 2

15 сдвига содержит 1 ячеек сдвига, причем 1 пропорционально в выбранном масштабе значению 9>/2. Выходы регистра 2 сдвига разделены на две группы (фиг.3). Количество ячеек сдвига

20 (А 1 „) между соседними выходами первой группы (с номерами от 0 до 1; от 1 до 2, от 2 до 3 и т,.д. до j-ro) (пропорционально приращениям значений функции (ф 8 „ на фиг.2б) между соот"1 ветствующими двумя соседними ординатами. Аналогичным образом организованы выходы второй группы с номерами от j+1 до К..

В исходном состоянии регистры 2, 30 5, 6, 17 сдвига, блок 11 счетчиков, формирователь 13 адреса и преобразователь 14 напряжение — частота обнулены.

В начале работы включается блок 1 синхронизации, с первоro выхода которого поступают тактовые импульсы, а с второго (например, через делитель частоты) — синхроимпульсы, период повторения которых задан равным периоду

4О подключения значений напряжений П,„ (например, U подключается через ключ, стробируемый m-м синхроимпульсом. Ключ для упрощения схемы не показан на фиг.1 на. входе -преобразова45 теля 14).

При поступлении первого синхроимпульса (m = 1) с второго выхода блока 1 синхронизации он подается на управляющий вход формирователя 13 адре; са и на входы S записи и тактовые входы С регистров 2 и 5 сдвига, что вызывает установку их первых разря- дов в состояние "1". Одновременно на

55 информационный вход преобразователя 14.íàïðÿæåíèå-частота подключается напряжение 11„ (задающее амплитуду выходной функции, считываемой с выхода мультиплексора 12).

476

3 1352

Благодаря "1" в первом разряде регистра 5 сдвига разрешается прохождение .тактовых импульсов через элемент И 18; поступая далее через элемент ИЛИ 3 на тактовый вход регистра 2 сдвига, тактовые импульсы осуществляют перемещение единичного"

ll состояния из первого в последующие разряды этого регистра.

Промежуток времени, за который f0

It II

1 достигнет первого выхода регистра 2 сдвига, равен

Т .41, OII где Т „ — период тактовых импульсов на первом выходе генератора 1;

d1 — количество разрядов до первого выхода регистра 2 сдвига.

Промежуток времени, за который

"1" достигнет выхода (j +1) этого же регистра, равен:

) o 25 где 1 „ — количество разрядов до (j+1)-го выхода регистра 2 сдвига.

Аналогично определяется в общем виде промежуток времени t (для пер-30

Il1 вой группы выходов)

n„

"п1 = Топ =411 = Т оп 1 и, 1=1.

1 и промежуток времени t (для второй

"2 группы выходов) и, п1 Топ — 1 Т рп

1.=! +1

Появление импульса на каждом последующем выходе первой группы реги- 40 стра 2 сдвига воздействует через элемент ИЛИ 15 на С-вход регистра 6 сдвига, вызывая сдвиг имеющегося содержимого и запись в освободившийся младший РазРяд 1 (т.е. одержимое 4 регистра 6 сдвига изменяется следующим образом: 0000 ...,1000...,1100

1110... и т.д.).

Модификация содержимого регистра 6 сдвига, описанная выше, приводит к последовательному запиранию через промежутки времени С„ (и „ р C1,j 2) соответствующих входов группы элементов И 7.

Аналогичным образом последователь-5 ное появление импульса на выходах второй группы регистра 2 сдвига с номерами от j +1 до К модифицирует через элемент ИЛИ 16 содержимое регистра 17 сдвига, вызывая последовательное запирание соответствующих входов группы элементов И 8 через промежуток времени t „ (n e ((j +1), K3) °

Одновременно с этим в каждом счетчике с номером от 1 до j блока 11 счетчиков накапливается и запоминается количество импульсов частоты f прошедших с выхода преобразователя

14 напряжение-частота через соответствующий вход группы элементов И 7 за промежуток времени t> определенный выше.

Одновременно во второй группе счетчиков с номерами от j+1 до К блока 11 счетчиков накапливается количество импульсов, поступающих с соответствующего выхода группы элементов ИЛИ 10. Это количество импульсов

; равно сумме числа импульсов, прошедших через соответствующий элемент групп элементов И 8 за промежуток времени t è числа импульсов 8 п2 J

8> /2, прошедших через последний элемент группы элементов И 7 за интервал времени t (Для предотвращеJ ния перекрытия двух последовательностей импульсов, поступающих на входы. элементов ИЛИ 10, необходимо, во-первых, чтобы сигналы на выходе преобразователя 14 напряжение-частота имел большую скважность, и, во-вторых, чтобы элемент 9 задержки обеспечивал задержку сигнала С " 0,5/ a, где <еа„ максимально возможное значение частоты импульсов на выходе преобразователя 14 напряжение-частота).

Следовательно, после заппрания всех входов первой и второй групп элементов И 7 и 8 в счетчиках с до хранятся коды

Топ

N — -1 — — -- -- 1 1, (п = 1, 2,...,j). а в счетчиках с, (j+1) по К хранятся коды

t n<+t S 70tI

И = — -- — - - = — -(1 +1)

"2 Т Т (n z = (j+1), (j+2),..., К) .

Так как частота f = . U a

Гт1 числа 1„, 1„, 1 пропорциональны сои, ответственно значениям 8„, В,, 6 /2

П11 П2 1 в выбранном масштабе, то содержимое в двоичном коде счетчиков и1 и и оказывается пропорциональным соответствующим отсчетам синусной функции

10 (n = 1, 2, ..., К).

sin п и (— —. — -) К 2

cos ь Пь

m 1

N при m ° 1 6 — 2-,.

А с,„;

N N

+ р ——

4 2 предыдущий

-m -1 при m

М

i) р. Ы N( тп-i < — — + р — - знак — при

sgn С .N И измененный знак — при тп i ) - — + р

4 2

13524 амплитуды О при аргументах, равных и, и и соответственно (фиг. 2а) .

Такйм образом, в блоке 11 счетчиков накоплены коды, пропорциональные произведениям ряда ординат синусоиды

5 (косинусоиды) на интервале и/2 на значение напряжения U задающего амплитуду выходного сигнала

Одновременно с закрытием последнего входа группы элементов .И 8 импульс с 15 последнего выхода регистра 17 сдвига поступает на вход обнуления преобразователя 14 напряжение-частота, на вход начальной установки формирователя 13 адреса и через элемент ИЛИ 4 2g на тактовый вход регистра 5 сдвига, осуществляя сдвиг единичного импульса из первого во второй разряд. закрывается элемент И 18, открывается элемент И 19, благодаря чему такто- 25 вые импульсы начинают поступать на тактовый вход С формирователя 13 адреса, начиная цикл формирования кодов адреса для поочередного считывания соответствующих кодов вычисленной дд функции на выход мультиплексора 12.

Формирование необходимой упорядоченной последовательности кодов-отсчетов функций на выходе функционального преобразователя может осуществляться при помощи формирователя 13 адреса в одном из двух режимов слегде р — номер перехода косинусной функции через нулевой уровень (причем р = О, 1,...,(ш+1).

Следовательно, при первом синхроимпульсе (m 1) шаг изменения кодов адреса 4А = 1 и на вход функциональ55 ного преобразователя считываются N =

4К кодов косинусной функции с соответствующим знаком sgn поступающим со знакового выхода формирователя 13

76

6 дующим образом: при постоянном шаге аргумента аА = 1, т.е. единичном ин- тервале между кодами ряда адресов

А>, Л ...А, А> и т.д., а также с переменным шагом 8 A между концами адресов, изменяющимся через определенное количество N считываемых орди-! нат функций. Первый режим необходим, например, при формировании тестовых синусоидальных сигналов большой длительности (формирователь 13 адреса в этом случае имеет простую структуру— на основе реверсивного счетчика с изменяющимся на единицу кодом). Второй режим необходим при синтезе ряда Фурье, описывающего сложные сигналы, т.е. для формирования ряда гармоник различной амплитуды U с кратно изменяющимся количе с твом пе р иодо в .

Процедура вычисления кодов синусно-косинусных функций в функциональном преобразователе идентична для любого номера m = 1, 2,. ° ., N синхроимпульса, поступающего с второго выхода блока 1 синхронизации при одновременной подаче отсчета напряжения U U

Ч» 2»

U,..., U» на вход преобразователя 14 напряжение — частота, а вычисление кодов адресов в формирователе 13 адреса:для считывания на выход мультиплексора 12, например, косинусных функций ряда частот, необходимых для синтеза ряда Фурье, в общем виде описывается следующими соотношениями: адреса, а после считывания N-ro кода на управляющий выход Конец" формирователя 13 поступает импульс, прекращающий работу последующих блоков информационно-вычислительного комплекса, в состав которого входит функцио-, нальный генератор (также устанавливающий в исходное состояние регистры 5, 6, 17 сдвига). При этом, благодаря нулевому состоянию первого и

7 1 152476 8 второго разрядов двухразрядного регистра 5 сдвига, закрывается прохождение тактовых i импульсов на вход с формирователя 13 адреса.

При следующем синхроимпульсе (m = 5 — 2) работа функционального преобразователя аналогична описанной, но

U„= U2 и шаг аргумента дА = m = 2, т.е. на выход мультиплексора 12 по каждому i-му тактовому импульсу счи1 тывается соответствующий код С, I т.е. Ср С2, С4,..., С1,,..., С, Ср °

С,..., причем количество ординат на

N период функции равно П

m подключении к выходу мультиплексо— ра 12 цифроаналогового преобразователя на его выход поступает соответствующий ряд N частот непрерывных косинусных функций, например для задач непрерывного управления сббъектами или для синтеза непрерывной сложной функции.

Рассмотрим подробнее работу возможного варианта выполнения формирователя 13 адреса.

Режим 1. Ключ 44 установлен в положение а, при котором его выход через элемент 45 задержки подключен к

R-входу счетчика 36 шага агрумента.

Перед началом работы формирователя через его управляющий вход в счетчик 36 шага аргумента поступает управляющий импульс, установив содержание счетчика 36 равным д А = 1, а на вход начальной установки D поступил импульс с последнего выхода регистра 6 сдвига, благодаря чему в сумматор 31 записывается код N/2 с регистра 21, а триггеры 20 и 39 установле40 ны в состояние, при KoTopbIx открыт первый вход элементов 2И-ИЛИ 28, 42

И 43, а ЧЕРЕЗ ИНтЕрВаЛ ВРЕМЕНИ с24 (заданный элементом 34 задержки) этот импульс поступает на тактовый вход

45 сумматора 29, разрешая запись в него кода К = N/4 с первого выхода регистра 21.

Таким образом, в сумматорах 29 и 33, предназначенных для установки

50 значений кодов граничных условий А и А о (фиг.5б и 5a), в начальном состоянии установлены соответственно коды адресов А о = N/4, А so = О, а в сумматоре 31 — код N/2 для контроля

55 знака синусной функции.

По первому тактовому импульсу (i = 1) в счетчике 35 тактов чстанавливается код k. = I, а в сумматорывычислители 30 и 34 по импульсу на их тактовых входах разрешается запись соответственно кодов A и А,. Код

Асо через первый вход элемента 2ИИЛИ 42 подается на адресный вход мультиплексора 12 (фиг.1), на выход которого считывается код С р = М/4, знак которого sgn = +! считывается с выхода сумматора 40 по модулю два че- рез открытый первый вход элемента 2ИИЛИ 43 на входу функционального преобразователя.

Через интервал времени 2 7

26 24 этот тактовый импульс поступает на вход триггера 39, изменяя его состояние: через открытый второй вход элемента 2И-ИЛИ 42 на его выход подается код A а через открытый второй вход элемента 2И-ИЛИ 43 на его выход с выхода сумматора 41 по модулю два подается знак отсчета синусной функции.

З ИитЕРВаЛ ВРЕМЕНИ с26+ приблизительно равный интервалу gt между тактовыми импульсами, триггер 39 возвращается в исходное состояние.

При этом через интервал времени C26-= 0,9дс первый тактовый импульс поступает на вход С сумматора 32, раз» решает изменение значения аргумента:

А, = А + дА = 1. Этот код подается на вторые входы устройств сравнения

37 и 38 и вторые входы сумматоров-вычислителей 30 и 34.

Второй тактовый импульс устанавливает в счетчике 35 состояние i = 2 и разрешает операции сравнения текущих кодов в устройствах 37 и 38 сравнения с граничными условиями, а в сумматорах-вычислителях 30 и 34 разрешаются операции вычитания по модулю

A, =l - A(=-„— — со

=(Азр — дА(= 1.

Эти коды, как и в предыдущем случае, считываются через элемент 2ИИЛИ 42 на адресный вход мультиплексора 12, а знаки соответствующих кодов ординат считываются с выхода элемента 2И-ИЛИ 43.

Аналогично процедура формирования кодов адреса и знака выходных функций выпопняется до такта i = N/4, соответствующего граничному условию, записанному в сумматоре 29 (фиг.5а,б); при этоь! срабатывает устройство 37 сравнения, выходной импульс которого является микрокомандой на изменение

1352476 знака косинусной функции (фиг.5б) в сумматоре 40 по модулю два и микрокомандой на изменение кода граничиого условия в сумматоре 38, в который записывается код с второго выхода ре- 5 гистра 21 коэффициентов, После этого в течение следующей четверти периода функции- на выход мультиплексора 12 подаются коды функций, определяемые кодами адреса с кодового выхода фор- 10 мирователя 13 адреса, а со знакового выхода формирователя 13 адреса с выходов сумматора 40 или 41 по модулю два подаются потенциалы, соответствующие положительному (фиг.5а) или 15 отрицательному (фиг ° 5б) знаку ординат этих функций.

Так как в счетчике 36 шага аргумента записано неизменно одно число

m = 1, то выходные сигналы функцио- 20 нального генератора имеют постоянный шаг аргумента А = 1 в течение заданного количества периодов функции. При этом после окончания каждого периода (при i = N) с выхода переполнения счетчика 35 поступает импульс, устанавливающий в нулевое состояние счетчик 35 и сумматоры 29-34, а через время L 4 0 5dt этОт импульс пОсту= пает на вход обнуления счетчика 36.

Вследствие этого следующий импульс m, поступающий на вход m формирователя адреса вновь задает начальные состоя.ния в сумматорах 40, 41 по модулю два, а в счетчике 36 шага аргумента 35 устанавливает вновь код В А =

Таким образом, формирователь 13 адреса подготовлен к заданию кодов адресов и знаков следующего периода 40 функции с постоянным шагом.

Режим 2. Ключ 44 установлен в положение б, при котором исключено периодическое обнуление счетчика 36, благодаря чему достигается изменение 45 шага аргумента д А = mdA„ после окон чания каждого периода функций.

При первом импульсе (m = 1), поступающем на управляющий вход форми- 5О рователя адреса, в счетчике 36 шага аргумента устанавливается код 4А „ =1, после чего по каждому тактовому i-му импульсу осуществляется формирование кодов адреса и изменение знаков орди-55 нат функции аналогично режиму 1, при котором адресов

Но после окончания формирования

N кодов адресов (т.е. считывания на выход функционального преобразователя одного периода синусной и косинусной функций) импульс переполнения счетчика 35 тактов поступает не только на входы обнуления сумматоров 29-34, но и на управляющий выход формирователя 13 адреса,с которого подается через элемент ИЛИ 4 на тактовый вход регистра 5 сдвига: записанный в нем одиночный импульс сдвигается с второго разряда, вследствие чего регистр 5 сдвига обнуляется, запрещая прохождение тактовых импульсов через элемент И 19 на.тактовый вход формирователя 13 адреса.

Второй управляющий импульс (m = 2) с второго выхода блока 1 синхронизации, поступая на управляющий вход формирователя 13 адреса, устанавливает в начальные состояния сумматоры 40, 41 по модулю два, а в счетчике 36 шага аргумента устанавливается код dA<2.

Одновременно с поступлением в логические устройства функционального преобразователя импульса" ш = 2 на вход преобразователя 14 напряжениечастота подключается напряжение уровня U<, a в процессе формирования функции в блоке 11 счетчиков накапливается новый ряд кодов 9 „.

После этого начинается процедура считывания этих кодов через мультиплексор 12 по кодам адресов, сформированных с шагом в формирователе 13 адреса: аналогично случаю m - =йА, =

1 сначала в сумматор 29 записывается код граничного условия N/4, в сумматор 31 — код N/2, в сумматоре 33 остается нулевое значение кода, после чего в сумматоре 32 каждый i-й тактовый импульс разрешает операции суммирования: (1-1) + 1 Л = ш1.

Это текущее значение кода (m i) используется для сравнения с граничными условиями в устройствах 37 и 38 сравнения при поступлении каждого -го тактового импульса.

При переходе одной из функций нулевого значения (фиг.5а) срабатывает одно из устройств сравнения 37 или

38: при микрокоманде р = 1 с устройства 37 сравнения разрешается запись в сумматор 33 граничного условия N/2

11 1352476 (для формирования кодов (:. . — фиг.5а), т

111 1 а в сумматоре 40 по модулю два изме- н няется состояние в соответствии с изс менением знака косинусной функции (фиг.5б) . 5 а 2И-ИЛИ 28) и через элемент ЙГПГ72 а изменение граничного условия в умматоре 31 на значение А = (— — +

N зрр 2 †-), а в сумматоре 29 — на значеN N ние А- = (— — + — -) ° /p 4 2

Таким образом, процедуры соответствующего изменения знаков и кодов адресов считывания ординат синусной и косинусной функции выполняются в течение тактов в соответствии с соотношениями

При значении аргумента m i>, N/2 срабатывает устройство 38 сравнения, формируя микрокоманду на изменение состояния сумматора 41 по модулю два 10 (в соответствии со знаком синусной функции), триггера 20 (вследствие чего открывается второй вход элеменN 1 предыдущий знак — при m i <) p

sgn S

N1i

N измененный знак — при m i mI р ——

m — при m ° i

m.i — р — - — ири m.i > (N/4 + р N/2(; предыдущий знак — при m i < N/2;

sgn С измененный знак — при m i ) IN/4 + р N/2I

I N/4 — m. i1 — при m i < N/2;

А

c„„

l N/4+p N/2 — mi) — при m i) р N/2.

В частота, блок счетчиков, мультиплексор, формирователь адреса, элемент задержки, две группы элементов И, группа элементов ИЛИ и третий и четвертый элементы ИПИ, при этом второй выход блока синхронизации соединен с входом управления записью формирователя адреса, входами записи первого и второго регистров сдвига и первыми входами первого и второго элементов ИЛИ, выходы которых подключены к тактовым входам первого и второго регистров сдвига соответственно, при этом третий элемент ИЛИ соединен входами с первой группой выходов первого регистра сдвига, а выходом — с входом записи и тактовым входом третьего регистра сдвига, подключенного выходами к инверсным входам элементов И первой группы, соединенных прямыми входами с выходом преобразователя напряжение— частота и прямыми входами элементов И второй группы, а выходами — с соот ветствующими счетными входами блока счетчиков, остальные счетные входы которого подключены к выходам элеменСледовательно, по одному i-му тактовому импульсу на выход функционального преобразователя считывается одна ордината синусной функции и одна ордината косинусной функции и соответствующие им знаки для одного периода кратного ряда N дискретных функций или функций ряда N частот. Зто достигается благодаря считыванию кодов ряда кратных гармоник с переменным числом ординат N N/m на период функtrl ции, что достигается благодаря крат- 45 ному изменению шага аргумента.

Формула и з обре т е н и я

Функциональный преобразователь, содержащий регистры сдвига, первый и второй элементы ИЛИ и два элемента И, подключенных первыми входами к первому выходу блока синхронизации, о т— л и ч а ю шийся тем, что, с це- 55 лью расширения области применения путем управления величиной шага аргумента и амплитуды сигнала, в него введены преобразователь напряжение—

13524 тов ИЛИ группы, соединенных первыми входами с выходом элемента задержки, а вторыми входами — с выходами соответствующих элементов И второй группы, подключенных инверсными входами к выходам четвертого регистра сдвига, .соединенного входом записи и тактовым входом с выходом четвертого элемента ИЛИ, входы которого подключены к последнему выходу первой группы и t0 второй группы выходов первого регистра сдвига, соединенного входом обнуления с входами обнуления блока счет- чиков, третьего и четвертого регистров сдвига, вторым входом второго l5 .элемента ИЛИ и выходом завершения цикла формирователя адреса, подключенного входом начальной установки к выходу последнего разряда четвертого регистра сдвига, третьему входу вто- 20

76 l4 рого элемента ИЛИ и входу сброса преобразователя напряжение — частота, информационный вход которого является входом управления амплитудой сигнала функционального преобразователя, при этом выход последнего элемента И первой группы соединен с входом элемента задержки, а выходы второго регистра сдвига подключены к .вторым входам первого и второго элементов И, выходы которых соединены соответственно с вторым входом первого элемента ИЛИ и тактовым входом формирователя адреса, кодовый выход которого подключен к управляющему входу мультиплексора, соединенного информационными входами с выходами блока счетчиков, а выходом - с информационным выходом функционального преобразователя.

ТИ

l 352476

1352476 лэЯмув усюаЖ

Sga

Составитель С. Казинов

Техред М.Ходанич

Редактор M.Циткина

Корректор M.Øàðoøè

Заказ 5566/48 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретенжЪ и QTKpbITHB

113035, Москва, Ж-35, Раушская наб., д. 4/5

И

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4