Устройство для коррекции ошибок

Иллюстрации

Показать всеРеферат

Целью изобретения является повышение надежности и сокращение затрат на коррекцию ошибок. Устройство содержит основной блок 1, контрольные блоки 2 и 3, блоки коммутации 4, узлы контроля 5, блок управления 6. Сигналы на выходах всех подблоков коммутации удовлетворяют трем контрольным соотношениям, проверяемым узлами контроля. Выходы основного блока разбиты на две группы, каждая из которых имеет контрольный сигнал по модулю два, формируемый первым контрольным блоком, второй контрольный блок формирует вектор контр ольных сигналов, равный поразрядной сумме сигналов первой и второй групп основного блока и сигналов первого контрольного блока. Такая организация контроля обеспечивает при ординарном потоке отказов независимую коррекцию одиночных ошибок по каждой трехразрядной группе, образованной выходами первой и второй групп основного блока и выходом второго контрольного блока. 1 з.п. ф-лы, 7 ил. ш (Л ОО СП tc N4 СО о

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4031700/24-24 (22) 03.03.86 (46) 15. 11.87. Бюл. Р 42 (72) Ю.А.Курочкин и Е.Г.Лещенко (53) 621.396(088.8) (56) Акцептованная заявка Японии

У 48-13851, кл. G 06 F 11/00, опублик. 1973.

Авторское свидетельство СССР

N - 109 1168, кл. G 06 F 11/18, 1982. (54) УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК (57) Целью изобретения является повышенйе надежности и сокращение затрат на коррекцию ошибок. Устройство содержит основной блок 1, контрольные блоки 2 и 3, блоки коммутации 4, узлы контроля 5, блок управления 6. Сигналы на выходах всех

„„SU„„1352490 А 1 (51)4 G 06 F 11/18, Н 05 К 10/00 подблоков коммутации удовлетворяют трем контрольным соотношениям, проверяемым узлами контроля. Выходы основного блока разбиты на две группы, каждая из которых имеет контрольный сигнал по модулю два, формируемый первым KOHTpoJTbHbM блоком, второй контрольный блок формирует вектор контрольных сигналов, равный поразрядной сумме сигналов первой и второй групп основного блока и сигналов первого контрольного блока. Такая организация контроля обеспечивает при ординарном потоке отказов независимую коррекцию одиночных ошибок по каждой трехразрядной группе, образованной выходами первой и второй групп @ основного блока и выходом второго контрольного блока. 1 з.п. ф-лы, 7 ил. С:

1 13524

Изобретение относится к вычислительной технике и автоматике и может) быть использовано для построения надежных цифровых устройств.

Целью изобретения является повышение надежности и сокращение затрат на коррекцию ошибок.

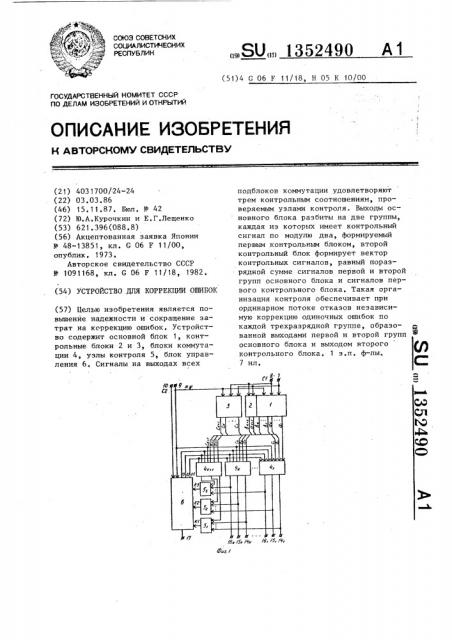

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 — функциональная схема подблока коммутации; на фиг. 3 — функциональная схема узла управления коммутацией; на фиг.

4 — функциональная схема блока управления; на фиг. 5 — функциональная схема ключа; на фиг. 6 — временные диаграммы работы блока управления на фиг. 7 — схема реализации основного блока и первого и второго контрольных блоков. 20

Устройство (фиг. 1) содержит основной блок 1,первый контрольный блок . 2, второй контрольный блок 3 блоки 4 коммутации, (i = I, К т 1), где 2К вЂ” число выходов основного бло- 25 ка, с первого по третий узлы контроля (УК) 5. (i = 1,3), блок 6 управления. Устройство содержит также информационный вход 7, входы приема первого строба 8, сигнала начальной установки 9, второго строба 10, первые 14 и вторые 15 информационные выходы, контрольный выход 17. Основной блок 1 имеет первую 11 и вторую 12. группы выходов - = 1,К, первый конт- 35 рольный блок 2, первый 11(и второй (ф1

12 „ контрольные выходы, второй контК+1 рольный блок 3, контрольные выходы

13, (i = 1,К+1) . Подблоки коммутации имеют контрольные выходы 16, а блок 40 управления — контрольные входы КЗ и

К4 и управляющие выходы 1.1-13. Узлы контроля реализованы в виде сумматоров по модулю два на (К+1) вход.

Блок 4. коммутации (фиг. 2) содержит с первого по третий ключи 20-22, элементы 23-25 неравнозначнасти, сумматор 26 по модулю два и узел 27 управления коммутацией (УУК), имеющий с первого по третий управляющие выходы

28; (i = 1,3).

Узел 27 управления коммутацией (фиг. 3) содержит элементы. И-HE 3133, триггеры 34-36.

Блок 6 управления (фиг. 4) содержит группу из трех элементов И 37, элемент НЕ 38, элемент ИЛИ 39 и Dтриггер 40, 90 2

Ключи 20-22 (фиг, 5) содержат элементы И 41 и 42, элемент НЕ 43, элемент ИЛИ 44.

Работа устройства основана на ординарности потока отказов, что позволяет расширить корректирующие воэможности используемого в устройстве метода защиты от ошибок. Выходы устройства с независимой реализацией выходных функций разбиваются на две руппы = (a,, a<, ..., а„) и В = (Ъ„, Ъ,..., ЬИ), BBopHTcH BepBbe контрольйый блок 2, реализующий функции

)=К iK а,„=,К а; (mod)), b = » b;(mod2)

i=1 )и 1 и второй контрольный блок 3, реализующий функции С; = а ., Щ Ь; (i = Г, K+1)1.

ieк

В этом случае С „ = С;(шод2).

1и1

В результате имеются три контрольных соотношения для всего устройства

1= kI.1

К1 = 1(» а. (mod2);

1нт

\и Кит

К2 =, .Ь; (mod2);

1к 1

1-К

КЗ = .С; (mod 2) .

Известны устройства, в которых данный метод защиты от ошибки позволяет исправлять одиночные ошибки в каждом слове. В данном устройстве используется еще одно контрольное соотношение К4 = ài Q+ b, Д+ с, что при учете ординарности потока отказов позволяет исправлять одиночные ошибки в каждой группе выходов а., b. с. (i = 1,К+1) .

При обнаружении отказа в блоке, формирующем сигнал, последний заменяется на сигнал Ъ; О+ с;(а; С+) с ), что позволяет исправить ошибку и сохранить условия выполнения контрольных соотношений К1-КЗ. При появлении отказа в следующей группе аналогично заменяется ошибочный сигнал и восстанавливается контрольное соотношение, в которое данный сигнал входит.

При появлении второго отказа в группе воэможность замены ошибочного сигнала отсутствует, но данная ошибка обнаруживается нарушением двух из трех контрольных соотношений К1 — КЗ.

3 135249

Устройство работает следующим образом.

По сигналу начальной установки производится установка в исходное сос5 тояние всех элементов памяти основного 1 и контрольных 2 и 3 блоков, блоков 4 коммутации и блока 6 управления.

При этом блоки 4 коммутации подключают к первым информационным выходам

14 первой группы выходов основного блока 1, а к вторым информационным выходам 15 — вторую, группу выходов основного блока 1, к контрольным выходам — выходы второго контрольного блока 3, к информационным выходам (К+1)-ro подблока коммутации подклю— чают выходы первого контрольного блока 2.

По первому стробу С1 входные сигна- 2р лы поступают на основной и контроль- ный блоки. В случае отсутствия ошибок управляющие сигналы К1-КЗ равны нулю поэтому никаких переключений подблоков коммутатора не производится, 25 а по спаду второго строба С2 производится выдача выходных сигналов на выход устройства.

В случае появления отказа в основном блоке 1, вызывавшем ошибку в од- Зр ном из сигналов первой группы, ошибка вызывает нарушение контрольной суммы К1. По стробу С2 контрольные сум- мы выдаются на блоки 4 коммутации.

Управляющий сигнал принимается толь- ко подблоком, у которого нарушена контрольная сумма К4, Блок 4 фиксирует отказ к своему первому информационному выходу выход функции b Q+

®с;. В результате к спаду строба С2 4р соотношение К1 восстанавливается (К1 = О) и по спаду С2 производится выдача выходных сигналов. Если же в устройствах, подключенных к данному подблоку 4, возник второй отказ, то 4> никаких переключений не производится, соответствующие контрольные соотношения остаются нарушенными (равны единице). По спаду строба С2 блок

6 управления фиксирует отказ и формирует контрольный сигнал на выходе

17. Работа устройства заканчивается.

Подблок коммутатора (фиг. 2) работает следующим образом.

После начальной установки к выходам 14 ., 15, и 16; подключены соответственно шины а 1, Ъ „. и с..(вхо.ды 11;, 12; и 13; соответственно).

Элементы 23-25 формируют сигналы

4 а. 0+ с, . О+ b;, b О+ с.. Сумматор 26 по модулю два формирует контроль— ную сумму К4 ° Узел управления коммутацией выявляет совпадение единич— ных сигналов К1-КЗ и сигнала К4, фиксирует отказ и выдает управляюций сигнал П1-П3 для переключения соответствующего ключа.

Отметим, что после срабатывания одного из триггеров узла 27 конт— рольная сумма К4 всегда будет равна нулю (при исправном подблоке коммутации). Действительно, К4 = а О+

+ Ь О+ с- после замены a; = b; O++) с имеет вид К4 = (Ь (+) с,) Q+ Ь,. О+ с, = О, что защищает подблок в дальнейшем от ложных срабатываний.

На фиг. 6 приведена временная диаграмма работы блока 6. При отсутствии ошибок в выходной информации на входах К1-КЗ формируются нулевые сигналы при поступлении синхросигнала С2.

Пусть появился отказ в блоке 14.

1 формирования сигнала. Тогда к моменту поступления сигнала С2 на выходе

К1 устанавливается единичный сигнал.

По сигналу С2 на выходе 11 формируется единичный сигнал, который, поступая на блок 4. коммутации, вызывает подключение выхода 14.. на фор1 мирователь сигнала b. Q+ с.. В результате контрольное соотношение на входе К1 восстанавливается. По спаду сигнала С2 цикл работы блоков заканчивается. Если в дальнейшем возникнет ошибка на выходе 16., то в cocl тояние " 1" установятся сигналы на входах К1 и КЗ. По сигналу С2 на выходе блока 6 управления формируются сигналы. Поскольку в этом случае никаких переключений в блоке 4 не про1 изводится, то сигналы К1 и КЗ не снимаются до спада сигнала С2. По спаду сигнала С2 устанавливается в "1" триггер 40, фиксируя на выходе 17 блока 6 управления единичный сигнал отказа устройства.

Пример реализации блоков 1-3. Допустим, что имеется устройство с выходными функциями у = х р х ; у =

=хЧху=хЛх:y=xQ+

1 2», 2» 4 1

Q+) х2 ° Для определения выходных функций контрольных блоков 2 и 3 все множество выходов разбивается на два подмножества А и В, где а; Е A u а1,у1; а2 у2 b ЕВиЬ, =У, b = v . Далее в соответствии с при1352490 6 веденными выше формулами значения всех контрольных функций следующие: а, О+а, Ъ, О+Ъ, a„O+ Ъ, а О+Ъ

CC„O++, хх, O++ х, и х

x A а Я а

Ъ х2 х с

1 с, х

Ъ =х„лх

На фиг. 7 приведена функциональ- f0 ная схема блоков 1-3, устройства, построенного на комбинационных схемах (элементы 45-52). Предполагается, что число выходов основного блока должно быть четным. В противном слу- 15 чае необходимо дополнить количест-— во выходов до четного, например реализовав одну функцию основного блока дважды.

20 изобретения

Формула

1. Устройство для коррекции ошибок, содержащее блоки коммутации, входы начальной установки которых подключены к соответствующему входу устройства, а первые информационные выходы подключены к первым информационным выходам устройства и к входам первого узла контроля, о т л и ч а ю — . З0 щ е е с я тем, что, с целью повышения надежности и сокращения затрат на коррекцию ошибок, введены второй и третий узлы контроля и блок управления, причем первые информационные 35 входы блоков коммутации подключены к соответствующим выходам первой группы выходов основного блока, а вторые информационные входы — к соответствующим выходам второй группы выходов 40 основного блока, первый и второй информационные входы соответствующего блока коммутации подключены к первому и второму выходам соответственно первого контрольного блока, контрольные 4S входы всех блоков коммутации подключены к соответствующим выходам второго контрольного блока, вторые информационные выходы — к вторым информационным выходам устройства и к входам второго узла контроля, а контрольные выходы — к входам третьего узла контроля, выходы узлов контроля подключены к соответствующим конт-. рольным входам блока управления, входы начальной установки и приема второго строба которого подключены к соответствующим входам устройства, а первый, второй и третий управляющие выходы — к соответствующим управляющим входам коммутации, контрольный выход — к контрольному выходу устройства.

2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что каждый блок коммутации содержит с первого по третий ключи и элементы неравнозначности, сумматор по модулю два и узел управления коммутацией, причем первый информационный вход блока подключен к первым входам первого ключа, первого и второго элементов неравноэначности, второй информационный вход подключен к первым входам второго ключа и третьего элемента неравнозначности и к второму входу второго элемента неравнозначности, контрольный вход подключен к первому входу третьего ключа и к вторым входам первого и третьего элементов неравнозначности, вторые входы первого, второго и третьего ключей подключены к выходам третьего, первого и второго элементов неравнозначности соответственно, а выходы — соответственно к первому, второму информационным выходам и контрольному выходу блока, а также к входам сумматора по модулю два, выход которого подключен к входу разрешения записи узла управления коммутацией, с первого по третий управляющие входы и вход начальной установки которого подключены к соответствующим входам блока, а с первого по третий управляющие выходы— к управляющим входам одноименных ключей.

1352490

1352490 чаи сии.

Фжб

Составитель В.Максимов

Редактор Ю.Середа Техред М.Ходанич

Корректор Л.Пилипенко

Заказ 5567/49 Тираж 671

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, И-35, Раушская наб, д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород," ул. Проектная, 4