Цифровой нерекурсивный фильтр

Иллюстрации

Показать всеРеферат

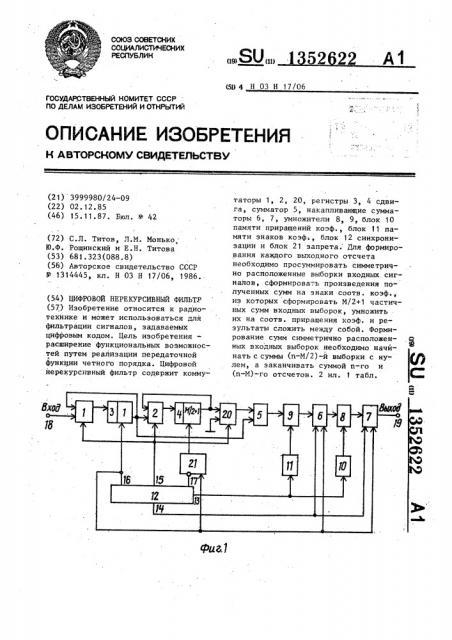

) Изобретение относится к радиотехнике и может использоваться для фильтрации сигналов, задаваемых цифровым кодом. Цель изобретения - расширение функциональных возможностей путем реализации передаточной функции четного йорядка. Цифровой йерекурс1шный фильтр содержит коммутаторы 1, 2, 20, регистры 3, 4 сдвига , сумматор 5, накапливакнцие сумматоры 6, 7, умножители 8, 9, блок 10 памяти приращений коэф., блок 11 памяти знаков коэф, блок 12 синхронизации и блок 21 запрета. Для формирования каждого выходного отсчета необходимо просуммировать симметрично расположенные выборки входных, сигналов , сформировать произведения полученных сумм на знаки соотв. коэф., из которых сформировать М/2+1 частичных сумм входных выборок, умножить их на соотв. приращения коэф. и результаты сложить между собой. Формирование сумм симметрично расположенных входных выборок необходимо начинать с суммы (п-М/2)-й выборки с нулем , а заканчивать суммой п-го и (п-М)-го отсчетов. 2 ил. 1 табл. i (Л С ФигЛ

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (51) 4 Н 03 Н 17/06

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ (21) 3999980/24-09 (22) 02.12.85 (46) 15.11.87. Бюл. Е 42 риг.1

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (72) С.Л. Титов, Л.М. Монько, Ю.Ф. Рощинский и Е.Н. Титова (53) 681.323(088.8) (56) Авторское свидетельство СССР

)ь 1314445, кл. Н 03 Н 17/06, 1986. (54) ЦИФРОВОЙ НЕРЕКУРСИВНЫЙ ФИЛЬТР (57) Изобретение относится к радиотехнике и может использоваться для фильтрации сигналов, задаваемых цифровым кодом. Цель изобретения— расширение функциональных возможностей путем реализации передаточной функции четного порядка. Цифровой нерекурсивный фильтр содержит коммутаторы 1, 2, 20, регистры 3, 4 сдвига, сумматор 5, накапливающие сумматоры 6, 7, умножители 8, 9, блок 10 памяти приращении коэф., блок 11 памяти знаков коэф1, блок 12 синхронизации и блок 21 запрета. Для формирования каждого выходного отсчета необходимо просуммировать симметриЧно расположенные выборки входных. сигналов, сформировать произведения полученных сумм на знаки соотв. коэф., из которых сформировать M/2+1 частичных сумм входных выборок, умножить их на соотв. приращения коэф. и результаты сложить между собой. Формирование сумм симметрично расположенных входных выборок необходимо начинать с суммы (и-М/2)-й выборки с нулем, а заканчивать суммой и-го и (n-M)-ro отсчетов. 2 ил. 1 табл.

135262 Изобретение относится к радиотех- нике и может быть использовано для фильтрации сигналов, задаваемых цифровым кодом. .)

Цель изобретения — расширение функциональных возможностей путем реализации передаточной функции четного порядка.

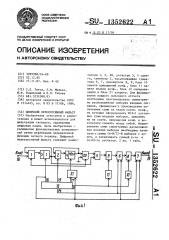

На фиг. 1 представлена электрическая структурная схема цифрового нерекурсивного фильтра; на фиг. 2 схема блока синхронизации.

Цифровой нерекурсивный фильтр (фиг. 1) содержит первый и второй коммутаторы 1 и 2, первый и второй регистры 3 и 4 сдвига, сумматор 5, первый и второй накапливающие сумматоры 6 и 7, второй и первый умножители 8 и 9, блок 10 памяти приращений коэффициентов, блок 11 памяти знаков коэффициента, блок 12 синхронизации, адресный выход 13 блока синхронизации, установочный выход 14 блока синхронизации, первый управляю- 25 щий выход 15 блока синхронизации, второй управляющий выход 16 блока 15 синхронизации, тактовый выход 17 блока синхронизации, вход 18 цифрового нерекурсивного фильтра, выход

19 цифрового нерекурсивного фильтра, третий коммутатор 20 и блок 21 запрета.

Блок 12 синхронизации (фиг. 2) содержит счетчик 22 по модулю M/2+1, дешифратор 23, элемент И 24 и генератор 25 тактовых импульсов.

Ц („= ) о;Х„; .

i--О

Цифровой нерекурсивный фильтр работает следующим образом.

Для определения алгоритма работы предлагаемого фильтра исходным является алгоритм свертки

Учитывая, что коэффициенты фильтрации нерекурсивных фильтров, как правило, симметричны, выражение (1) для фильтра четного порядка можно представить в виде

hlj2-1

Выражение (2) можно преобразовать путем замены весовых коэффициентов

2 2 д; их приращениями д а, = а; - а;, и их знаками sign (а;) М!2- I ьо, +sign(а, =o

) (X „; + Хлм,,)+

+ sign(a„< )X ьа,. (3) Первый и второй регистры 3 и 4 сдвига осуществляют хранение и через первый и второй коммутаторы 1,и

2. циклический сдвиг данных, хранящихся в них. Через коммутаторы 1 и 2 в регистры 3 и 4 сдвига производится также запись новых данных соответственно с входа 18 и первого регистра

3 сдвига. Сумматор 5 производит суммирование симметрично расположенных входных выборок, которые с номерами от и до и-M/2 содержатся в первом регистре 3 сдвига, а с номерами с и-M/2 до и-M — во втором регистре 4 сдвига. Первый умножитель 9 на +1 производит умножение сумм, поступающих с выхода сумматора 5, на знаки соответствующих коэффициентов, которые хранятся в блоке 11 памяти знаков коэффициентов. Полученные произведения накапливаются в первом накапливающем сумматоре б в виде частичных сумм, которые затем умножаются во втором умножителе 8 на малоразрядные приращения коэффициентов, хранящихся в блоке 10 памяти приращений коэффициентов, а полученные произведения накапливаются во втором накапливающем сумматоре 7.

В начале каждого цикла вычисле4 ния сигнал, поступающий с установочИз выражения (3) следует, что для формирования каждого выходного отсчета, необходимо просуммировать симметрично расположенные выборки входных сигналов (при этом и-M/2-я выборка суммируется с нулем), сформировать произведения полученных сумм на знаки соответствующих коэффициентов,из.которых затем сформировать

И/2+1 частичных сумм входных выборок, умножить их на соответствующие приращения коэффициентов и результаты сложить между собой. При этом формирование сумм симметрично расположенных входных выборок необходимо начинать с суммы и-М/2-й выборки с нулем, а заканчивать суммой n-ro u и-М-го отсчетов.

3 i3 ного выхода 14 блока 12 синхронизации, производит обнуление первого и второго накапливающих сумматоров 6 и 7.

Запись в регистры 3 и 4 сдвига организована таким образом, что в начале каждого цикла вычисления в правой (выходной) ячейке памяти первого регистра 3 сдвига хранится значение п-М/2-го входного отсчета, а в каждой ячейке левее - значение отсчетов с номерами на единицу меньше.

В то же время в правой ячейке памяти второго регистра 4 сдвига записано значение и-И+1-го входноro отсчета, в следующей ячейке левее — и-M/2-ro отсчета и в каждой следующей ячейке левее — отсчеты с номерами на единицу больше. В первом такте каждого цикла вычисления сигнал, поступающий с первого управляющего выхода

15 блока 12 синхронизации, переводит первый, второй и третий коммутаторы 1, 2 и 20 в режим коммутации сигналов соответственно с входа 18, выхода первого регистра 3 сдвига и входа логического нуля цифрового нерекурсивного фильтра. В конце пер— вого такта вычисления в первую ячейку памяти первого регистра 3 сдвига записывается значение текущего входного отсчета, а из последней ячейки выводится значение и-M/2-го отсчета, которое записывается в первую ячейку второго регистра 4 сдвига, из последней ячейки которого выводится значение и-М+1-го отсчета. В течение

3!) ),. м, г м)г-<

sign(a„, )Х„, sign(ai )», =м(г-(52622 4 первый коммутатор 1 в режим коммутации сигнала с выхода первого регистра 3 сдвига, а второй и третий коммутаторы 2 и 20 — в режим комму5 тации сигнала с выхода второго регистра 4 сдвига. В течение M/2-1-го такта вычисления под действием тактовых сигналов, поступающих с тактового выхода 16 блока 12 синхронизации и выхода блока 21 запрета на тактовые входы соответственно первого и второго регистров 3 и 4 сдвига, в них происходит циклическая перезапись информации. Во время последнего N/2+1-го такта вычисления тактовый сигнал поступает только на тактовый вход первого регистра 3 сдвига, а.во втором регистре 4 сдвига информация остается неизменной.

В таблице приведено расположение входных n-i-х отсчетов (указано значение i) в каждом из тактов

n-ro цикла вычисления в регистрах

3 и 4 сдвига для фильтра восьмого порядка,,а также номера отсчетов, поступающих на вход сумматора 5.

В течение M/2+1 тактов каждого цикла вычисления на выходе первого

30 накапливающего сумматора 6 последовательно формируются частичные суммы: же первого такта на входы сумматора

5 поступают значения и-М/2-го отсчета с выхода первого регистра 3 сдвига и значение нуля с выхода третьего коммутатора 20. Поэтому в конце первого такта вычисления в регистр первого накапливающего сумматора 6 запишется произведение значения и-М/2-ro отсчета на знак И/2 коэффициента. Одновременно данное произведение умножится во втором умножителе 8 на значение приращения коэффициента

6 a )»(q и полученное произведение за- . пишется во второй накапливающий сумматор 7.

Начиная с начала второго такта вычисления и до конца последнего такта вычисления сигнал, поступающий с первого управляющего выхода 15 блока 12 синхронизации на управляющие входы первого, второго и третьего коммутаторов 1, 2, 20, переключает

»(у

40 м(г-

sign(a„, )Х „, + nips(a; )" которые во втором умножителе 8 умножаются на малоразрядные приращения коэффициентов: ьа м(г, ь а„„г, ь о. поступающие из блока 10 памяти приращений коэффициентов синхронно с частичными суммами с выхода первого накапливающего сумматора 6.

Вычисляемые произведения в течение

55 М/2+1 тактов вычисления суммируются во втором накапливающем сумматоре 7, где в конце последнего

M/2+1-го такта каждого цикла вычисления формируется очередной отсчет

Номер цикла

Номер такта ды тора 5

) 2

8888

2 3 4 1 8 7 6 5 9

2 3 4 8 7 6 5 . 9

0 I 2 3 4 8 7 6 5 и-1

Ноль

3 0 1 2 5 4 8 7 6

2 3 О 1 6 5 4 8 7

7 6 5 .4 8

7 6 5 4 8

3 0

2 3

0 1 и+1

Ноль

5 135 выходного сигнала Уп поступающий на выход 19 цифрового нереверсивного фильтра. С приходом следующего входного отсчета Х „„ цикл вычисления повторяется.

Формула изобретения

Цифровой нерекурсивный фильтр, содержащий последовательно соединенные первый коммутатор, первый вход которого является входом цифрового нерекурсивного фильтра, первый регистр сдвига, выход которого соединен с вторым входом первого коммутатора, второй коммутатор и второй регистр сдвига, выход которого соединен с вторым входом второго коммутатора, последовательно соединенные сумматор, первый вход которого соединен с выходом первого регистра сдвига, первый умножитель, первый накапливающий сумматор, второй умножигель и второй накапливающий сумматор, выход которого является выходом цифрового иерекурсивного фильтра, блок памяти знаков коэффициентов, выход которого соединен с вторым входом первого умножителя, блок памяти приращений коэффициентов, выход которого соединен с вторым входом второго умножителя, а также блок синхрони2622

6 зации, адресный выход которого соединен с адресными входами блока памяти знаков коэффициентов и блока памяти приращений коэффициентов, установочный выход соединен с установочными входами первого и второго накапливающих сумматоров, тактовый выход соединен с тактовыми входами пер; ваго регистра сдвига и первого и второго накапливающих сумматоров, а первый управляющий выход соединен с управляющим входом первого коммутатора, отличающийся тем, что, с целью расширения функциональных возможностей путем реализации передаточной функции четного порядка, в него введены третий коммутатор, первый вход которого соединен с выхо2О дом второго регистра сдвига, второй вход соединен с входом логического нуля цифрового нерекурсивного фильтра, управляющий вход соединен с первым управляющим выходом блока

25 синхронизации, а выход — с вторым входом сумматора, и блок запрета, вход которого соединен с вторым уп-. равляющим выходом блока синхронизации, а выход — с тактовым входом 0 второго регистра сдвига, при этом первый управляющий выход блока синхронизации соединен с управляющим входом второго коммутатора.

l352622

17 авиа 2

Составитель Э. Борисов

Техред М.Ходанич Корректор А. Обручар

Редактор А. Лежнина

Заказ 5575/55 Тираж 900

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г . Ужгород, ул. Проектная, 4