Цифровой регулятор фазы гармонического сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может быть использовано при формировании гетеродинных, опорных и контрольных сигналов в фазовых радиотехнических системах. Цифровой регулятор содержит фазовращатель 1 (на 90), цифровые аттенюаторы 2 и 3, фазоинверторы 5 и 6, ключи 7-10, сумматор 11, тригонометрический преобразователь cos 16, формирователь 17 константы и анализатор 18 кода. Введение цифрового аттенюатора 4, коммутатора 12, умножителей 13 и 14 тригонометрического преобразователя tg I5 и образование новых функциональных связей повышает точность регулирования фазы. 2 ил. (Л ибш со ел 4 СО ГО

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) А1 (д11 4 G 01 R 25/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

Aar

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3908743/24-21 (22) 05. Об. 85 (46) 23. 11.87. Бюл. № 43 (72) M. И. Малыкин (53) 621.3)7.77(088.8) (56) Авторское свидетельство СССР № 1104465, кл. G 05 В 11/Ol, 1983.

Авторское свидетельство СССР

¹ 447678, кл. G 01 R 15/00, 1 976. (54) ЦИ@РОВОЧ РЕГУЛЯТОР АЗ!.! ГАРМОНИЧЕСКОГО СИГНАЛА (57) Изобретение относится к радиотехнике и может быть использовано при формировании гетеродинных, опорных и контрольных сигналов в фазовых радиотехнических системах. Цифровой регулятор содержит фазовращатель 1 (на 90 ), цифровые аттенюаторы 2 и

3, фазоинверторы 5 и б, ключи 7-10, сумматор 11, тригонометрический преобразователь соя !6, формирователь

17 константы и анализатор 18 кода.

Введение цифрового аттенюатора 4, коммутатора 12, умножителей 13 л 14 тригонометрического преобразователя

tg 15 и образование новых функциональных связей повьппает точность регулирования фазы. 2 ил.

3354132

20

35

45

Изобретение относится к радиотехнике и может быть использовано при формировании гетеродинных, опорных и контрольных сигналов в фазовых радиотехнических системах.

Целью изобретения является повышение точности регулирования фазы.

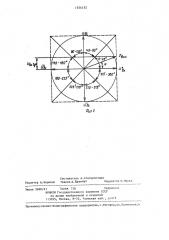

На фиг.1 изображена структурная электрическая схема регулятора фазы; на фиг,2 — векторная диаграмма, поясняющая работу регулятора фазы и его преимущество перед известным регулятором.

Цифровой регулятор фазы гармонического сигнала содержит фаэовращатель 1 (на 90 ), цифровые аттенюаторы 2 — 4, фазоинверторы 5 и 6, ключи

7 — 10, сумматор 11, коммутатор 12, умножители 13 и 14, тригонометрические преобразователи tg 15 и сов 16, формирователь 17 константы и анализатор 18.кода. Вход и выход фазовращателя 1 (на 90 ) соединены с входами цифровых аттенюаторов 2 и 3 соответственно. Выход цифрового аттенюатора 2 соединен с входом ключа 7 непосредственно и с входом ключа 8 через Ааэоинвертор 5. Выход цифрового аттенюатора 3 соединен с входом ключа 10 непосредственно и с входом ключа 9 через Фазоинвертор 6. Выходы всех ключей соединены с входами сумматора 11, выход которого соединен с входом цифрового аттенюатора 4, Вход анализатора 18 кода, являющийся входом управления устройства, соединен с входами тригонометрических преобразователей 15 и 16, а его выходы подключены к входам управления коммутатора 12 и ключей 7 — 10 соответственно,. Выход тригонометрического преобразователя 16 соединен с первым входом умножителя 14, выход которого соединен с входом управления цифрового; аттенюатора 4. Выход формирователя 17 соединен с вторыми входами перемножителей 13 и 14 и с входом коммутатора 12. Выходы 19 и

20 коммутатора 12 соединены с входа-. ми управления цифровых аттенюаторов

3 и 2 соответственно. При этом коммутатор имеет входы 21 и 22, а анализатор 18 — выходы 23 — 27, Устройство работает следующим образом.

На вход фазовращателя 1, являющийся сигнальным входом устройства; поступает сигнал П „ ь„ cos63ts начальную фазу которого необходимо изменить. На вход анализатора 18 поступает код N< величины смещения фазы.

Код Й одновременно поступает на входы преобразователей 15 и 16. В зависимости от получетверти круга, в которой находится значение q, анали— затор 18 формирует пять логических команд (О или 1), поступающих на управляющие входы коммутатора 12 и ключей 7 — 10.

В преобразователях 15 и 16 код Н, преобразуется соответственно в коды

Ntg q тангенса g H Ncos q косинуса q .

Эти коды в умножителях 13 и 14 пе, n ремножаются с кодом Б =2 -1, где n— количество разрядов цифровых аттенюаторсв, поступающим с выхода формирователя 17. Код N Ntgq с выхода умножителя 13 поступает на вход 22 коммутатора 12, а код Y, Ncosq с выхода умножителя 14 подается на вход управления цифрового аттенюатора 4.

На вход 21 коммутатора 12 поступает код N с выхода формирователя 17.

Коммутатор 12 работает таким образом, что при поступлении на его управляющий вход логической "1" вход 21 подключается к выходу 19, а вход 22 — к выходу 20, при поступлении логического "0" вход 21 подключается к выходу 20, а вход 22 — к выходу 19. Таким образом, в зависимости от значения фазы с, на один иэ цифровых аттенюаторов 2 и 3 поступает код N обеспечивая его коэффициент передачи, равный единице, а на второй цифровой аттенюатор поступает код N,Ntgcp, обеспечивая его коэффициент передачи, равный tgq>.

Входной сигнал U „ поступает на вход цифрового аттенюатора 2, а

О= % сдвинутый на 90 сигнал U „

= U „ sin u t с выхoдa фазовращателя

1 поступает на вход аттенюатора 3.

На выходе аттенюаторов 2 и 3, в зависимости от состояния коммутатора 12, имеют место сигналы U „(ц )

М.

= Пвх tgVcos yt и UBx либо UB u

ВХ X

Ньх (c{>) = 15Bx сЩз. па, Hs выходах фазоинверторов 5 и 6, меняющих фазу

B сигнала на 180, соответственно устанавливаются сигналы U,„(ц) 1cosut H UBX 1.1 S1nut лиUB„(q) = Нь„1.Щз1.пи и Uz, =

-U,„„cosut.

1

Таким образом, на входах ключей, в зависимости от состояния коммутатора 12, могут иметь место следующие сигйалы: на входе ключа 7: U» (cg) или U,„; на входе ключа 8: UB„(cp) или Ц „; на входе ключа 9: U или

U x (q), на входе ключа 10: Б „или Вх (Ч ) °

Ключи открыты, если на их управляющие входы поступает логическая

"1" и закрыты при поступлении логического "0". На сумматор 10 посту— пают всегда два из восьми указанных векторов, которые в сумме дают сигнал с заданным сдвигом фазы Ч, т.е. на выходе сумматора 11 образуется сигнал Уьыу = 13ьык сов (+Ч) ° туда сигнала V„„= V, -Птгд д

=Ущ„ /cosy. На выходе аттенюатора 4, коэААициент передачи которого равен

cos(f, сигнал становится равным Б,ы„ =

=U < cos (Qt+9), и его амплитуда Uex Hå эависит от величины (p

Принцип работы устройства поясняется векторной диаграммой (фиг.2).

Тригонометрический круг разделяется

0 на восемь равных частей по 45 . В каждой части по острому углу у и прилежающему катету, являющемуся радиусом круга, строится восемь прямоугольных треугольников. Меняя в каждом треугольнике величину противоле— жащего катета в пределах 0-1, можно, а менять значение Оу в пределах 0-45

Если величина прилежащего катета равна единице, то величина противолежащего катета, равная tgq, будет соот— ветствовать углу (f . Меняя направле% ние ортогональных векторов U „и Пц„и величину одного из них в пределах

0-1, можно менять фазу результирующего вектора в пределах 0-360

При этом максимальная погрешность

dg, установки фазы q определяется выражением

6У,,=

1+tg где о — относительная величина дис354132

50 крета изменения амплитуды одного из ортогональных векторов.

Формула изобретения

Пифровой регулятор фазы гармонического сигнала, содержащий фазовращатель, вход которого является входом устройства, два цифровых аттенюатора, два фазоинвертора, четыре ключа, сумматор, входы которого соединены с выходами ключей, и тригонометрический преобразователь cos причем вход и выход фазовращателя соединены с входами первого и второго цифровых аттенюаторов соответственно, выход первого фазового аттенюатора соединен с входом первого ключа непосред-. ственно и с входом второго ключа через первый фазоинвертор, а выход второго цифрового аттенюатора соединен непосредственно с входом четвертого ключа.и с входом третьего ключа через второй фазоинвертор, о т л и— ч а ю шийся тем, что, с целью повышения точности регулировки фазы, в него введены коммутатор, выходы которого соединены с входами управления первого и второго цифровых аттенюаторов соответственно, третий циф вЂ, ! ровой аттенюатор, вход которого соединен с выходом сумматора, первый умножитель, выход которого соединен с первым входом коммутатора, второй умножитель, первый вход которого соединен с выходом тригонометрического преобразователя cos, а выход подключен к входу управления третьего цифрового аттенюатора, тригонометрический преобразователь tg выход которого соединен с первым входом перво го умножителя, формирователь константы, выход которого соединен с вторыми входами первого и второго умножителей и с вторым входом коммутатора, и анализатор кода, вход которого соединен с входами тригонометрических преобразователей cos и tg, а выходы подключены к входам управления коммутатора, первого, второго, третьего и четвертого ключей соответственно °

1354132

Составитель А. Статоростина

Редактор А. Ворович Техред А. Кравчук Корректор И.Муска

Заказ 5690/41 Тираж i 30 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие,г.ужгород,ул.Проектная,4