Устройство для контроля цифровых узлов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля узлов. Цель изобретения - увеличение быстродействия за счет обеспечения организации контроля между рабочими интервалами времени в масштабе реального времени. Устройство содержит мультиплексор , коммутатор, дешифратор конечного набора, дешифратор эталанной сигнатуры, элемент запрета, три элемента И, элемент ИЛИ-НЕ, формирователь импульса, два элемента задержки, элемент ИЛИ, генератор псевдослучайной последовательности и сигнатурный анализатор. Достоверность работоспособности аппаратуры, как правило, обеспечивается периодическим тестовым контролем, который дополняет оперативный аппаратный контроль функционирования аппаратура. Периодический тестовой контроль требует специальным образом организованного программного обеспечения и навязывает принудительное структурное и временное изменение процесса функционирования основной аппаратуры системы. В предлагаемом изобретении контроль работоспособности аппаратуры осуществляется в паузы между рабочими интервалами, не требуя специального программного обеспечения и не изменяя временной диаграммы процесса функционирования. Кроме того, полнота тестовой проверки с помощью встроенных аппаратных .,.t средств может быть существенно вьш1е полноты традиционных программных тестовых проверок. Использование изобретения при проектировании интегральных схем комбинационного типа (например, программируемых логических матриц) позволяет создать элементную базу проектирования высоконадежных и наиболее ответственных узлов вычислительной техники, в которых использование ложной информации для управления недопустимо. Таким образом, предлагаемое комбинационное устройство с встроенным контролем может быть использовано в составе высоконадежных систем, обеспечивающих повышенный уровень достоверности вьщаваемой информации . 2 ил. (Л со ел N СО D1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (gg 4 С 06 F 11/26

5 А1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 4064792/24-24 (22) 05.05.86 (46) 23.11.87. Бюл. 1(- 43 (71) Московский инженерно-физический институт (72) Н.О.Атовмян, Е.Ф.Березкин, Ю.А.Дашковский и Н,В.Ефремов (53) 681.3(088.8) (56) Авторское свидетельство СССР .

У 1037261, кл. С 06 F 11/26, 1983.

Авторское свидетельство СССР

У 1179348, кл. С 06 F 11/26, 1984. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ

УЗЛОВ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля узлов.

Цель изобретения — увеличение быстродействия за счет обеспечения организации контроля между рабочими интервалами времени в масштабе реального времени. Устройство содержит мультиплексор, коммутатор, дешифратор конечного набора, дешифратор эталонной сигнатуры, элемент запрета, три элемента И, элемент ИЛИ-НЕ, формирователь импульса, два элемента задержки, элемент ИЛИ, генератор псевдослучайной последовательности и сигнатурный анализатор. Достоверность работоспособности аппаратуры, как правило, обеспечивается периодическим тестовым контролем, который дополняет оперативный аппаратный контроль функционирования аппаратура. Периодический тестовой контроль требует специальным образом организованного программного обеспечения и навязывает принудительное структурное и временное изменение процесса функционирования основной аппаратуры системы. В предлагаемом изобретении контроль работоспособности аппаратуры осуществляется в паузы между рабочими интервалами, не требуя специального программного обеспечения и не изменяя временной диаграммы процесса функционирования.

Кроме того, полнота тестовой проверки с помощью встроенных аппаратных средств может быть существенно выше Ф полноты традиционных программных тес- рр товых проверок. Использование изобре- V Ф тения при проектировании интегральных схем комбинационного типа (например, с программируемых логических матриц) позволяет создать элементную базу проектирования высоконадежных и наиОавй более ответственных узлов вычисли- СИ тельной техники, в которых использо- Ql вание ложной информации для управления недопустимо, Таким образом, предлагаемое комбинационное устройство с встроенным контролем может быть использовано в составе высоконадежных систем, обеспечивающих повышенный уровень достоверности выдаваемой информации. 2 ил.

1354195

Изобретение относится к вычислительной технике и может быть использовано в высоконадежных системах, обеспечивающих повышенный уровень до5 стоверности выдаваемой информации.

Цель изобретения — увеличение быстродействия за счет обеспечения организации процесса контроля между рабочими интервалами в масштабе реаль- 1п ного времени.

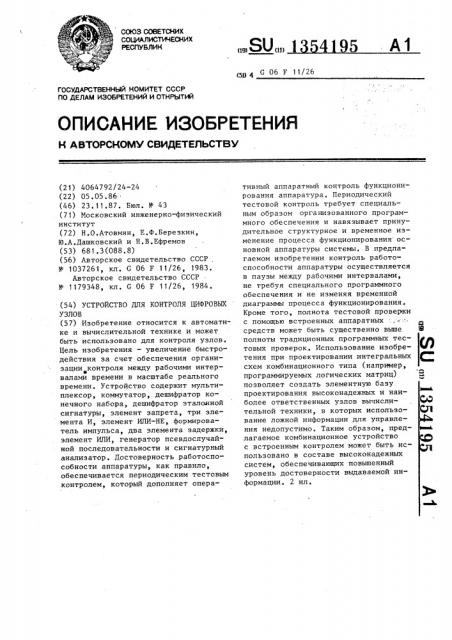

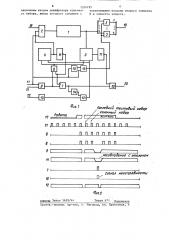

На фиг.1 приведена блок-схема устройства, на фиг.2 — временные диаграммы работы устройства.

Устройство содержит контролируемый узел 1, мультиплексор 2, коммутатор 3 с тремя состояниями, генератор 4 псевдослучайных чисел, сигнатурный анализатор 5, дешифратор б конечного набора, элемент 7 запрета, 2п элементы И 8-10, дешифратор 11 эталонной сигнатуры, элемент ИЛИ-НЕ 12, формирователь 13 импульса, элементы

14 и 15 задержки, элемент ИЛИ 16, вход 17 задания режима работы,.инфор- 25 мационный вход 18, выход 19 признака отклика, выход 20 ошибки, вход 21 синхронизации, вход 22 начальной установки.

Контроль работоспособности узла 1 производится во время пауз между рабочими интервалами. С этой целью к узлу 1 подключается мультиплексор 2, коммутатор 3 с тремя состояниями °

Сигнал на входе 17 осуществляет иден35 тификацию рабочего режима и режима контроля работоспособности. При подаче нуля на вход 17 входная информация с информационного входа 18 поступает на узел 1, а выходная информация че- 4О рез открытый коммутатор 3 — на выход

19,-При подаче единицы на вход 17 реализуется режим контроля работоспособности узла 1.

Генератор 4 может вырабатывать заданные двоичные наборы, составляющие минимальный полный тест, а сигнатурHblH анализатор 5 обнаруживает заданное множество векторов или матриц ошибок реакций контролируемого узла

1, обусловленных перечнем его неисправностей.

Дешифратор 6 конечного набора устанавливает момент спроса тактовым импульсом через элемент 7 запрета и

55 элемент И 10 состояния дешифратора

11 эталонной сигнатуры. Единичный импульс на выходе 20 свидетельствует а том„ что эталонная сигнатура не совпадает с фактической сигнатурой, выработанной в результате проверки.

Элемент И 8 предназначен для того, чтобы после свертки анализатором 5 реакции узла 1 на последний тестовый набор блокировать переключение гене- .— ратора 4 и анализатора 5.

Элемент И 9 в режиме контроля работоспособности пропускает тактовые импульсы с входа 21 на входы элемента

И 8 и элемента 7 запрета.

Элемент ИЛИ вЂ 12 предназначен для начальной установки генератора 4 и анализатора 5. Начальная установка производится через формирователь 13 импульса при появлении положительного перепада на входе 27 либо импульсом опроса состояния дешифратора 11 эталонной структуры, задержанным элементом 14 на длительность тактового импульса.

Элемент 15 задержки и элемент ИЛИ

16 выполняют функции дифференцированной задержки сигнала, подаваемого на вход 17. Причем они задерживают только отрицательный фронт этого сигнала на время срабатывания узла 1. Эта задержка требуется для того, чтобы при переходе из режима контроля работоспособности в рабочий режим разрешить работу коммутатора З.лишь после появления на их входах реакции узла 1 на первый рабочий набор, Устройство работает следующим образом.

При включении питания генератор 4 и анализатор 5 через формирователь 13 и элемент ИЛИ-HE 12 устанавливаются в исходное состояние, Это обеспечивает невозможность выполнения усеченной последовательности тестовой проверки и, следовательно, появления ложного сигнала неисправности ° Исходным состоянием для генератора 4 является первый тестовый набор, а для анализатора нулевой код °

В рабочем режиме (сигнал входа 17 равен нулю) устройство функционирует обычным образом — мультиплексор 2 коммутирует на вход узла 1 входные данные входа 18, а коммутатор 3 с тремя состояниями выход узла 1 на выход 19. Элемент И 9 не пропускает тактовые импульсы с входа 21 на генератор 4 и анализатор 5.

С приходом запрещающего потенциала (сигнал входа 17 равен единице) мультиплексор 2 переключает вход узла 1 з 13 на выход генератора 4, коммутатор 3 переходит в состояние высокого импеданса и элемент И 9 пропускает тактовые импульсы с входа 21 через элемент И 8 на синхровходы генератора 4 и анализатора 5.

Далее запускается режим контроля работоспособности, в котором на каждый тактовый импульс генератор 4 подготавливает подачу на вход узла 1 очередного тестового набора, а анализатор 5 воспринимает реакцию узла

1 на предыдущий тестовый набор.

В момент, когда генератор 4 выработает конечный набор, который всегда следует за последним тестовым набором, анализатор 5 сворачивает реакцию узла 1 на последний тестовый набор.

Дешифратор 6 распознает конечный набор, и на его выходе появляется низкий потенциал, который блокирует прохождение следующего тактового импульса через элемент И 8 на синхровходы генератора 4 и анализатора 5. В то же время низкий уровень сигнала на выходе дешифратора 6 разрешает прохождение следующего тактового импульса через элемент 7 запрета на вход элемента И 10. Если на выходе дешифратора 11 эталонной сигнатуры есть низкий потенциал, то узел исправен, и на выходе 20 остается низкий потенциал. В противном случае (в узле появилась неисправность), сигнатура отличается от эталонной и на выходе 20 появляется единичный импульс, свидетельствующий о наличии в схеме неисправности.

Импульс опроса состояния дешифратора 11 эталонной сигнатуры, задержанный элементом 14 на длительность тактового импульса, через элемент

ИЛИ-НЕ 12 устанавливает генератбр 4 и анализатор 5 в исходное состояние, и цикл контроля повторен.

В результате узел 1 контролируется в интервалы времени, когда оно простаивает. При этом в зависимости от длины пауз контроль работоспособности проводится многократно циклически или квантами, каждый раз продолжая проверку с того тестового набора, на котором зафиксировано последнее прерывание рабочим режимом.

Формула и з обретения

Устройство для контроля цифровых узлов, содержащее генератор псевдослучайных чисел, сигнатурный анали40

55 второй элемент задержки с вторым входом элемента ИЛИ, выход которого соединен с управляющим входом коммутатора, выход которого является выходом признака отклика устройства, информационный вход которого соединен с первым информационным входом мультиплексора, выход которого соединен с выходом устройства для подключения ко входам контролируемого узла, информационный вход коммутатора является входом устройства для подключения к выходу контролируемого узла и соединен с информационным входом сигнатурного анализатора, вход синхронизации которого соединен с выходом второго элемента И и входом синхронизации генератора псевдослучайных чисел, выход которого соединен с вторым информационным входом мультиплексора и инфор54195 затор, первый элемент задержки, коммутатор, мультиплексор, три элемента

И, формирователь импульса, о т л и—

5 ч а ю щ е е с я тем, что, с целью увеличения быстродействия за счет обеспечения организации процесса контроля между рабочими интервалами в масштабе реального времени, устрой10 ство содержит дешифратор конечного

1 набора, дешифратор эталонной сигнатуры, элемент запрета, элемент ИЛИ-НЕ, элемент ИЛИ, второй элемент задержки, причем синхровход устройства соединен

15 с информационным входом первого элемента И, выход которого соединен с информационным входом второго элемента И и информационным входом элемента запрета, выход которого соединен с

20 управляющим входом третьего элемента

И и через первый элемент задержки с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом формирователя импульса, вход которого соединен с входом начальной установки устройства, .выход элемента ИЛИ-НЕ соединен с входом разрешения генератора псевдослучайных чисел и сигнатурного анализатора, выход которого соединен с информационным входом дешифратора эталонной сигнатуры, выход которого соединен с информационным входом третьего элемента И, выход которого является выходом признака ошибки устройства, вход задания режима работы которого соединен с управляющим входом первого элемента И, с управляющим входом мультиплексора с первым входом элемента ИЛИ и через я?сФГЪий m моною

Сигнал неисаробиости тираж 671 Подписное дщццщ Заказ 5695/44

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Б

1354195 б мационным входом дешифратора конечно- управляющими входами второго элемента го. набора, выход которого соединен с И и элемента запрета.