Устройство для ввода в цвм инициативных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам ввода информации, и может быть использовано для приема инициативных сигналов по входным дискретным каналам. Целью изобретения является уменьшение объема оборудования устройства. Устройство содержит блок 3 управления, блок 4 нормализации , блок 5 компенсации, двухуровневый компаратор 6, компаратор 7, интегратор 8, регистр 9, триггер 10. Устройство выделяет инициативньм сигнал по 48-м входным каналам и вырабатывает сигнал прерывания, по которому ЦВМ считывает входную информаа (Л бь/х: СХ) ел со 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

8 А1 (19) (11) (51) 4 G 06 F 1 3/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕтЕЛЬСтВУ иг.

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4037742/24-24 (22) 04.02.86 (46) 23.11.87. Бюл. )) 43 (72) Т.А.Курдюкова, В,T.Диденко и В.Е.Столяренко (53) 68 1.3 (088.8) (56) Авторское свидетельство СССР

У 1314345, кл. G 06 F 13/00, 15.06.86.

Модуль ввода инициативных сигналов А622-4, Руководство по эксплуатации 3.035.018 РЭ. (54) УСТРОЙСТВО ДЛЯ ВВОДА В ЦВМ ИНИЦИАТИВНЫХ СИГНАЛОВ (57) Изобретение относится к вычислительной технике, в частности к устройствам ввода информации, и может быть использовано для приема инициативных сигналов по входным дискретным каналам, Целью изобретения является уменьшение объема оборудования устройства. Устройство содержит блок 3 управления, блок 4 нормализации, блок 5 компенсации, двухуровневый компаратор 6, компаратор 7, интегратор 8, регистр 9, триггер 10.

Устройство выделяет инициативный сигнал по 48-м входным каналам и вырабатывает сигнал прерывания, по которому ЦВМ считывает входную информациюе 1 запв ф лыу 3 иле

1354 198

?0

30

40 г<

Изобретение относится к вычислительной технике и может быть использовано для приема в УВМ инициативных дискретных сигналов.

Цель изобретения — сокращение объема оборудования устройства.

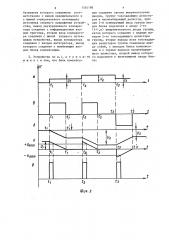

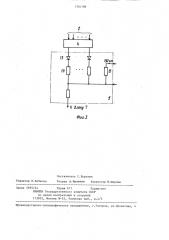

На фиг. 1 приведена структурная схема устройства; на фиг.2 — временная диаграмма, поясняющая работу схемы; на фиг.3 — структура блока компенсации.

Устройство содержит вход 1 для подключения управляющего выхода ЦВМ, вход 2 для подключения выхода источника инициативных сигналов, блок 3 управления, блок 4 нормализации, блок 5 компенсации, двухуровневый компаратор 6, компаратор 7, интегратор 8, регистр 9, триггер 10, выход

11 для подключения входа данных ЦВМ и выход 12 для подключения входа прерывания ЦВМ. Блок 5 компенсации (фиг.3) содержит группу 13 выпрями.тельных диодов, группу 14 токозадающих резисторов, масштабирующий резистор 15.

Устройство работает следующим образом.

В исходном состоянии триггер 10 (фиг.1) сброшен, на выходе компаратора 6 сигнал отсутствует. ,Сигналы от датчиков поступают по входу 2 на входы блока 4 нормализации, приводятся к унифицированному уровню и поступают на входы блока 5 компенсации и на входы регистра 9 °

Эквивалентное (весовое) изменение напряжения при включении — отключении датчиков показано на фиг,2а, В момент поступления сигнала на вход блока 5 компенсации на выходе этого блока в момент времени t< (фиг.2г) происходит скачок напряжения U,, который поступает на первый (прямой) вход компаратора 7. С выхода компаратора 7 сигнал (фиг.2б) поступает на вход интегратора 8, на выходе которого (фиг.2в) за время (t< — t<) напряжение достигает установившегося значения U<, равного по амплитуде. напряжению, поступившему с блока 4 номализации, но противоположной полярности. С выхода интегратора 8 напряжение (фиг.2в) поступает на вычитающий вход блока 5 компенсации, в котором за время (t, — e ) происходит компенсации входного сигнала U< фиг.2r).

В момент времени t на выходе двухуровневого компаратора 6 формируется инициативный сигнал (фиг.2д) .

Длительность импульса этого сигнала зависит от настройки порога отпускания компаратора 6 (+ U „ или — U фиг.2г). С выхода компаратора 6 этот сигнал взводит триггер 10, который выдает сигнал запроса, поступающий на вход прерывания ЦВМ, После получения сигнала запроса ЦВМ выдает управляющие сигналы на вход 1, по которым блок 3 управления формирует строб выдачи данных. Этот сигнал стробирует регистр 9 и на выход 11 данных выдается информация о состоянии входов.

После этого ЦВМ выдает сигнал, который через блок 3 управления сбрасывает триггер 10. Устройство переходит в исходное состояние.

На фиг.2 показаны моменты включения t< и отключения других датчиков, Процесс формирования инициативного сигнала (фиг.2д) и запись информации в регистр 9 аналогичен описанному.

Фор м ул а и з ° о б р е т е н и я t. Устройство для ввода в ЦВМ инициативных сигналов, содержащее блок нормализации, регистр, блок управления и триггер, причем вход блока нормализации соединен c входом устройства для подключения источника инициативных сигналов, входы синхронизации триггера и регистра соединены с первым выходом блока управления, второй выход которого соединен с единичным входом триггера, вход блока управления подключен к входу устройства для подключения управляющего выхода ЦВК, выходы триггера и регистра соединены с выходами устройства для подключения соответственно входа прерывания и входа данных ЦВМ, о т л и ч а ющ е е с я тем, что, с целью уменьшения объема оборудования устройства, в него введены блок компенсации, компаратор, двухуровневый компаратор, интегратор, причем группа суммирующих входов блока компенсации соединена с выходом блока нормализации и с информационным входом регистра, выход блока компенсации соединен с первым входом компаратора и с информационным входом двухуровневого компаратора, входы задания уровня сра1354 198 батывания которого соединены соответственно с шиной положительного и с шиной отрицательного потенциала источника опорного напряжения устрой\ 5 ства, выход двухуровневого компаратора соединен с информационным входом триггера, второй вход компаратора соединен с шиной нулевого потенциала устройства, выход компаратора 1ц соединен с входом интегратора, выход которого соединен с вычитающим входом блока компенсации.

2. Устройство по п.1, о т л и ч а- 15 ю щ е е с я тем, что блок компенса1 ции содержит группу выпрямительных диодов, группу токозадающих резисторов и масштабирующий резистор, причем i-й суммирующий вход группы входов блока подключен к аноду i-го (i=1 и) выпрямительного диода группы, катод которого соединен с первым выводом i-ro токозадающего резистора группы, вторые выводы всех токозадающих резисторов группы соединены между собой, с выходом блока компенсации и с первым выводом масштабирующего резистора, второй вывод которого подключен к вычитающему входу блока.

1354198

Составитель С. Бурухин

Редактор Н.Бобкова

Техред А. Кравчук Корректор М. Шароши

Заказ 5695/44 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, r Ужгород, ул.Проектная, 4