Амплитудный синхроселектор

Иллюстрации

Показать всеРеферат

Изобретение относится к телевидению и обеспечивает повышение точности вьщеления синхроимпульсов при воздействии низкочастотной аддитивной помехи (НАЛ). Амплитудный синхроселектор содержит буферный усилитель 1, конденсаторы 2, 16, резистор 3, ключи 4, 18, источник 5 опорного напряжения , пороговые блоки (ПБ) 6,11- 14, предварительный синхроселектор 7, дифференцируклцие блоки 8,9, логические инверторы 10, 19, блок смещения 15, операционный усилитель (ОУ) 17, элементы ИЛИ 20, 21, И 22-24. При отсутствии НАЛ половина размаха строчных синхроимпульсов на первом входе ПВ 6 совпадает с напряжением источника 5. При этом на выходе ОУ 17 формируется нулевое напряжение, на выходах ПБ 11-14 формируются равные по длительности импульсы, и открыт только ключ 18. При воздействии НАП заряд, накопленный конденсатором 16 во время строчного синхроимпульса, не равен заряду, стекающему с него. Пpи этом на выходе ОУ 17 будет-соответственно изменяться напряжение, что приводит к соотв открьшанию .ключей 4, 18 и смещению видеосигнала на входе ПБ 6. Выбором постоянной времени инвертирующего интегратора, : состоящего из резистора 3, конденсатора 16 и ОУ 17, можно добиться полной компенсации НАП на входе порогового блока 6. 1 з.п. ф-лы, 2 ил. с (Л 00 ел 4 ни 4 СО «Я.Г

СОЮЗ СОВЕТСКИХ

СОЦИАЛИС ГИЧЕСКИХ

РЕСПУБЛИК (51)4 Н 04 И 5 08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3909357/24-09 (22) 05.06.85 (46) 23.11.87. Бюл. Ф 43 (72) В.Т.Басий, В.И.Мельник, Ю.В.Сташкив и В.Я.Татарин (53) 621 ° 397 (088.8) (56) Авторское свидетельство СССР

В 621125, кл. Н 04 N 5/08, 1977. (54) АМПЛИТУДНЫЙ СИНХРОСЕЛЕКТОР (57) Изобретение относится к телевидению и обеспечивает повышение точности выделения синхроимпульсов при воздействии низкочастотной аддитивной помехи (НАП). Амплитудный синхроселектор содержит буферный усилитель

1, конденсаторы 2, 16, резистор 3, ключи 4, 18, источник 5 опорного напряжения, пороговые блоки (ПБ) 6, 1114, предварительный синхроселектор

7, дифференцирующие блоки 8,9, логические инверторы 10, 19, блок смещения 15, операционный усилитель (ОУ) „„SU„„1354443 А1

17, элементы ИЛИ 20, 21, И 22-24.

При отсутствии НАП половина размаха строчных синхроимпульсов на первом входе ПВ 6 совпадает с напряжением источника 5 ° При этом на выходе ОУ

17 формируется нулевое напряжение, на выходах ПБ 11-14 формируются равные по длительности импульсы, и открыт только ключ 18. При воздействии

НАП заряд, накопленный конденсатором

16 во время строчного синхроимпульса, не равен заряду, стекающему с него.

При этом на выходе ОУ 17 будет .соответственно изменяться напряжение, что приводит к соотв, открыванию ключей 4, 18 и смещению видеосигнала на входе ПБ 6. Выбором постоянной времени инвертирующего интегратора, . состоящего из резистора 3,. конденсатора 16 и ОУ 17, можно добиться полной компенсации НАП на входе порогового блока 6. 1 з.п. ф-лы, 2 ил.

1354443

Изобретение относится к телевизи;онной технике, в частности к телевизионной измерительной технике.

Цель изобретения — повышение точ5 ности выделения синхроимпульсов при воздействии низкочастотной аддитивной помехи.

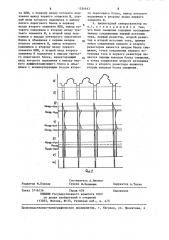

На фиг.1 приведена структурная электрическая схема амплитудного синх-1О .роселектора; на фиг.2 — временные диаграммы, поясняющие работу.

Амплитудный синхроселектор (фиг.1) содержит буферный усилитель 1, первый конденсатор 2, резистор 3, первый ключ 4, источник 5 опорного напряжения, первый пороговый блок 6, предварительный синхроселектор 7, два дифt ференцирующих блока 8 и 9, первый логический инвертор 10, пороговые блоки 20

11 — 14, блок 15 смещения, второй конденсатор 16, операционный усилитель 17, второй ключ 18, второй логический инвертор l9, элементы ИЛИ 20 и 21, элементы И 22 — 24. 25

Блок 15 смещения содержит первый источник 25 тока, первый 26 и второй

27 резисторы, второй источник 28 тока.

Амплитудный синхроселектор работает следующим образом. ЗО

Видеосигнал (фиг.2а) подается на вход буферного усилителя 1 с малым выходным сопротивлением, что позволяет исключить влияние импульсов фиксации на входные цепи предварительного синхроселектора 7. В последнем из видеосигнала выделяется синхросмесь (фиг.2б), которая попадает на вход первого дифференцирующего блока 8 и на вход первого логического инвертора 40

10, где она инвертируется.

Дифференцирующие блоки 8 и 9 выбираются с равными постоянными времени.

На выходе первого дифференцирующего блока 8 формируются рйзнополядные ко 45 роткие импульсы, соответствующие передним и задним фронтам синхроимпульсов (фиг.2в). Эти импульсы попадают на неинвертирующий вход второго порогового блока 11 и на инвертирующий вход третьего порогового блока 12, на неинвертирующий вход которого подается напряжение с выхода операционного усилителя 17, смещенное первым резистором 26 на величину -U (фиг. 2д) .

56

На инвертирующий вход второго порогового блока 11 подается напряжение с выхода операционного усилителя 17, смещенное вторым резистором 27 на величину +U (фи" 2д) Импульсы с выхода второго дифференцирующего блока.

9, которые имеют противоположную полярность относительно импульсов с выхода первого дифферекцирующего блока

8 (фиг.2г); подаются на неинвертирующий вход четвертого порогового блока

13 и на инвертирующий вход пятого порогового блока 14, на неинвертирующий вход которого подается напряжение с выхода операционного усилителя 17, смещенное на величину -П (фиг.2д).

На инвертирующий вход четвертого порогового блока 13 подается напряжение с выхода операционного усилителя 17, смещенное на величину +П „ (фиг.2д).

При отсутствии низкочастотной аддитивной помехи половина размаха строчных синхроимпульсов на первом входе порогового блока 6 точно совпадает с напряжением источника 5 опорного напряжения. На выходе операционного усилителя 17 формируется нулевое напряжение и длительности всех импульсов .на выходах пороговых блоков

1i - 14 равны. Поэтому открывается только второй ключ 18. При этом заряд, накопленный вторым конденсатором 16 во время строчного синхроимпульса, равен заряду, стекающему с него во время гасящего импульса.,За счет этого напряжение на выходе операционного усилителя 17 не изменяется.

При воздействии на видеосигнал низкочастотной аддитивной помехи заряд, накопленный вторым конденсатором 16, уже не равен заряду, стека щему с него, Напряжение на выходе операционного усилителя 17 начинает изменяться.

Если аддитивная низкочастотная помеха такова, что синхроимпульсы смещаются вниз, то на выходе операционного усилителя 17 напряжение увеличивается. Вследствие этого длительность импульсов, формируемьи вторым пороговьпч блоком 11 во время прохождения строчных синхроимпульсов, уменьшается, а длительность импульсов, формируемых третьим пороговым блоком 12 во время прохождения гасящих импульсов, увеличивается. В то же время длительность импульсов, формируемых пятым пороговым блоком 14 во время прохождения строчных сийхроимпульсов, увеличивается, а длительность импульсов, формируемых четвертым пороговым

1354443 блоком 13 во время прохождения гасящих импульсов, уменьшается. Выходы пороговых блоков, формирующих импульсы во время прохождения строчных синхроимпульсов, объединены по И первым элементом И 22, а выходы пороговых блоков, формирующих импульсы во время гасящих импульсов, объединены по И с вторым элементом И 23. Поскольку первый 8 и второй 9 дифференцирующие блоки имеют одинаковые постоянные времени то на выходах элеменl тов И 22 и 23 формируются импульсы одинаковой длительности во время прохождения строчных и гасящих импульсов соответственно.

Эти импульсы (фиг.2е) собираются по ИЛИ первым элементом ИЛИ 20 и от крывают второй ключ 18. Эти же импульсы через второй логический инвертор 19 запрещают прохождение импульсов с выхода второго элемента ИЛИ 21 на управляющий вход первого ключа 4.

После прохождения управляющих импульсов для второго ключа 18 на управляю,щий вход ключа 4 через третий элемент

И 24 и второй элемент ИЛИ 21 могут проходить импульсы с выходов четвертого 11 и пятого 12 пороговых блоков.

И если напряжение на выходе операционного усилителя 17 больше нуля, первый ключ 4 дополнительно открывается во время прохождения строчного синхроимпульса (фиг.2ж), что смещает видеосигнал на втором входе первого . порогового блока 6 вверх, т.е. в про тивофазе с низкочастотной аддитивной помехой.

Соответствующим выбором постоянной времени инвертирующего интегратора, состоящего из резистора 3, второго конденсатора 16 и операционного усилителя 17, можно добиться полной компенсации низкочастотной аддитивной помехи на входе первого порогового блока 6 и соответственно увеличения точности выделения синхроимпульсов.

Действительно, на выходе операционного усилителя 17 формируется сигнал, пропорциональный первой производной по времени от сигнала низкочастотной аддитивной помехи. Этот сигнал замешивается в видеосигнал на втором входе первого порогового блока

6 путем дополнительного подключения первого конденсатора 2 через резистор

3 и первый ключ 4 к источнику 5 опорного напряжения. Таким образом, ошиб10

l5

55 ка привязки половины размаха строчного синхроимпульса к потенциалу при-. вязки пропорциональна второй произ-. водной по времени от низкочастотной аддитивной помехи.

Формула изобретения

1. Амплитудный синхроселектор, содержащий последовательно соединенные буферный усилитель, первый конденсатор, резистор, первый ключ и источник опорного напряжения, подключенные также к первому входу первого порогового блока, выход которого является выходом амплитудного синхроселектора, а второй вход подключен к точке соединения резистора и первого конденсатора, к второму выводу которого через предварительный синхроселектор подключен вход первого дифференцирующего блока, отличающийся тем, что, с целью повышения точности выделения синхроимпульсов при воздействии низкочастотной аддитивной помехи, в него введены второй ключ, два логических инвертора, два элемента ИЛИ, с второго по пятый пороговые блоки, три элемента И, операционный усилитель, второй конденсатор, блок смещения и второй дифференцирующий блок, выход которого подключен к выходу предварительного синхроселектора через первый логический инвертор, а выход подключен к неинвертирующему входу четвертого порогового блока и инвертирующему входу пятого порогового блока, неинвертирующий вход которого объединен с неинвертирующим входом третьего порогового блока и подключен к первому выходу блока смещения, к второму выходу которого подключены инвертирующие входы второго и четвертого пороговых блоков, а вход блока смещения подключен к первому выводу второго конденсатора и выходу операционного усилителя, неинвертирующий вход которого подключен к источнику опорного напряжения, а инвертирующий вход соединен с вторым выводом конденсатора и через второй ключ подключен к точке соединения резистора и первого ключа, вход управления которого подключен к выходу третьего элемента И, первый вход которого через второй логический инвертор объединен с управляющим входом второго ключа и подключен к выходу первого элемен1354443 колер, +Исн «ер. сн е) 0опер. Мсн

Ènep.-ue «ер Исн

Uonep

e) Фиь.2

Составитель А. Иванов

Техред И,Попович

Редактор М.Бланар

Корректор А Тяско

Подписное

Заказ 5716/56 Тираж 636

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 та ИЛИ, к первому входу которого под,ключен выход первого элемента И, первый вход которого подключен к выходу пятого порогового блока и первому входу второго элемента ИЛИ, выход ко5 торого подключен к второму входу третьего элемента И, а второй вход под. ключен к выходу четвертого порогового блока и объединен с первым входом . второго элемента И, выход которого подключен к второму входу первого элемента ИЛИ, а второй вход второго элемента И подключен к выходу третьего порогового блока, инвертирующий вход которого подключен к выходу первого дифференцирующего блока и объединен с неинвертирующим входом второro порогового блока, выход которого подключен к второму входу первого элемента И.

2. Амплитудный синхроселектор по п.1, отличающийся тем, что блок смещения содержит последовательно соединенные первый источник тока, первый резистор, второй резистор и второй источник тока, причем точка соединения первого и второго резисторов является входом блока смещения, точка соединения первого источника тока и первого резистора яв- ляется первым выходом блока смещения, а точка соединения второго источника тока и второго резистора является вторым выходом блока смещения.