Преобразователь частоты в код

Иллюстрации

Показать всеРеферат

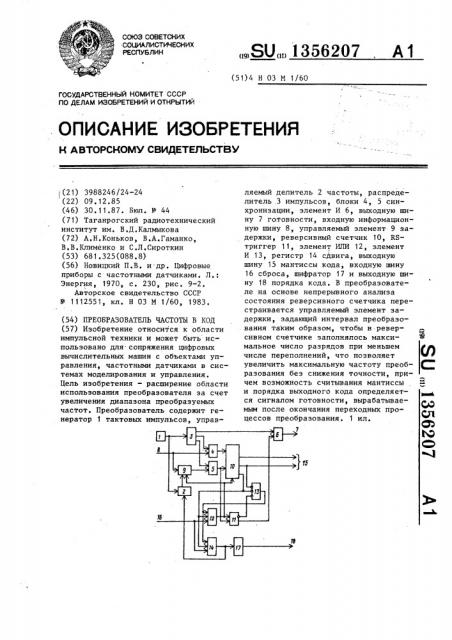

Изобретение относится к области импульсной техники и может быть использовано для-сопряжения цифровых вычислительных машин с объектами управления , частотными датчиками в системах моделирования и управления. Цель изобретения - расширение области использования преобразователя за счет увеличения диапазона преобразуемых частот. Преобразователь содержит генератор 1 тактовых импульсов, управляемый делитель 2 частоты, распределитель .3 импульсов, блоки 4, 5 синхронизации , элемент И 6, выходную шину 7 готовности, входную информационную шину 8, управляемый элемент 9 задержки , реверсивный счетчик 10, RS- триггер 11, элемент ИЛИ 12, элемент И 13, регистр 14 сДвига, выходную шину 15 мантиссы кода, входную шину 16 сброса, шифратор 17 и выходную шину 18 порядка кода. В преобразователе на основе непрерывного анализа состояния реверсивного счетчика перестраивается управляемый элемент задержки , задаюш €й интервал преобразования таким образом, чтобы в реверсивном счетчике заполнялось максимальное число разрядов при меньшем числе переполнений, что позволяет увеличить максимальную частоту преобразования без снижения точности, причем возможность считывания мантиссы и порядка выходного кода определяется сигналом готовности, вырабатываемым после окончания переходных процессов преобразования. 1 ил. 5- $ (Л со сд О5 ю

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 4 Н 03 M 1/60

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

j(21) 3988246/24-24 (22) 09.12.85 (46) 30.11.87. Бюл. ¹ 44 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) А.Н.Коньков, В.А.Гаманко, В.В.Клименко и С.Л.Сироткин (53) 681.325(088.8) (56) Новицкий П.В. и.др. Цифровые приборы с частотными датчиками. Л.:

Энергия, 1970, с. 230, рис. 9-2.

Авторское свидетельство СССР № 1112551, кл. Н 03 М 1/60, 1983. (54) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД (57) Изобретение относится к области импульсной техники и может быть использовано для. сопряжения цифровых вычислительных машин с объектами управления, частотными датчиками в системах моделирования и управления, Цель изобретения — расширение области использования преобразователя за счет увеличения диапазона преобразуемых частот. Преобразователь содержит генератор 1 тактовых импульсов, управ„.SUÄÄ 1356207 А1 ляемый делитель 2 частоты, распределитель 3 импульсов, блоки 4, 5 синхронизации, элемент И 6, выходную шину 7 готовности, входную информационную шину 8, управляемый элемент 9 задержки, реверсивный счетчик 10, RSтриггер 11, элемент ИЛИ 12, элемент

И 13, регистр t4 сдвига, выходную шину 15 мантиссы кода, входную шину

16 сброса, шифратор 17 и выходную шину 18 порядка кода. В преобразователе на основе непрерывного анализа состояния реверсивного счетчика перестраивается управляемый элемент задержки, задающий интервал преобразо. вания таким образом, чтобы в реверсивном счетчике заполнялось максимальное число разрядов при меньшем числе переполнений, что позволяет увеличить максимальную частоту преобразования без снижения точности, причем возможность считывания мантиссы ф и порядка выходного кода определяется сигналом готовности, вырабатываемым после окончания переходных процессов преобразования. 1 ил.

13562

Изобретение относится к импульсной технике и может быть использовано для сопряжения цифровых вычислительных машин с объектами управления, частотными датчиками в системах мо5 делирования и управления.

Цель изобретения — расширение области использования за счет увеличения диапазона преобразуемых частот.

Преобразователь содержит генератор 1 тактовых импульсов, управляемый делитель 2 частоты, распределитель 3 импульсов, блоки 4 и 5 синхронизации, элемент И 6, выходную шину 7 готовности, входную информационную шину 8, управляемый элемент

9 задержки, реверсивный счетчик 10, RS-триггер 11, элемент ИЛИ 12, элемент И 13, регистр 14 сдвига, выходную шину 15 мантиссы кода, входную шину 16 сброса, шифратор 17 и выходную шину 18 порядка кода.

Преобразователь работает следующим образом. 25

Перед началом работы преобразователь устанавливается в исходное состояние подачей по шине 16 сигнала

"Сброс". При этом через элемент ИЛИ

12 устанавливается в ноль триггер 11, ЗО счетчик 10, элемент 9 задержки и все разряды регистра 14, кроме среднего.

По шине 8 на второй вход первого блока 4 синхронизации и информационный вход элемента 9 задержки поступают импульсы входной частоты. Блоки

4 и 5 синхронизируют и разносят во времени моменты поступления импульсов входной частоты на суммирующий и вычитающий входы счетчика 10. На сум40 мирующий вход счетчика 10 импульсы начинают поступать сразу после подачи входной частоты по шине 8, а на вычитающий вход — спустя время, определяемое задержкой элемента 9. Первым импульсом с выхода блока 5 устанав45 ливается в единицу триггер 11, нулевой потенциал с инверсного выхода которого открывает элемент И 13, а сигналом с прямого выхода открывается элемент И 6, За время, прошедшее между появлением первых импульсов на суммирующем и вычитающем входах счетчика 10, в счетчике накопится число, прямо пропорциональное значению входной частоты. При неизменной вход- 55 ной частоте на шине 8 код в счетчике будет также неизменным с точностью до младшего разряда. Это объясняется

07 2 поочередным поступлением импульсов на вычитающий и суммирующий входы счетчика 10. При изменении входной частоты пропорционально измейится содержимое счетчика 10 эа счет„инерционности управляемого элемента задержки, Начальное значение задержки определяется частотой импульсов, поступающих с выхода делителя 2 частоты. При этом коэффициент деления определяется кодом, хранимым в регистре 14. Указанное справедливо при отсутствии переполнения счетчика 10 и при наличии хотя бьi одного из mcrapших установленного в единицу разряда счетчика, т.е. первая значащая цифра отлична от нуля. При переполнении счетчика 10 на его выходе появляется сигнал, который через элемент ИЛИ 12 сбрасывает триггер 11, обнуляет счетчик 10, элемент задержки и сдвигает содержимое регистра 14 на m разрядов вправо (в сторону младших разрядов).

При этом коэффициент деления делителя 2 частоты уменьшается в К= 2 раз, а частота импульсов на управляющем входе элемента 9 задержки увеличивается в К раз. Преобразователь продолжает работать так, как после подачи сигнала "Сброс" по шине 16. Такой итерационный процесс продолжается до тех пор, пока старший разряд счетчика не станет равным нулю. При этом сигнал "Готовность" на шине 7 еще не появляется. Если в результате счета импульсов входной частоты первая значащая цифра (m разряды) равна нулю, то срабатывает элемент И 13, анализирующий равенство нулю m разрядов счетчика 10. Через элемент ИЛИ 12 сбрасывается триггер 11, счетчик 10, обнуляется цифровая линия 9 задержки и производится сдвиг содержимого регистра 14 на ш разрядов влево (в сторону старших разрядов). При этом коэффициент деления делителя 2 частоты увеличивается в К раз, частота импульсов на управляющем входе цифровой линии 9 задержки уменьшается в К раз, следовательно, в К раз увеличивается величина задержки.

Такой процесс продолжается до тех пор, пока первая значащая цифра не станет отличной от нуля.

Мантисса кода снимается с шины 15, а код порядка — с выхода шифратора

17 в ниде дополнительного двоичного кода. Сигналом об окончании преобра20

Рг

Lp= (2 — 1) — — — — — 1, 2 F « где n — разрядность мантиссы входного кода, бит, P — разрядность порядка выходно- 25 го кода, бит;

F — частота импульсов генератора

1, Гц.

Составитель З.Моисеенко

Техред А.Кравчук Корректор А.Обручар

Редактор А.Лежнина

Заказ 58 11/54 Тираж 900 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, .4

13562 зования и возможности считывания кода является сигнал "Готовность" на шине 7, который выдается после окончания всех переходных процессов в преобразователе по импульсу с третьего выхода распределителя 3 импульсов при наличии на первом входе элемента

И 6 единичного сигнала с выхода триггера 11. l0

Для обеспечения заданной точности преобразования частота импульсов на выходах распределителя 3 импульсов

Риакс где Fмак. — Максимальное значение 15 входноч частоты на шине 8.

Разрядность управляемого элемента

9 задержки определяется выражением:

Формула изобретения З0

Преобразователь частоты в код, содержащий реверсивный счетчик, распределитель импульсов, первый и второй выходы которого соединены с первыми

35 входами первого и второго блоков синхронизации соответственно, а вход соединен с выходом генератора тактовых импульсов, второй вход второго блока синхронизации соединен с выхо- 4 дом элемента задержки, элемент ИЛИ и два элемента И, о т л и ч а ю щ и йс я тем, что, с целью расширения области использования эа счет увеличения диапазона преобразуемых частот, 4 в него введены управляемый делитель частоты, регистр сдвига, шифратор и

RS-триггер, а элемент задержки выполнен управляемым, причем и информаци- . онных выходов реверсивного счетчика

07

4 являются выходной шиной мантиссы кода (где и — разрядность мантиссы выходного кода), выход переполнения соединен с первым инверсным входом первого элемента И, первым входом элемента ИЛИ и входом сдвига вправо регистра сдвига, суммирующий и вычитающий входы реверсивного счетчика соединены с выходами первого и второго блоков синхронизации соответственно, установочный вход объединен с R-входом RS-триггера и установочным входом управляемого элемента задержки и соединен с выходом элемента

ИЛИ, информационный вход управляемого элемента. задержки объединен с вторым входом первого блока синхронизации и является входной информационной шиной, а управляющие входы соединены с соответствующими выходами управляемого делителя частоты, информационный вход которого соединен с выходом генератора тактовых импульсов, а управляющие входы объединены с соответствующими входами шифратора и соединены с соответствующими выходами регистра сдвига, установочный вход которого объединен с вторым входом элемента ИЛИ и является входной шиной сброса преобразователя, а вход сдвига влево объединен с третьим входом элемента ИЛИ и соединен с выходом первого элемента И, вторые инверсные входы которого соединены с ш выходами старших разрядов из и информационных выходов реверсивного счетчика (m = log К, где К вЂ” основание используемой системы счисления), а третий инверсный вход соединен с инверсным выходом RS-триггера, Sвход которого соединен с выходом второго блока синхронизации, а прямой выход соединен с первым входом второго элемента И, второй вход которого соединен с третьим выходом распре,делителя импульсов, а выход является

;,выходной шиной готовности преобразо, вателя, выходы шифратора являются выходной шиной порядка кода.