Устройство для вычисления выражения @

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для использования в системах цифровой обработки информации в реальном масштабе времени. Цель изобретения - повышение быстродействия за счет 00 ел о со фиг J

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) А1 (б11 4 G 06 F 7/544

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

C е

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ, (21) 3986714/24-24 (22) 04. 12. 85 (46) 07.12,87.Вюл. № 45 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) И.M.Êðèâoðó÷êo, К.Г.Иваненко и В.В.Карпенко (53) 681,325(088,8) ,(56) Авторское свидетельство СССР

¹ 1320804, кл, G 06 F 7/544,05 ° 06.85.

Авторское свидетельство СССР

¹ 1180883, кл. G 06 F 7/544, 1984. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ВЫРАЖЕНИЯ ВИДА б1 -1 у = .> а . х.

< — iwk-j 1

j=1 (57) Изобретение относится к вычислительной технике и предназначено для использования в системах цифровой обработки информации в реальном масштабе времени. Цель изобретения— повышение быстродействия за счет! бk--1

У;1= а1,„, х;

Jef где у — значения элементов преобра !

It зованного массива, х; — значения элементов исходного массива, а„ „Я 1-1,0,1) — значения коэффициентов, k — число коэффициентов, i, q

Ф обеспечения вычисления всего выходного массива:

1357949

i 2 k — индексы элементов массивов. С этой целью устройство, содержащее триггер 1, элементы И 2, 3, группу элементов И 5, регистры 6-8, счетчик 9, дешифратор 10, группу умножителей 11 и группу сумматоров 12, содержит сумматор 4. Введение сумматора 4 и изменение связей в устройстве позволяет вычислять выхоцной массив (у, ) за один такт работы устройства, 2 ил.

Изобретение относится к вычислительной технике и предназначено для использования в системах цифровой обработки информации в реальном масш5 табе времени.

Цель изобретения — повышение быстродействия за счет обеспечения параллельного вычисления всего выходного массива jy; l0

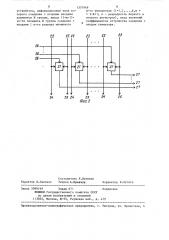

На фиг. 1 представлена !рункциональная .схема устройства; на фиг.2 вариант выполнения умножителя группы.

Устройство содержит триггер 1, элементы И 2 и 3, сумматор 4, группу элементов И 5, регистры 6-8, счетчик

9, дешифратор 10, группу умножителей 11 и группу сумматоров 12, входы

13-17 синхронизации, сброса, запуска, ввода коэффициентов и информацион- 20 ный устройства соответственно, выходы

18-20 признака сбоя, сопровождения данных и информационный устройства соответственно ° Умножители 21, входы 22 и 23 и выходы 24 и 25 положи- 25 тельного и отрицательного значений множителя соответственно, входы 26 значения множимого и выходы значения произведения.

Устройство работает следующим образом.

Подачей сигнала на вход 14 производится установка устройства в исходное состояние. При этом сбрасываются триггер 1, регистры 6-8 и счетчик 9. 3g

Затем вводятся коэффициенты а;,<.

При этом на вход 13 поступает импульс, по заднему фронту которого счетчик 9 устанавливается в состояние, равное единице. В результате на первом входе дешифратора 10 появляется. сигнал, поступающий на вход разрешения запи-, си регистра 7 °

В следующем такте по переднему фронту импульса, поступающего на вход

13, осуществляется запись в регистр

7 положительных значений коэффициентов, а по заднему фронту этого импульса счетчик 9 устанавливается в состояние, равное двум. В результате по сигналу с второго выхода дешифратора 10 разрешается запись в;»егистр

8 отрицательных значений коэффициентов, которые поступают в следующем такте на вход 16, синхронизируемых по переднему фронту импульса на входе 13, По заднему фронту этог» импульса счетчик 9 устанавливается в состояние, равное трем. Одновременно вектор отрицательных значений коэффициентов а;,> " поступает на сумматор 12, который осуществляет подсчет числа единиц, содержащих я в векторе отрицательных значений. Вычисленное значение с выхода cóììàòîpa 12 заносится в регистр 6 п» импульсу на входе 13.

Эта сумма используется для коррекции результата вычисления.

Если на этапе в ода на вход 16 поступают еще какие-либо данные, сопровождающиеся импульсом, то по заднему фронту импульса по входу 13 счетчик 9 устанавливается в с.»стояние, равное четырем, в результате чего на третьем выходе дешифратора 10 появляется признак сбоя устройства.

1357949 где у

1 f

В а;,k Е

<Ф -1

«. « -<

40 ения

«k-<

Если коэффициенты введены без сбоя, то по сигналу по входу 15 триггер 1 устанавливается в единичное состояние, открывая элементы И 5 и

5 второй элемент ИЗ. После этого на ,вход 17 поступает массив jx <) (Т векторов по и разрядов), синхронизируемый импульсом по входу 13. Векторы входного массива поступают на входы 10 соответствующих умножителей группы 11 по следующему правилу: выходы (1+

+ m-1) n-ro элемента И 5 соединены с входами 1 n-ro разряда множимого

m-го умножителя (1 = 1, 2,...,k; 15

m = I — k+1; n — разрядность вектора), т.е. на вход множимого первого умножителя 11 группы поступают значе.ния х,,,х„,„, на вход множимого второго умножителя группы 11 — х, 20 ...,х(„„),„, Hà (I — k + 1)-ro

X(3 <,.<) <), ° ° ° < Xdq

Если значение а = 1, то значе<+k-p ние х проходит через умножители

21 без изменения, если а;,д = О, 25 то на выходе умножителя 21 ноль, если a<+ „ = -1, то на выходе умнодителя 21 х (обратный код).

На сумматорах 12 образуется сумма у. = а,, х следующим об< (к-<)

1 =< разом.

Все положительные произведения а„ х поступают в прямом коде, все отрицательные — в обратном. Сумма числа единиц с выхода регистра 6 поступает на вход коррекции каждого сумматора группы 12.

На первом сумматоре 12 образуется сумма у„ = а„х,+ а„,х +...+

+ а< х„, на втором — у, = а„х +

+ а„,х, +...+ a,х„„, íà (I — k +

+ 1)-ом — у .„„), = а„х,„„+ а„,х „+

+...+ а<х . Все I — k + 1 сумм образуются одновременно и по заднему фронту сигнала сопровождения данных снимаются с выходов 20. По следующему импульсу, поступающему на вход 13, формируются значения у,,...,у<

50 и т.д.

Ф о р м у л а и з о б р е т

Устройство для вычисления выражения вида у = а „, ° х !

=< значения элементов преобразованного массива; значения элементов исходного массива, / (-1,0,11 — значения коэффициентов — число коэффициентов

i,q=1,2,...,k — индексы элементов массивов, содержащее триггер, два элемента И, три регистра, группу элементов И, группу умножителей, группу сумматоров, счетчик и дешифратор, первый и второй выходы которого соединены с входами записи первого и второго регистров соответственно, выходы которых соединены с входами положительного и отрицательного значений множителя соответственно умножителей группы, выходы значения произведения которых соединены с входами первого слагаемого соответствующих сумматоров группы, вход синхронизации устройства соединен с входами синхронизации первого и второго регистров и первыми входами первого и второго элементов И, вход сброса устройства соединен с входами сброса счетчика, первого, второго и третьего регистров и триггера, инверсный вход которого соединен с вторым входом первого элемента И, выход которого соединен с входом разрешения записи третьего регистра и счетным входом счетчика, выход которого соединен с входом дешифратора, третий .выход которого является выходом признака сбоя устройства, вход запуска которого соединен с входом установки триггера, прямой выход которого соединен с первыми входами элементов И группы и вторым входом второго элемента И, выход которого является выходом сопровождения данных устройства, вход коэффициентов которого соединен с информационными входами первого и второго регистров, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия за счет обеспечения параллельного вычисления всего выходного массива (у; ), оно содержит сумматор, выход которого соединен с информационным входом третьего регистра, выход которого соединен с входами второго слагаемого сумматоров группы, выходы которых образуют информационный выход 27 7 27

25 Г4 25

<Рог, Г

Составитель Н.Матвеек

Редактор Л.Лангазо Техред А.Кравчук

Корректор В.Бутяга

Заказ 5999/49 тираж 671

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 устройства, информационный вход которого соединен с вторыми входами элементов И группы, выход (1+m-1)»

«и-ro элемента И группы соединен с входами 1 n-ro разряда множимого

1357949

m-го умножителя (1=1,2,...,k,m =

= I-k+1", n — - разрядность первого и второго регистров), вход значений коэффициентов устройства соединен с входом сумматора.