Устройство управления организацией доступа к внешней памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам управления внешней полупроводниковой памятью большой емкости,.., тл. может быть использовано в системах обработки массивов данных, в системах обработки изображений и многомашинных комплексах, работающих с общим полем памяти. Цель изобретения - расширение области применения за счет увеличения объема подключаемой памяти. Устройство содержит приемник 1, регистр 2, арифметико-логический узел 3, мультиплексор 4, счетчик 5 битов.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (Н) А1 (50 4 0 06 F 12 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4013592/24-24 (22) 21.01.86 (46) 07.12.87. Бюл. № 45 (71) Научно-производственное объединение.| Импульс" им. XXV съезда КПСС (72) С. T. Галеев, А. В. Карачев, В. М. Костелянский, В, И. Песоцкий и Ю. И. Статылко (53) 681.325(088.8) ,(56) Авторское свидетельство СССР № 1198526, кл. G 06 F 12/00, 1980.

Лукьянов Д. А. "Электроника 256 К" эмулятор диска комплексов на основе микроЭВМ "Электроника "60 и ДВК:

Микропроцессорные средства и системы.

M.: 1986, ¹ 22, с. 62-65. (54) УСТРОЙСТВО УПРАВЛЕНИЯ ОРГАНИЗА- .

ЦИЕЙ ДОСТУПА К ВНЕШНЕЙ ПАМЯТИ (57) Изобретение относится к вычислительной технике, в частности к устройствам управления внешней полУпроводниковой памятью большой емкости, и может быть использовано в системах обработки массивов данных, в системах обработки изображений и многомашинных комплексах, работающих с общим полем памяти. Цель изобретения - расширение области применения за счет увеличения объема подключаемой памяти, Устройство содержит приемник 1, регистр

2, арифметико-логический узел 3, мультиплексор 4, счетчик 5 битов, !

357965 регистр 6, регистр 7, передатчик 8, блок 9 памяти, регистр 10, счетчик

ll адреса, формирователь 12 адреса внешней памяти, блок 13 микропрограммного управления, регистр 14, магистраль 16. Устройство используется для организации доступа к внешней полупроводниковой памяти большой емИзобретение относится к вычисли-. тельной технике, в частности к устройствам управления внешней полупроводниковой памятью большой емкости, и может быть использовано в сис" 5, темах обработки массивов данных, в системах обработки изображений и многомашинных комплексах, работающих с .общим полем памяти.

Цель изобретения — расширение области применения за счет увеличения объема подключаемой памяти„

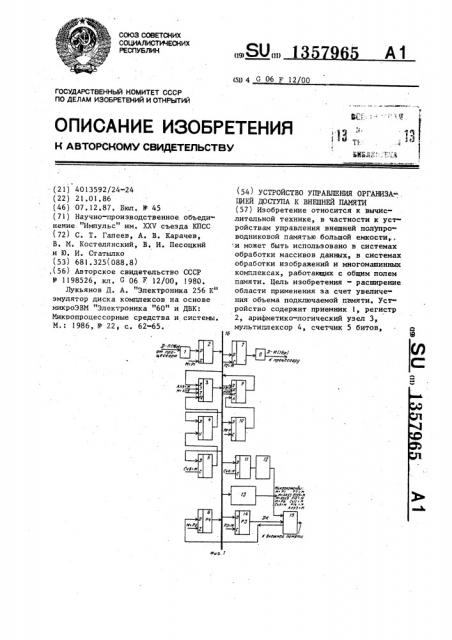

На фиг. 1 представлена структурная схема устройства; на фиг. 2—

15 структурная схема блока микропрограммного управления.

Устройство содержит приемник 1, регистр 2, арифметико-логический узел 3, мультиплексор 4, счетчик 5 битов, регистр 6, регистр 7, передат20 чик 8, блок 9 памяти, регистр 10, счетчик 11 адреса, формирователь 12 адреса внешней памяти, блок 13 микропрограммного управления, регистр 14, 25 блок 15 управления внешней памятью, магистраль 16.

Устройство обеспечивает следующие методы доступа к массивам данных внешней памяти:

О квантование данных; при использовании этого метода центральным процессором задаются следующие параметры: A — адрес начальный массива данных, 1 — общая длина массива, А„— величина пропусков между квантами массива; операции для этого метода доступа выполняются в следующем порядке: начиная с А производится чтение или запись части массива величиной А, затем адрес увеличивается, на величину А и продолжается чтением или записью следующей части массива величиной А„„ вся операция завершакости. Управление устройством осуществляется блоком 13 микропрограммного управления в зависимости от кода операции, формируемой процессором. Устройство обеспечивает несколько методов доступа к массивам данных, находящихся во внешней памяти, 2 ил. ется по исчерпанию общей длины массива; транспозиция данных; при использовании этого мегода центральным процессором задаются следующие параметры:

Ан, А, А . Операции для этого метода выполняются в следующем порядке: начиная с А, производится чтение или запись первого слова (байта), затем адрес увеличивается на величину Лд и читается или записывается второе слово (байт), затем адрес вновь увеличивается на величину А и читается или записывается третье слово, число таких шагов равно А ; после исчерпания Ац осуществляется возврат к адресу А +1 и цикл повторян ется с возвратом к адресу А +2, операция заканчивается после чтения или записи массива длиной (А„-А )+1; метод доступа с заданной последовательностью адресов; для этого метода необходимо задавать А„ и шаблон адресов"; "шаблон" представляет собой массив 128 слов (2048 бит), который записывается в блок 9 каждому адресу (начиная с A>), ставится в соответствие значения соответствующего бита массива "шаблона": единичное значение определяет необходимость выполнения операции над ячейкой с, данным адресом, нулевое — переход. к следующему адресу без выполнения операции, вся операция завершается по исчерпанию длины шаблона; метод доступа с заданной последовательностью даннь х; для этого метода необходимо задавать Л„и "шаблон данных"; "шаблон" представляет собой массив « 128 слов (2048 бит) и записывается в блок 9 по единичному значению бита "шаблона", осуществляется зались в очередную ячейку, по нулево1357965 му — pàííûå игнорируются, текущий адрес формируется прибавлением единицы к предыдущему адресу после очередной записи; вся операция завершается по

5 исчерпанию длины "шаблона"; чтение под маской, предварительно в устройство управления загружается два слова маски (маска нулей и маска единиц); на каждое прочитанное сло- 10 во (байт) накладывается поочередно маска нулей и маска единиц, в разрядах, определенных единицами слов маски, записываются, соответственно, нули и единицы, остальные разряды не 15 изменяются; этот метод может использоваться совместно с методом квантования данных; чтение с инверсией; этот метод может использоваться совместно с мето- 20 дом квантования данных; чтение ортогональное; при этом методе из каждого считанного слова (байта) выделяется один указанный разряд, из выделенных битов формиру- 25 ется слово (байт) и выдается в центральный процессор; адреса для этого метода формируются прибавлением единицы к текущему адресу или методу квантования данных; 30 чтение с коньюкцией или диэъюнкцией двух массивов, оба массива находятся в внешней памяти; формирование адреса аналогично предыдущему методу; поиск по контексту по ключу с битовой или байтовой маской; предварительно в блок 9 необходимо записать

,контекст или ключи с масками, Взаимодействие всех элементов устройства осуществляется посредством 40 магистрали 16. Приемники 1, передатчик 8, регистр 2 и регистр 7 обеспечивают выход на внешний радиальный параллельный (16 разрядов) интерфейс: данные приемника (D-П), данные источ- 45 ника (D-И). С помощью счетчика 11 адреса и формирователя 12 адресная последовательность передается в блок

15 управления внешней памятью, Обмен данными с блоком 15 осуществляется с помощью регистров 6 и 14. Блок памяти емкостью 2К байт используется для хранения заданных последовательностей адресов, последовательностей данных, контекстов. Регистр 10 служит для хранения адреса блока 9. Формирование, адресов в соответствии с заданным методом доступа производится с помощью арифметико-логического узла 3, в регистры которого записываются принимаемые от центрального процессора параметры операции . А„, Aö, A, I, маски, ключи. С помощью счетчика 5 битов обеспечивается выполнение операций ортогональных чтения.

Общее управление элементами схемы осуществляется блоком 13 микропрограммного управления.

Арифметико-логический узел 3 может быть реализован на микросхеме, содержащей 16 регистров, в которые записываются параметры операций, содержащиеся в командах процессора, Команда процессора содержит до 15 слов.

Используют следующие регистры:

R1 - адрес текущий первого массива;

R2 — длина массива; R3 — величина приращения адреса первого массива (А ); R4 — величина пропуска адресов первого массива (А,); Н5 - маска единиц; Н6 — маска нулей; R7 — адрес текущий второго массива; R8 - величина приращения адреса второго массива (Ам); R9 — величина пропуска адреса второго массива (А„); R10 - Ац текущее первого массива; Rll — А текущее второго массива; R12 - код команды; R13 — константа 2; R14 - рабочий регистр; R15 - длина статистики; R16 — адрес статистики.

Например, чтобы выполнить операцию квантования данных, от процессора поступает пятисловная команда, содержащая код операции,.начальный адрес массива данных, длину массива А, А11, В арифметико-логическом узле 3 осуществляется хранение и обработка параметров, заданных в команде процессора.

Например, наращивание текущего адреса (+I +Ац или +А„), изменение длины массива и сравнение ее с. saданной длиной, осуществляется после каждого обращения к внешней памяти в операциях связанных с записью и чтением данных.

Включением общего питания устройства в регистр адреса микрокоманд блока 13 заносится нулевой адрес микропрограммы функционирования устройства управления. Первой включается микропрограмма начальной установки и перехода в исходное состояние. В исходном состоянии блок управления находится в режиме ожидания команд процессора.

5 135

Устройство функционирует следующим образом.

На вход регистра 2 устройства поступают команды процессора через приемник 1 . При микрокоманде M =Рl (магистрали и присвоить значение регистра 1), поступающей из блока 13 по радиальным связям, принятая команда процессора устанавливается на магист-. раль 16. По микрокоманде АУ-М команда процессора по информационному входу с магистрали 16 заносится в рабочие регистры арифметико-логического узла 3. Одновременно команда по магистрали поступает в блок 13 для анализа кода операции в команде, принятой от процессора.

Вслед за командой через приемник

1 от процессора поступают параметры операции: А„, Ац, А, I, ключи, маски, "шаблоны" в сочетании, определенном кодом операции. Параметры А, А

A, I, ключи и маски записываются в узел 3 по тому же пути, что и команды. "Шаблоны" записываются в блок 9 в следующем порядке, Через приемники

1 данные "шаблона" поступают в регистр 2. Текущий адрес внешней памяти, сформированный в узел 3 по микрокоманде блока 13 M-АЛУЗ магистрали

16 присвоить содержимое узла 3, устанавливается на магистраль 16. По микрокоманде 10 текущий адрес блока

9 с магистрали 16 заносится s регистр

10.,Затем по микрокоманде М-Р! данные "шаблона" из регистра 2 устанавливаются на магистраль 16 и.по микрокоманде ОЗУ9-М записываются в блок 9.

Данные в операциях записи во внеш нюю память с входа D-П через приемник 1, входной регистр 2 поступают на вход регистра 14 и по микрокоманде 14-М заносятся в регистр 14.

С выхода регистра 14 данные поступают через блок 15 для записи во внешнюю память. Текущий адрес внешней памяти формируется в узле 3 и поступает на вход счетчика 11 адреса и по микрокоманде Счll-М заносится в счетчик 11 адреса. С выхода последнего адрес через формирователь 12 поступает в блок 15.

Данные в операциях чтения из внешней памяти через блок 15 поступают в регистр 6 и по микрокоманде M-Р6 выдаются на магистраль 16. С последней данные поступают на вход регистра 7, 7965

55 по микрокоманде Р7-М записываются в него и через передатчики 8 выдаются в процессор, Для операций ортогонального чтения считанные внешней памяти данные через регистр 6 поступают на вход мультиплексора 4, в счетчик 5 битов предварительно записывается номер бита, подлежащего выделению, скоммутированный бит с выхода мультиплексора 4 поступает на вход сдвиговых регистроВ арифметико-логического узла 3 и сдвигается.

Операция повторяется до получения

16-разрядного слова, которое с выхода узла 3 через регистр 7 и передатчик 8 выдается в процессор.

Для операций поиска чтения под маской, чтения инверсного, чтения с дизъюнкцией чтения с коньюнкцией все данные из внешней памяти через. регистр

6 поступают в узел 3 по информационному входу. После соответствующих операций в арифметика-логическом узле 3 по микрокоманде АЛУЗ-М данные с выхода узла 3 поступают на магистраль 16 и через регистр 2 и передатчик 8 выдаются в процессор.

Формула

Устройство управления организацией доступа к внешней памяти, содержащее счетчик адреса, первый регистр, приемник, передатчик, выход приемника соединен с информационным входом первого регистра, выход приемника является первым информационным входом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет увеличения объема подключаемой памяти, в него введены четыре регистра, арифметико-логический узел, блок памяти, мультиплексор, счетчик битов, формирователь ад-.

1 реса внешней памяти, блок микропрограммного управления, причем выход первого регистра соединен с информационными входами арифметика-логического узла, второго и третьего регистров, счетчика битов, входом занесения команды блока микропрограммного управления, выход четвертого регистра соединен с информационными входами пятого регистра, мультиплексора, выход пятого регистра соединен с входом передатчика, выход которого является пеовым информационным выходом устрой7965

Составитель В. Бородин

Редактор М. Бланар Техред Л.Сердюкова Корректор М. Шароши

Заказ 6000/50

Тираж 671 Подписное

ВНИИЛИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., p. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

7 135 ства, выход арифметика-логического узла соединен с информационными входами блока памяти, счетчика адреса, информационный вход арифметико-.логического узла соединен с выходами блока памяти и четвертого регистра, выход третьего регистра соединен с адресным входом блока памяти, выход счетчика битов соединен .с управляющим входом мультиплексора, выход которого соединен с входом управления сдвигом арифметико-логического узла, выход счетчика адреса соединен с вхо- дом формирователя адреса внешней памяти, выход которого является адресным выходом устройства, выход второго регистра является вторым информационным выходом устройства, информационный вход четвертого регистра является вторым информационным входом устройства, первый выход блока микропрограммного управления соединен с входом сброса первого регистра, вход стробирования пятого регистра соеди5 нен с вторым выходом блока микропро. граммного управления, третий и четвертый выходы которого соединены с входами задания инструкций и управления состояниями выходов арифметико1О логического узла соответственно, пя.тый и шестой выходы блока микропрограммного управления соединены с входами записи и чтения блока памяти соответственно, выходы с седьмого по десятый блока микропрограммного управления соединены с входами стробирования второго и третьего регистров, счетчиков битов и адреса соответственно, одиннадцатый выход блока микро-

2О программного управления соединен с входом сброса четвертого регистра.